- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX6ULL pixel clock can't follow device tree setting ?

i.MX6ULL pixel clock can't follow device tree setting ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX6ULL pixel clock can't follow device tree setting ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We want to set i.MX6ULL output 800x600-60 VESA timing.

We use 4.1.15_1.1.0 BSP version

My device tree display timing is

display0: display {

bits-per-pixel = <16>;

bus-width = <24>;

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <40000000>;

hactive = <800>;

vactive = <600>;

hback-porch = <88>;

hfront-porch = <40>;

vback-porch = <23>;

vfront-porch = <1>;

hsync-len = <128>;

vsync-len = <4>;

de-active = <1>;

hsync-active = <1>;

vsync-active = <1>;

pixelclk-active = <0>;

};

};

};

and lcdif_sel is select pll5

I also check clock tree information.

pll5_bypass_src 1 1 24000000 0 0

pll5 1 1 649515096 0 0

pll5_bypass 1 1 649515096 0 0

pll5_video 1 1 649515096 0 0

pll5_post_div 1 1 324757548 0 0

pll5_video_div 1 1 324757548 0 0

lcdif_pre_sel 1 1 324757548 0 0

lcdif_pred 1 1 108252516 0 0

lcdif_podf 1 1 36084172 0 0

lcdif_pix 1 1 36084172 0 0

iomuxc 0 0 36084172 0 0

lcdif_sel 0 0 36084172 0 0

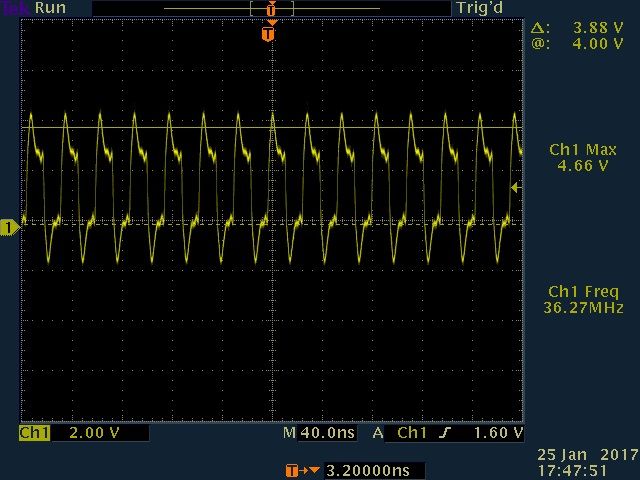

And We also check waveform from scope , clock is 36.27M

How to let lcdif_sel out 40MHz ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Appolo

one can try to set pll5 (which is currently = 649515096) to other frequency

so it could be divided to produce 40MHz. One can printf ccm registers

following Figure 18-2. Clock Tree i.MX6ULL RM

http://www.nxp.com/docs/en/reference-manual/IMX6ULLRM.pdf

Also may be useful try to change clock sources using example on

IMX6Q Device Tree Binding for ADV7343 Encoder

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

As I understand ,i.MX6Q/D/DL/SOLO can reference device tree "clock-frequency" to output currect pixel clock if we use pll5.

Does mxsfb.c don't reference "clock-frequency" ?

OR

If I need to setting VESA timing *640x480-60 ,800x600-60" , I need to add PLL5=fixed clock into C file ?