- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5777C EBI SRAM interface

MPC5777C EBI SRAM interface

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5777C EBI SRAM interface

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm working with MPC5777C in S32DS, I'm trying to interface SRAM (Flow through Burst) using EBI. Here i have initialized all the given EBI registers as per the reference manual. Still EBI is not generating any signals, all EBI pins are in pulled high state. I couldn't able to resolve the issue as there is no reference for EBI interface in S32DS.

Is there any component library or driver file for EBI(MPC5777C), or kindly provide any initialization steps for EBI.

Herewith attached my program.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

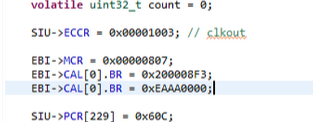

Hi, at first glance I see an error in your code, writing 2 times to the same register (it should be BR and OR registers). The values it indeed wrong.

Here you may find example code for external SRAM used on MPC5777CEVB (it uses GHS compiler, but all settings you can find in main file):

https://community.nxp.com/t5/MPC5xxx-Knowledge-Base/Example-MPC5777C-External-SRAM-test-GHS714/ta-p/...

Also pay attention to following bullettin, section 5:

https://community.nxp.com/t5/MPC5xxx-Knowledge-Base/External-Bus-Interface-FAQs/ta-p/1124068

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

#include "MPC5777C.h"

#include "stdio.h"

#define SDRAM_BASE 0x20000022

static void User_HW_init(void)

{

/* set round robin for all slaves */

XBAR->PORT[0].CRS = XBAR_CRS_ARB(1);

XBAR->PORT[1].CRS = XBAR_CRS_ARB(1);

XBAR->PORT[2].CRS = XBAR_CRS_ARB(1);

XBAR->PORT[3].CRS = XBAR_CRS_ARB(1);

XBAR->PORT[4].CRS = XBAR_CRS_ARB(1);

XBAR->PORT[6].CRS = XBAR_CRS_ARB(1);

XBAR->PORT[7].CRS = XBAR_CRS_ARB(1);

}

void External_SRAM_MMU_init(void)

{

__asm__("e_lis %r3,0x1002"); // Select TLB entry#, define R/W replacment control

__asm__("mtspr 624,%r3"); // Load MAS0 with 0x1002_0000 for TLB entry #2

__asm__("e_lis %r3,0xc000"); // setup 512MBytes to cover the whole EBI space

__asm__("e_or2i %r3,0x0980"); // TLB valid, protected from invalidation

__asm__("mtspr 625,%r3"); // Load MAS1 with 0xC000_0980 for TLB entry #2

__asm__("se_bgeni %r3,2"); // virtual address at 0x2000_0000

__asm__("e_ori %r3,%r3,0x0038"); // VLE, cache-inhibited, write through

__asm__("mtspr 626,%r3"); // Load MAS2 with 0x2000_0038 for TLB entry #2

__asm__("se_bgeni %r3,2"); // physical address at 0x2000_0000

__asm__("e_ori %r3,%r3,0x003f"); // all accesses permitted

__asm__("mtspr 627,%r3");

__asm__("msync"); // make sure we finished all memory accesses

__asm__("tlbwe"); // Write entry defined in MAS0 (entry #2 here) to MMU TLB

__asm__("se_isync"); // Wait for tlbwe to complete, then flush instruction buffer

}

static void External_SRAM_init(void)

{

volatile unsigned int count = 0;

/* Change EBI Physical Base Address to 0x2000_0000 */

External_SRAM_MMU_init();

/* CLKOUT Divide by 4 -> 33MHz */

SIU->ECCR = 0x00001003;

SIU->PCR[256] = 0x0443;

/* CS0 PCR 256 */

SIU->PCR[256] = 0x0443;

/* D_ADD_DAT31 PCR 257 */

SIU->PCR[257] = 0x0840;

/* D_ADD_DAT16 - 30 PCR 263 - 277 */

for (count = 263; count <= 277; count++)

{

SIU->PCR[count] = 0x0443;

};

/* D_ADD_DAT0 - 15 PCR 278 - 293 */

for (count = 278; count <= 293; count++)

{

SIU->PCR[count] = 0x0440;

};

/* D_RD_WR PCR 294 */

SIU->PCR[294] = 0x0443;

/* D_WE0 - D_WE1 PCR 295-296 */

SIU->PCR[295] = 0x0443;

SIU->PCR[296] = 0x0443;

/* D_OE PCR 297 */

SIU->PCR[297] = 0x0443;

/* D_TS PCR 298 */

SIU->PCR[298] = 0x0443;

/* D_ALE PCR 299 */

SIU->PCR[299] = 0x0443;

/* D_TA PCR 300 */

SIU->PCR[300] = 0x0443;

/* D_CS1 PCR 301 */

SIU->PCR[301] = 0x0443;

/* D_BDIP PCR 302 */

SIU->PCR[302] = 0x0443;

// SIU->PCR[307] = 0x0443;

/* D_WE2 - D_WE3 PCR 303 - 304 */

SIU->PCR[303] = 0x0443;

SIU->PCR[304] = 0x0443;

/* D_ADD9 - D_ADD11 PCR 305 - 307 */

for (count = 305; count <= 307; count++)

{

SIU->PCR[count] = 0x443;

};

/* D_ADD12 - D_ADD15 PCR 259 - 262 */

for (count = 259; count <= 262; count++)

{

SIU->PCR[count] = 0x0443;

};

/* Base Address: 0x20000000, 16-bit, non-Mux'd bus */

EBI->CAL[0].BR = 0x20000001; //burst access

/* Address Mask: 512KBytes, Zero Wait States - Flow-Through Sync SRAM */

//EBI->CAL[0].OR = 0xfff80012;

/* Address Mask: 512KBytes, One Wait States - Pipelined Sync SRAM */

EBI->CAL[0].OR = 0xFFF80010;

/* MCR - 32-bit mode */

EBI->MCR = 0x00000801;

}

/*!

\brief The main function for the project.

\details The startup initialization sequence is the following:

* - startup asm routine

* - main()

*/

int main(void)

{

/* Write your local variable definition here */

int i = 0;

volatile uint32_t *sdram = (uint32_t*)SDRAM_BASE;

/*** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!! ***/

#ifdef PEX_RTOS_INIT

PEX_RTOS_INIT(); /* Initialization of the selected RTOS. Macro is defined by the RTOS component. */

#endif

/*** End of Processor Expert internal initialization. ***/

/* Write your code here */

CLOCK_SYS_Init(g_clockManConfigsArr, CLOCK_MANAGER_CONFIG_CNT,

g_clockManCallbacksArr, CLOCK_MANAGER_CALLBACK_CNT);

CLOCK_SYS_UpdateConfiguration(0U, CLOCK_MANAGER_POLICY_FORCIBLE);

User_HW_init();

External_SRAM_init();

for(;;)

{

*sdram = (uint32_t)0x1234;

}

}Thanks for your reply.

Yes, later I changed the register configuration now I'm able to write in SRAM.

But, when i tried to write in a particular location data is being written in all locations.

And also unable to write data in Muxed 32 or 16 bit.

refer the following attachments.

thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which is used memory? Your connection? If it is flow through, as you said, you should use zero wait state (commented out in the code)

If you see the same value in all fields, in indicates an issue with addressing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

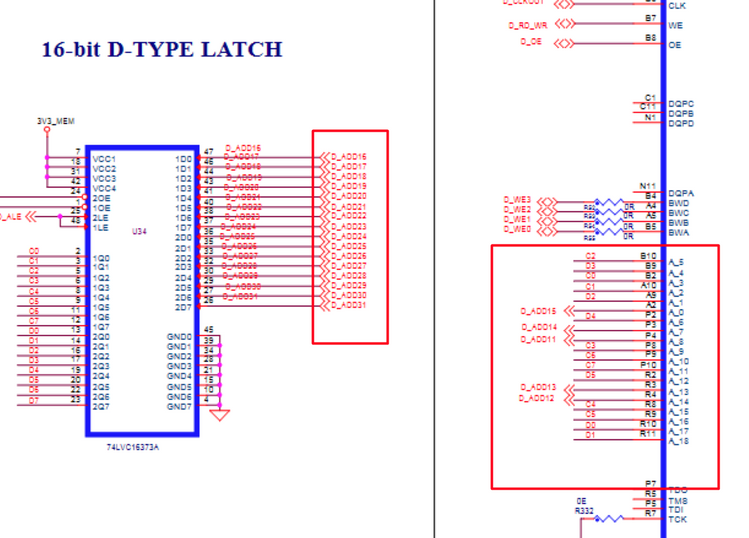

Memory I'm using is CY7C1471BV33-133BZI (cypress). Hardware connections are as it is in the uploaded schematic previously.

Yes, the memory is a flow through burst synchronous, also I used zero wait states configuration which is commented in the example program.

For addressing in SRAM there are 2 pins which is A0 and A1 field select and A(address) pins, I tried all the possible combinations, still data is being written in all the fields.

But in Muxed 32 and 16 bit data is not even written in single address. I didn't understand what I'm missing here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does this mean you only have connected five address lines? Why there is a latch device there, if unconnected? Please explain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As per my application I want to use 16 bit or 32 bit muxed mode. So, latch is used and also usage of latch is mentioned in datasheet. My major doubt is whether the connections are fine or else I need to do some changes.

In non mux mode I can able to write data but instead of being written in specific location, it is written in complete CS0 address range locations.

I'm only confused on the address pins connection. We did the connection same as evaluation board (MPC5777c daughter board). The only difference is SRAM which is interfaced CY7C1471BV33-133BZI for more memory.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You haven't answered my question.

On the screenshot it seems on the memory side only address lines A_0, A_7, A_8, A_13, A_14 are connected what's wrong, of course, if it is so.