- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MCX Microcontrollers

- :

- Re: Cannot halt processor with EXT oscillator mode

Cannot halt processor with EXT oscillator mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Cannot halt processor with EXT oscillator mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

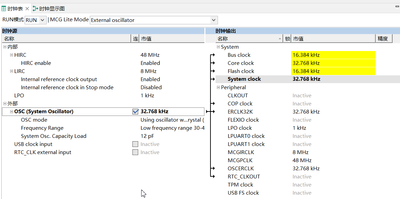

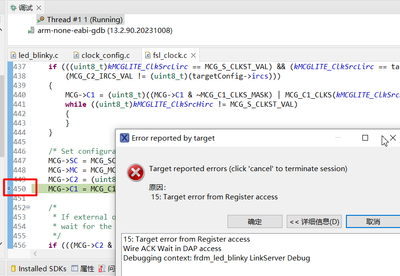

It is failed to set break point when debugging with following MCG configuration.

It run well without debugging.

const mcglite_config_t mcgliteConfig_BOARD_BootClockRUN =

{

.outsrc=kMCGLITE_ClkSrcExt, /* MCGOUTCLK source is external clock source */

.irclkEnableMode = MCG_IRCLK_DISABLE, /* MCGIRCLK disabled */

.ircs = kMCGLITE_Lirc8M, /* Slow internal reference (LIRC) 8 MHz clock selected */

.fcrdiv = kMCGLITE_LircDivBy1, /* Low-frequency Internal Reference Clock Divider: divided by 1 */

.lircDiv2 = kMCGLITE_LircDivBy1, /* Second Low-frequency Internal Reference Clock Divider: divided by 1 */

.hircEnableInNotHircMode = false, /* HIRC source is not enabled */

};

Error report

My board is FRDM-MCXC242.

How to deal with the problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @limit1995

Could you please show me where you set the breakpoint? And which demo did you use? I will help to check on my side. Thank you.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @Alice_Yang

I set the clock configuration based on demo app led_blinky.

Then update the source files.

And step-by-step dubugging caused error like below.

The part of the automatically generated clock_config.c is as follows:

void BOARD_InitBootClocks(void)

{

BOARD_BootClockRUN();

}

/*******************************************************************************

********************** Configuration BOARD_BootClockRUN ***********************

******************************************************************************/

/* clang-format off */

/* TEXT BELOW IS USED AS SETTING FOR TOOLS *************************************

!!Configuration

name: BOARD_BootClockRUN

called_from_default_init: true

outputs:

- {id: Bus_clock.outFreq, value: 16.384 kHz}

- {id: Core_clock.outFreq, value: 32.768 kHz}

- {id: ERCLK32K.outFreq, value: 32.768 kHz}

- {id: Flash_clock.outFreq, value: 16.384 kHz}

- {id: LPO_clock.outFreq, value: 1 kHz}

- {id: MCGIRCLK.outFreq, value: 8 MHz}

- {id: MCGPCLK.outFreq, value: 48 MHz}

- {id: OSCERCLK.outFreq, value: 32.768 kHz}

- {id: System_clock.outFreq, value: 32.768 kHz}

settings:

- {id: MCGMode, value: EXT}

- {id: MCG.CLKS.sel, value: SIM.OSCCLK}

- {id: MCG_C2_OSC_MODE_CFG, value: ModeOscLowPower}

- {id: MCG_MC_HIRCEN_CFG, value: Enabled}

- {id: OSC0_CR_ERCLKEN_CFG, value: Enabled}

- {id: OSC_CR_ERCLKEN_CFG, value: Enabled}

- {id: OSC_CR_SYS_OSC_CAP_LOAD_CFG, value: SC12PF}

- {id: SIM.CLKOUTSEL.sel, value: MCG.MCGPCLK}

- {id: SIM.COPCLKSEL.sel, value: OSC.OSCERCLK}

- {id: SIM.FLEXIOSRCSEL.sel, value: MCG.MCGPCLK}

- {id: SIM.LPUART0SRCSEL.sel, value: MCG.MCGPCLK}

- {id: SIM.LPUART1SRCSEL.sel, value: MCG.MCGPCLK}

- {id: SIM.RTCCLKOUTSEL.sel, value: OSC.OSCERCLK}

- {id: SIM.TPMSRCSEL.sel, value: MCG.MCGPCLK}

- {id: SIM.USBSRCSEL.sel, value: MCG.MCGPCLK}

sources:

- {id: MCG.HIRC.outFreq, value: 48 MHz}

- {id: OSC.OSC.outFreq, value: 32.768 kHz, enabled: true}

* BE CAREFUL MODIFYING THIS COMMENT - IT IS YAML SETTINGS FOR TOOLS **********/

/* clang-format on */

/*******************************************************************************

* Variables for BOARD_BootClockRUN configuration

******************************************************************************/

const mcglite_config_t mcgliteConfig_BOARD_BootClockRUN =

{

.outsrc=kMCGLITE_ClkSrcExt, /* MCGOUTCLK source is external clock source */

.irclkEnableMode = kMCGLITE_IrclkEnable, /* MCGIRCLK enabled, MCGIRCLK disabled in STOP mode */

.ircs = kMCGLITE_Lirc8M, /* Slow internal reference (LIRC) 8 MHz clock selected */

.fcrdiv = kMCGLITE_LircDivBy1, /* Low-frequency Internal Reference Clock Divider: divided by 1 */

.lircDiv2 = kMCGLITE_LircDivBy1, /* Second Low-frequency Internal Reference Clock Divider: divided by 1 */

.hircEnableInNotHircMode = true, /* HIRC source is enabled */

};

const sim_clock_config_t simConfig_BOARD_BootClockRUN =

{

.er32ksrc=SIM_OSC32KSEL_OSC32KCLK_CLK, /* OSC32KSEL select: OSC32KCLK clock */

.clkdiv1 = 0x10000U, /* SIM_CLKDIV1 - OUTDIV1: /1, OUTDIV4: /2 */

};

const osc_config_t oscConfig_BOARD_BootClockRUN =

{

.freq = 32768U, /* Oscillator frequency: 32768Hz */

.capLoad = (kOSC_Cap4P | kOSC_Cap8P), /* Oscillator capacity load: 12pF */

.workMode = kOSC_ModeOscLowPower, /* Oscillator low power */

.oscerConfig =

{

.enableMode = kOSC_ErClkEnable, /* Enable external reference clock, disable external reference clock in STOP mode */

}

};

/*******************************************************************************

* Code for BOARD_BootClockRUN configuration

******************************************************************************/

void BOARD_BootClockRUN(void)

{

/* Set the system clock dividers in SIM to safe value. */

CLOCK_SetSimSafeDivs();

/* Initializes OSC0 according to board configuration. */

CLOCK_InitOsc0(&oscConfig_BOARD_BootClockRUN);

CLOCK_SetXtal0Freq(oscConfig_BOARD_BootClockRUN.freq);

/* Set MCG to EXT mode. */

CLOCK_SetMcgliteConfig(&mcgliteConfig_BOARD_BootClockRUN);

/* Set the clock configuration in SIM module. */

CLOCK_SetSimConfig(&simConfig_BOARD_BootClockRUN);

/* Set SystemCoreClock variable. */

SystemCoreClock = BOARD_BOOTCLOCKRUN_CORE_CLOCK;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @limit1995

In MCG control register 1, it changes the clock source for the main clock. It cannot be debugged when the clock source is changed.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @Alice_Yang ,

It is ok to step-over BOARD_InitBootClocks() with HIRC mode.

But it is failed to step-over BOARD_InitBootClocks() or to set break point with EXT mode. Debugging is not possible at all.

Why?

And I want to know how to debug with EXT mode.

Thanks.