- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- MCUXpresso IDE

- :

- Re: Errore in download programma con MCUXpresso IDE

Errore in download programma con MCUXpresso IDE

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Buongiorno.

Sto provando a scaricare il programma "Hello World" fornito con l'SDK nella scheda MIMXRT1050-EVK.

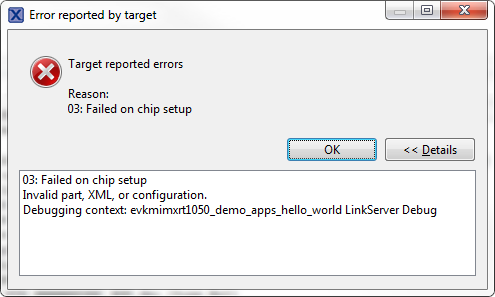

All'atto del download, però, ottengo sempre questo errore:

Ecco l'uscita della Console:

MCUXpresso RedlinkMulti Driver v10.1 (Nov 9 2017 16:45:39 - crt_emu_cm_redlink build 360)

Found chip XML file in E:/nxp/Workspace/evkmimxrt1050_demo_apps_hello_world/Debug\MIMXRT1052xxxxx.xml

Reconnected to existing redlink server (PID 4294967295)

Connecting to probe 1 core 0 (server PID unknown) gave 'OK'

Probe Firmware: DAPLink CMSIS-DAP (ARM)

Serial Number: 0227000041114e450030300dc40300535ab1000097969900

VID:PID: 0D28:0204

USB Path: \\?\hid#vid_0d28&pid_0204&mi_03#9&29aa56e6&0&0000#{4d1e55b2-f16f-11cf-88cb-001111000030}

debug interface type = <unknown> (DAP DP ID 0BD11477) over SWD

processor type = Cortex-M7 (CPU ID 410FC270)

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 0BD11477. CpuID: 410FC270. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM dev (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM dev (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM dev (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C ChipIP dev SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 ChipIP dev DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E ChipIP dev (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 ChipIP dev ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 ARCH 23B:4A13r0 CoreSight dev type 0x13 Trace Source - core

ROM 2 E0042000: CID B105900D PID 04004BB906 CoreSight dev type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BB9A9 CoreSight dev type 0x11 Trace Sink - TPIU

ROM 1 E0043000: CID B105F00D PID 04001BB101 System dev (type 0x0)

CM7 Rev. 0.0 DTCM: 512KB ITCM: 512KB

LoUU: Level 2: LoC: Level 2

Level 1 Cache Type: Instruction+Data

ICache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 512 Assoc: 2 LineSize: 8

DCache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 256 Assoc: 4 LineSize: 8

failed to find a target memory area to use to test the Debug Access Port

required information about vendor NXP chip MIMXRT1052xxxxx not found

Failed on chip setup: Ec(01). Invalid part, XML, or configuration.

error closing down debug session - Ee(FF). Redlink interface error 255.

La versione di MCUXpresso-IDE è questa:

MCUXpresso IDE v10.1.0 [Build 589] [2017-11-14]

Potreste darmi un aiuto?

Grazie.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have a theory as to what the cause of your problems may be.

Please can you follow the process to mass erase the Hyperflash that is detailed in the Troubleshooting section of Overview of using the MIMXRT1050-EVK with MCUXpresso IDE

After doing this, power the board down and then back up again. And then try debugging your project again. Does this then work?

Regards,

MCUXpresso IDE Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have a theory as to what the cause of your problems may be.

Please can you follow the process to mass erase the Hyperflash that is detailed in the Troubleshooting section of Overview of using the MIMXRT1050-EVK with MCUXpresso IDE

After doing this, power the board down and then back up again. And then try debugging your project again. Does this then work?

Regards,

MCUXpresso IDE Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

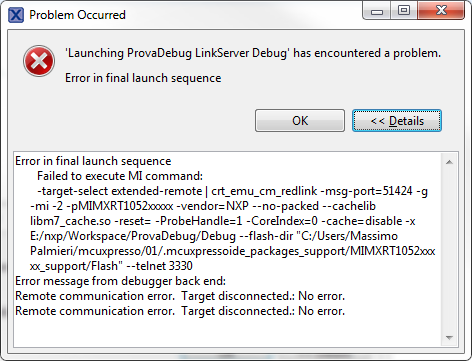

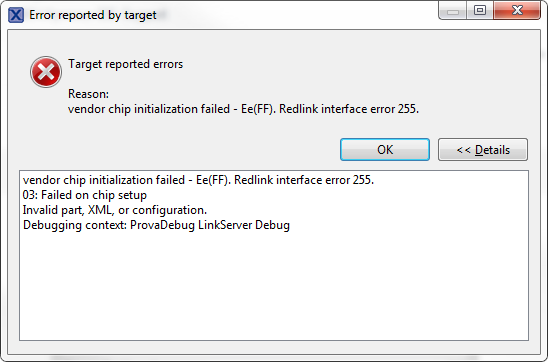

Following the instructions on the above document, i have created a new projects and inserted the preprocessor directive "XIP_EXTERNAL_FLASH". Then i compiled and launched debugger and these are the results:

Console window:

MCUXpresso RedlinkMulti Driver v10.1 (Nov 9 2017 16:45:39 - crt_emu_cm_redlink build 360)

Found chip XML file in E:/nxp/Workspace/ProvaDebug/Debug\MIMXRT1052xxxxx.xml

Reconnected to existing redlink server (PID 4294967295)

Connecting to probe 1 core 0 (server PID unknown) gave 'OK'

Probe Firmware: DAPLink CMSIS-DAP (ARM)

Serial Number: 0227000041114e450030300dc40300535ab1000097969900

VID:PID: 0D28:0204

USB Path: \\?\hid#vid_0d28&pid_0204&mi_03#9&29aa56e6&0&0000#{4d1e55b2-f16f-11cf-88cb-001111000030}

debug interface type = <unknown> (DAP DP ID 0BD11477) over SWD

processor type = Cortex-M7 (CPU ID 410FC270)

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 0BD11477. CpuID: 410FC270. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM dev (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM dev (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM dev (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C ChipIP dev SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 ChipIP dev DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E ChipIP dev (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 ChipIP dev ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 ARCH 23B:4A13r0 CoreSight dev type 0x13 Trace Source - core

ROM 2 E0042000: CID B105900D PID 04004BB906 CoreSight dev type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BB9A9 CoreSight dev type 0x11 Trace Sink - TPIU

ROM 1 E0043000: CID B105F00D PID 04001BB101 System dev (type 0x0)

CM7 Rev. 0.0 DTCM: 512KB ITCM: 512KB

LoUU: Level 2: LoC: Level 2

Level 1 Cache Type: Instruction+Data

ICache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 512 Assoc: 2 LineSize: 8

DCache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 256 Assoc: 4 LineSize: 8

Inspected v.2 External Flash Device on SPI using SPIFI lib MIMXRT1050-EVK_S26KS512S.cfx

Image 'MIMXRT1050-EVK_S26KS512SOct 19 2017 16:37:47'

Opening flash driver MIMXRT1050-EVK_S26KS512S.cfx

chip initialization failed - Ee(FF). Redlink interface error 255.

failed to find a target memory area to use to test the Debug Access Port

required information about vendor NXP chip MIMXRT1052xxxxx not found

Failed on chip setup: Ec(01). Invalid part, XML, or configuration.

error closing down debug session - Ee(FF). Redlink interface error 255.

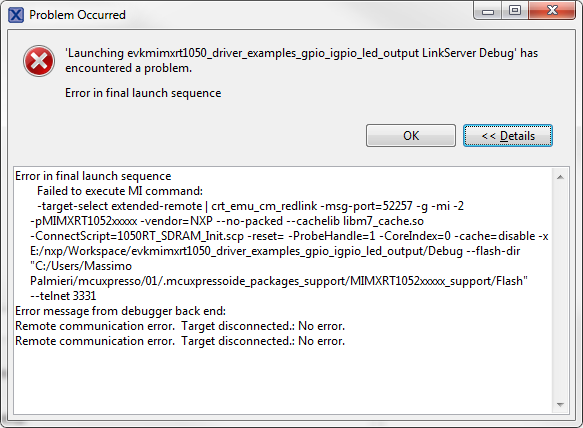

Then i have imported the led SDK example and added the SDRAM script. I launched the debugger and this is the result:

Console window

MCUXpresso RedlinkMulti Driver v10.1 (Nov 9 2017 16:45:39 - crt_emu_cm_redlink build 360)

Found chip XML file in E:/nxp/Workspace/evkmimxrt1050_driver_examples_gpio_igpio_led_output/Debug\MIMXRT1052xxxxx.xml

Reconnected to existing redlink server (PID 4294967295)

Connecting to probe 1 core 0 (server PID unknown) gave 'OK'

============= SCRIPT: 1050RT_SDRAM_Init.scp =============

Setup SDRAM

Clock Init Done

SDRAM Init Done

============= END SCRIPT ================================

Probe Firmware: DAPLink CMSIS-DAP (ARM)

Serial Number: 0227000041114e450030300dc40300535ab1000097969900

VID:PID: 0D28:0204

USB Path: \\?\hid#vid_0d28&pid_0204&mi_03#9&29aa56e6&0&0000#{4d1e55b2-f16f-11cf-88cb-001111000030}

debug interface type = <unknown> (DAP DP ID 0BD11477) over SWD

processor type = Cortex-M7 (CPU ID 410FC270)

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 0BD11477. CpuID: 410FC270. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM dev (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM dev (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM dev (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C ChipIP dev SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 ChipIP dev DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E ChipIP dev (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 ChipIP dev ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 ARCH 23B:4A13r0 CoreSight dev type 0x13 Trace Source - core

ROM 2 E0042000: CID B105900D PID 04004BB906 CoreSight dev type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BB9A9 CoreSight dev type 0x11 Trace Sink - TPIU

ROM 1 E0043000: CID B105F00D PID 04001BB101 System dev (type 0x0)

CM7 Rev. 0.0 DTCM: 512KB ITCM: 512KB

LoUU: Level 2: LoC: Level 2

Level 1 Cache Type: Instruction+Data

ICache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 512 Assoc: 2 LineSize: 8

DCache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 256 Assoc: 4 LineSize: 8

failed to find a target memory area to use to test the Debug Access Port

required information about vendor NXP chip MIMXRT1052xxxxx not found

Failed on chip setup: Ec(01). Invalid part, XML, or configuration.

error closing down debug session - Ee(FF). Redlink interface error 255.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

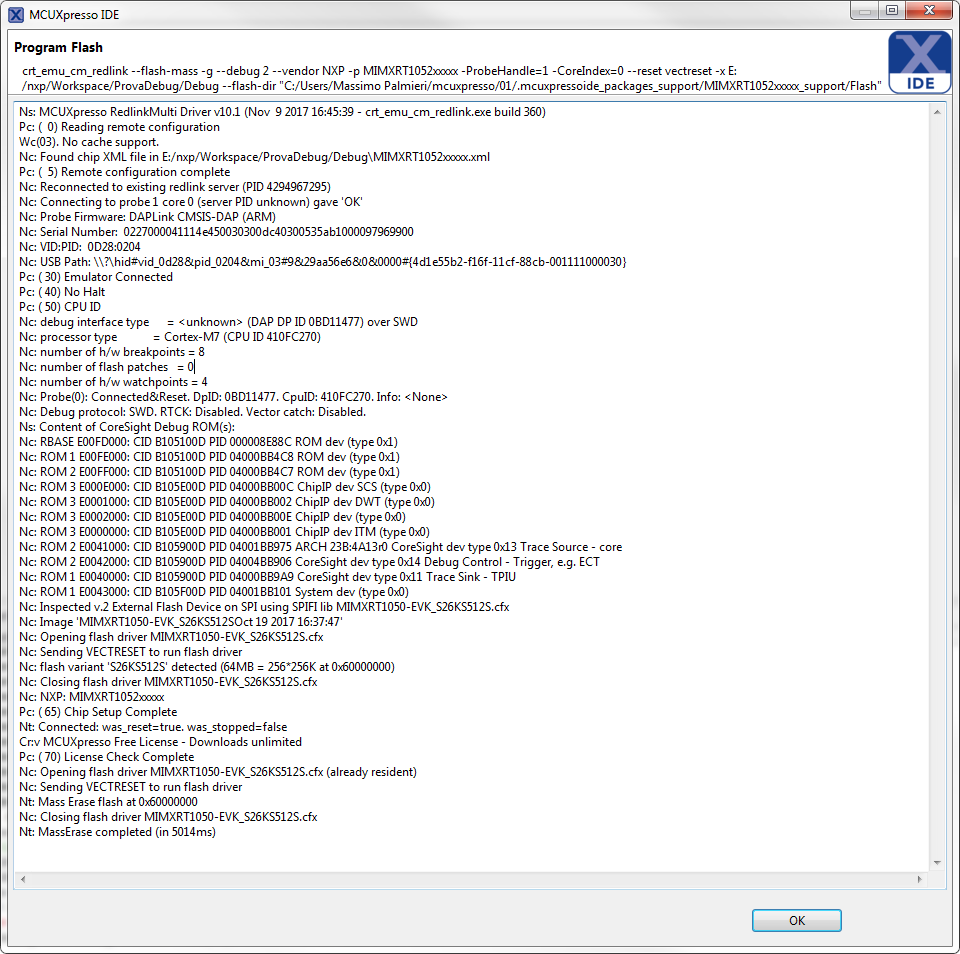

Now I have done the procedure to mass erase the hyper flash:

and now the debugger IS FUNTIONING.

I re-tried debugging in flash and in SDRAM and both are ok!

But it's right that to pass from an instruction and another the debugger takes several seconds? (almost 6 seconds)??

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Massimo,

Even I am also facing the same issue but I didn't get what procedure you have followed to solve the issue. It would be great if you could explain me. Is there any further setup in the hardware required? like, jumper or switch change?

Thank you,

Rakshith Rao.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

For using MCUXpresso IDE with the i.MX RT1050, please start off by going through the document available from : Overview of using the MIMXRT1050-EVK with MCUXpresso IDE

If you still have problems, please tell us exactly what you are doing and what you see.

Regards,

MCUXpresso IDE Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Massimo,

I am glad we have worked around this initial problem, but I am sorry you see this poor debug performance.

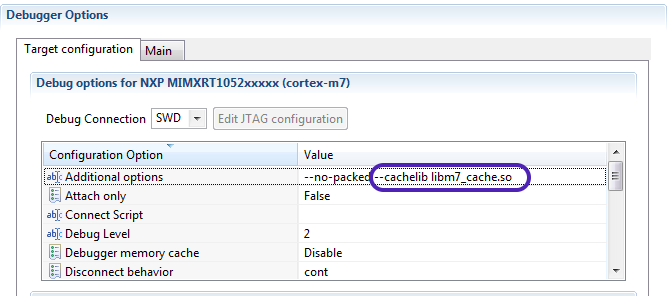

Regarding the debug performance - please can you try the following. Double click the launch configuration file and locate the entry shown below: delete this.

Now, please retry the debug operation and let us know if this resolved the performance issue you see.

Note: the debug probe on this part is not particularly fast. For improved performance, you might want to consider a higher performance debug probe such as NXP's LPC-Link2.

Yours,

MCUXpresso Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Ok, now it's all right! Thank you very much for your help!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Massismo,

I am sorry you are seeing these problems - let's try to sort things out. Firstly, we have created a document outlining various features and issues relating to the MIMXRT1050 that will hopefully be useful.

Overview of using the MIMXRT1050-EVK with MCUXpresso IDE

Please check the DAPLink Firmware section of this document to ensure you have the latest OpenSDA firmware installed!

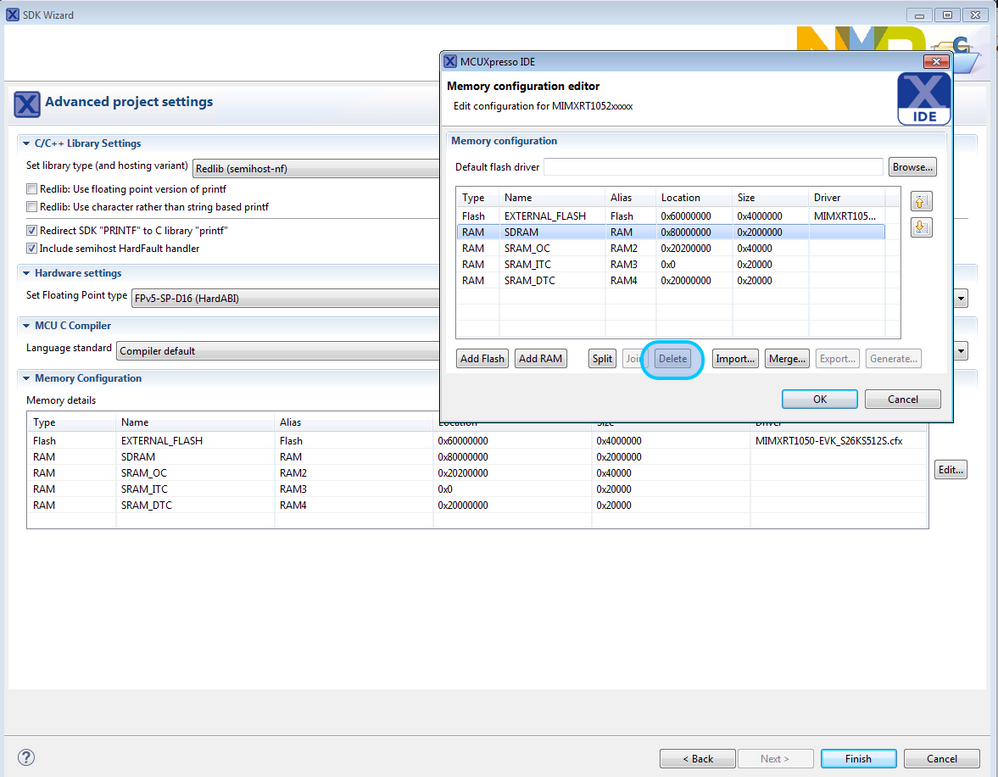

As previously mentioned, the error 'failed to find a target memory area to use to test the Debug Access Port' is key to the problems you are seeing. We are not able to duplicate this issue in our local testing, but the suspicion is that this might relate to an SDRAM access problem, so please may we suggest you try the following:

As described in the document above, create a new project using the New project wizard - but this time go to the second wizard screen and delete the SDRAM region.

Click 'OK' and Finish the project creation. This project will have no description of the SDRAM region and hence the debug world will attempt no access there.

Please try to debug this new project (via the OpenSDA debug connection) and let us know your results.

Yours,

MCUXpresso Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The debugger is attempting to discover an efficient way to access memory, but fails to read. Have you modified the memory configuration using the memory configuration dialog? If so, can you post the settings here?

Thanks and regards,

MCUXpresso Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the reply.

No, i haven't changed the memory configuration. These are the memory regions:

In Iar Embedde workbench, the memory definition in the .icf file for sdram_debug configuration is:

define symbol m_interrupts_start = 0x00000000;

define symbol m_interrupts_end = 0x000003FF;

define symbol m_text_start = 0x00000400;

define symbol m_text_end = 0x0001FFFF;

define symbol m_data_start = 0x20000000;

define symbol m_data_end = 0x2001FFFF;

define symbol m_data2_start = 0x20200000;

define symbol m_data2_end = 0x2023FFFF;

define symbol m_data3_start = 0x80000000;

define symbol m_data3_end = 0x81DFFFFF;

define symbol m_ncache_start = 0x81E00000;

define symbol m_ncache_end = 0x81FFFFFF;

/* Sizes */

if (isdefinedsymbol(__stack_size__)) {

define symbol __size_cstack__ = __stack_size__;

} else {

define symbol __size_cstack__ = 0x0400;

}

if (isdefinedsymbol(__heap_size__)) {

define symbol __size_heap__ = __heap_size__;

} else {

define symbol __size_heap__ = 0x0400;

}

define exported symbol __VECTOR_TABLE = m_interrupts_start;

define exported symbol __VECTOR_RAM = m_interrupts_start;

define exported symbol __RAM_VECTOR_TABLE_SIZE = 0x0;

define memory mem with size = 4G;

define region TEXT_region = mem:[from m_interrupts_start to m_interrupts_end]

| mem:[from m_text_start to m_text_end];

define region DATA_region = mem:[from m_data_start to m_data_end];

define region DATA2_region = mem:[from m_data2_start to m_data2_end];

define region DATA3_region = mem:[from m_data3_start to m_data3_end-__size_cstack__];

define region CSTACK_region = mem:[from m_data3_end-__size_cstack__+1 to m_data3_end];

define region NCACHE_region = mem:[from m_ncache_start to m_ncache_end];

define block CSTACK with alignment = 8, size = __size_cstack__ { };

define block HEAP with alignment = 8, size = __size_heap__ { };

define block RW { first readwrite, section m_usb_dma_init_data };

define block ZI with alignment = 32 { first zi, section m_usb_dma_noninit_data };

define block NCACHE_VAR with size = 0x200000 , alignment = 0x100000 { section NonCacheable , section NonCacheable.init };

initialize by copy { readwrite, section .textrw };

do not initialize { section .noinit };

place at address mem: m_interrupts_start { readonly section .intvec };

place in TEXT_region { readonly };

place in DATA3_region { block RW };

place in DATA3_region { block ZI };

place in DATA3_region { last block HEAP };

place in CSTACK_region { block CSTACK };

place in NCACHE_region { block NCACHE_VAR };

This configuration, if this is the problem, is functioning.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

First thing to check would be power. If you are not using a separate power supply and are trying to power via the OpenSDA debug probe, then make sure that you have a jumper on J1 connecting 1-2 on the middle pair of headers. Note: if this link is set correctly, the LED next to J1 will light green. If the LED is not lit, the MCU/board will not be powered correctly and debug will fail

And if you are powering in this manner, then I would suggest connecting via a powererd USB hub rather than relying on the power direct from your PC.

Regards,

MCUXpresso IDE Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your reply. The jumper config seems to be correct: the green led is lit.

Now I try to power the board via a 5V power supply and set J1 in 1-2 position. The led is light green but when I try to download the program i take this answer:

MCUXpresso RedlinkMulti Driver v10.1 (Nov 9 2017 16:45:39 - crt_emu_cm_redlink build 360)

Found chip XML file in E:/nxp/Workspace/evkmimxrt1050_demo_apps_hello_world/Debug\MIMXRT1052xxxxx.xml

Reconnected to existing redlink server (PID 4294967295)

Connecting to probe 1 core 0 (server PID unknown) gave 'OK'

Probe Firmware: DAPLink CMSIS-DAP (ARM)

Serial Number: 0227000041114e450030300dc40300535ab1000097969900

VID:PID: 0D28:0204

USB Path: \\?\hid#vid_0d28&pid_0204&mi_03#9&29aa56e6&0&0000#{4d1e55b2-f16f-11cf-88cb-001111000030}

debug interface type = <unknown> (DAP DP ID 0BD11477) over SWD

processor type = Cortex-M7 (CPU ID 410FC270)

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 0BD11477. CpuID: 410FC270. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM dev (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM dev (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM dev (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C ChipIP dev SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 ChipIP dev DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E ChipIP dev (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 ChipIP dev ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 ARCH 23B:4A13r0 CoreSight dev type 0x13 Trace Source - core

ROM 2 E0042000: CID B105900D PID 04004BB906 CoreSight dev type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BB9A9 CoreSight dev type 0x11 Trace Sink - TPIU

ROM 1 E0043000: CID B105F00D PID 04001BB101 System dev (type 0x0)

CM7 Rev. 0.0 DTCM: 512KB ITCM: 512KB

LoUU: Level 2: LoC: Level 2

Level 1 Cache Type: Instruction+Data

ICache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 512 Assoc: 2 LineSize: 8

DCache 32K: WT: Y WB: Y RA: Y WA: Y NumSets: 256 Assoc: 4 LineSize: 8

failed to find a target memory area to use to test the Debug Access Port

required information about vendor NXP chip MIMXRT1052xxxxx not found

Failed on chip setup: Ec(01). Invalid part, XML, or configuration.

error closing down debug session - Ee(FF). Redlink interface error 255.

That is the same as before.

I don't know if there is some configuration i miss in my IDE or in my board.

I need some help: I am new in working with this IDE.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As clarification, i try to download the same code with IAR development tool and it's all ok. But I prefer to work with MCUXpresso, if it is possible...

Thank you.