- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: Clock on I2S is not consistent

Clock on I2S is not consistent

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm using SDK 2.11 on an LPC5512 using MCUexpresso 11.5.1. I've got a TFA9879 hanging off an I2S bus that this chip is driving to play audio sourced from an SPI memory.

I've got it configured correctly (I think) and set up for 22050 Hz (or pretty close since you can't quite get there with this chip: see Solved: I2S clock not exact but doesn't matter - NXP Community)

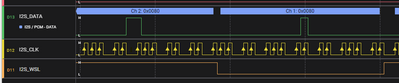

The problem I'm having is that the clock is not consistent:

When this clocks, it's clocking at 1MHz, not 700+KHz and then it's missing clocks every so often. The WSL line is pretty much correct in what it's doing overall so the basic clock rate is correct, just the instantaneous clock is not right. On this Audio part, it's saying that it has a PLL inside that is helping keep it synced to and compensating for the real clock rates but missing clocks isn't going to help that along much...

Got any idea of what is causing this behaviour?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

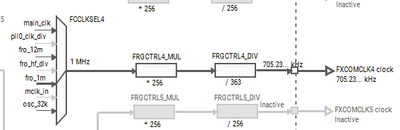

ref the diagram that I included here...

The Multiplier on FXCOMCLK4 doesn't want to be anything other than 256 in this tool and the divisor only goes up to 511 so I can't bring fro_12m into anything reasonable as a clock rate on that line.

However, my pll0 is running at 96MHz (derived from fro_12m) so I turned on pll0_clk_div and divided that down to 1Mhz and used that as input to FCCLKSEL4 to get me the same (sort of close) clock rate.

Didn't' change the odd clock stream at all.

HOWEVER: when I changed the divisor in FXCOMCLK4 to 256 (so that whole scale thing is 1) and then changed the pll0_clk_div to 136, I now get a good clock!

So somehow this FRGCTRL4 is hosing the output clock. No idea why but it really doesn't like to be set up how I set it up.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

the I2S sampling rate is 22.05KHz, the bit width in one slot is 16 bits, the bit clock is 22.05KHz*16*2=705.6KHz, you use FRG to get 705.6KHz from 1M internal clock, maybe it is the root cause for the discontinuous bit clock.

I suggest you use FRO12MHz, 12MHz/705.6KHz=17, you can set up the FRG divider as 1(set up the MULT to be 0), ans set up the I2S prescaler as 17, I suppose that the I2S bit clock will be continuous.

Pls have a try

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

ref the diagram that I included here...

The Multiplier on FXCOMCLK4 doesn't want to be anything other than 256 in this tool and the divisor only goes up to 511 so I can't bring fro_12m into anything reasonable as a clock rate on that line.

However, my pll0 is running at 96MHz (derived from fro_12m) so I turned on pll0_clk_div and divided that down to 1Mhz and used that as input to FCCLKSEL4 to get me the same (sort of close) clock rate.

Didn't' change the odd clock stream at all.

HOWEVER: when I changed the divisor in FXCOMCLK4 to 256 (so that whole scale thing is 1) and then changed the pll0_clk_div to 136, I now get a good clock!

So somehow this FRGCTRL4 is hosing the output clock. No idea why but it really doesn't like to be set up how I set it up.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

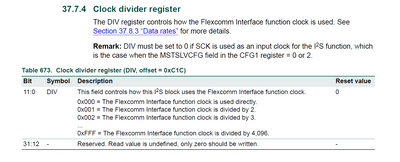

First of all, the DIV bits of FRG must be 0xFF or 256 as the following Remark.

Remark: To use the fractional baud rate generator, 0xFF must be wirtten to the DIV value

to yield a denominator vale of 256. All other values are not supported. See Section 34.3.1

“Configure the Flexcomm Interface clock and USART baud rate” and Section 34.7.2

“Clocking and baud rates”.

Secondly, there is a divider for the I2S driving clock, the FRG can generate the clock frequency for your application such as x*705.6KHz and set up the I2S divider as x and use the I2S divider to divide it to 705.6KHz.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This particular trace is from logic analyzer (Salea) , correct, at 16MS/s... I confirmed this with a scope because, as you note, logic analyzers aren't always truthful... I see the same behaviour in the scope trace.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Randy,

If you see the same behaviour on the scope, I think the bit clock has problem, it is inconsistent.

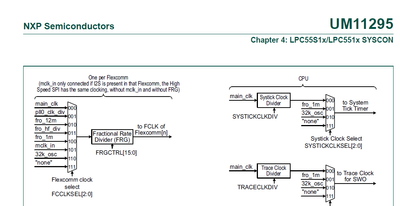

As the following fig, the bit clock is from the FCLKn, pls post the code to configure the FRG, the clock source of FRG so that we have a check.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Can you tell us the instrument name to display the I2S clock, data and frame signals? it appears that you use logic analyzer to display the signals, because of the limited logic analyzer sampling time, it has the issue.

Pls try to use oscilloscope to display the I2S signals instead of logic analyzer.

If you use oscilloscope, I am sorry.

BR

XiangJun Rong