- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- About mk22fn512 spi1/spi0 Transmission delay problem

About mk22fn512 spi1/spi0 Transmission delay problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

About mk22fn512 spi1/spi0 Transmission delay problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

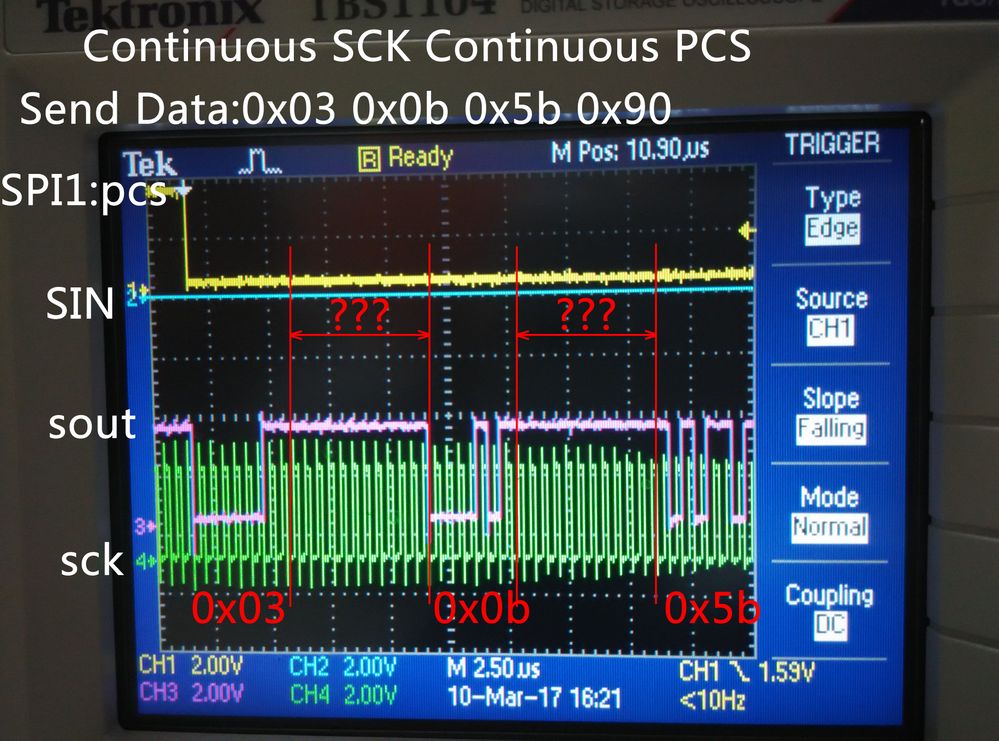

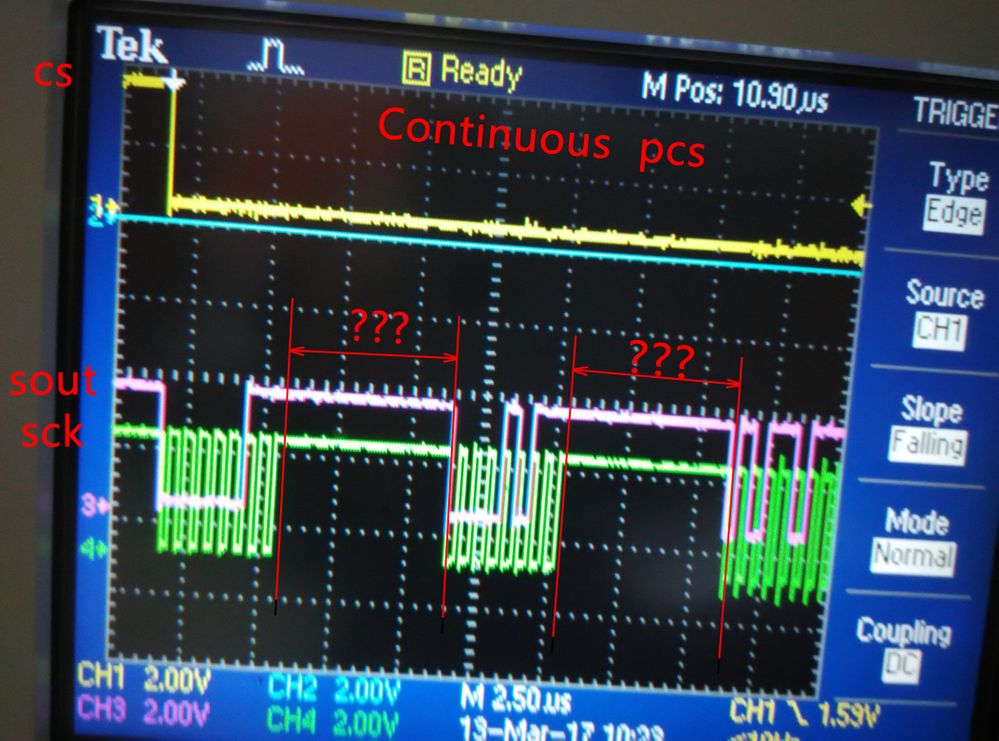

I am using mk22fn512 SPI1/SPI0 to send a series of data,Let SPI/SPI0 work in the loopback and continuous sck and continuous pcs mode.I found that when the SPI bus transmits data, each SOUT will have a certain delay after the completion of a single byte of data, which causes the slave device to be unable to determine the received data.

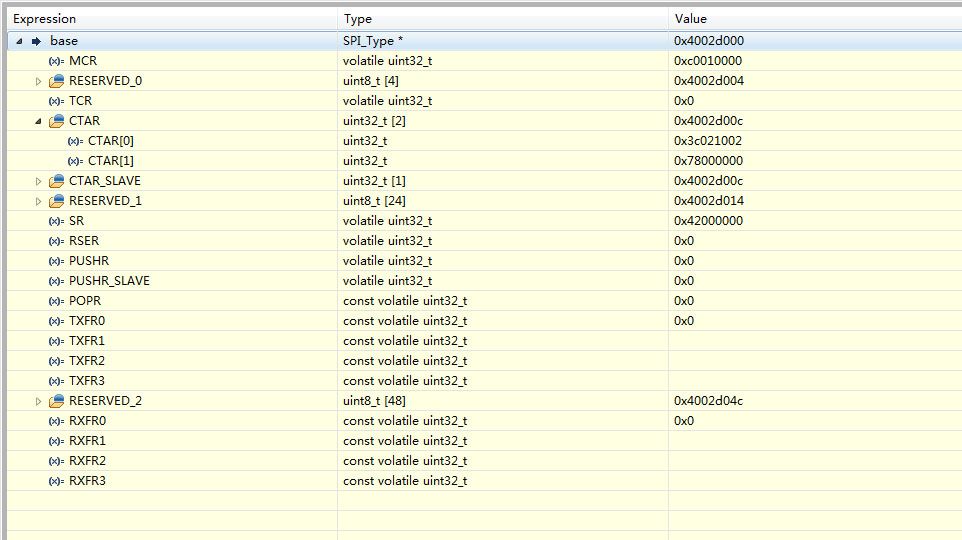

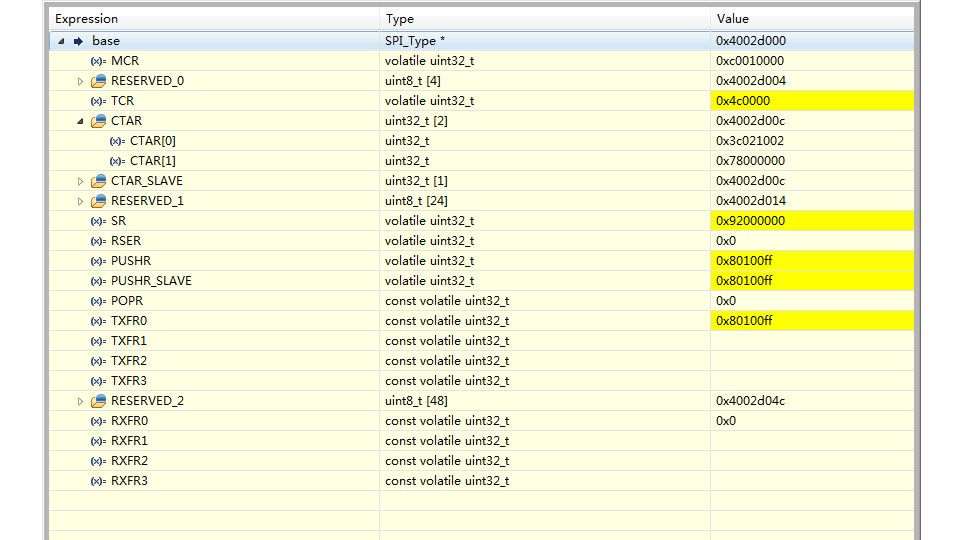

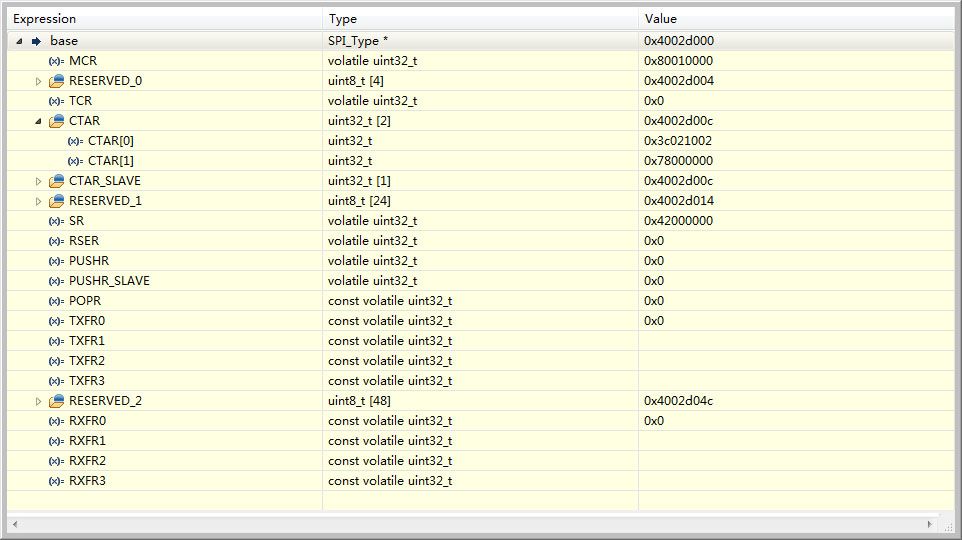

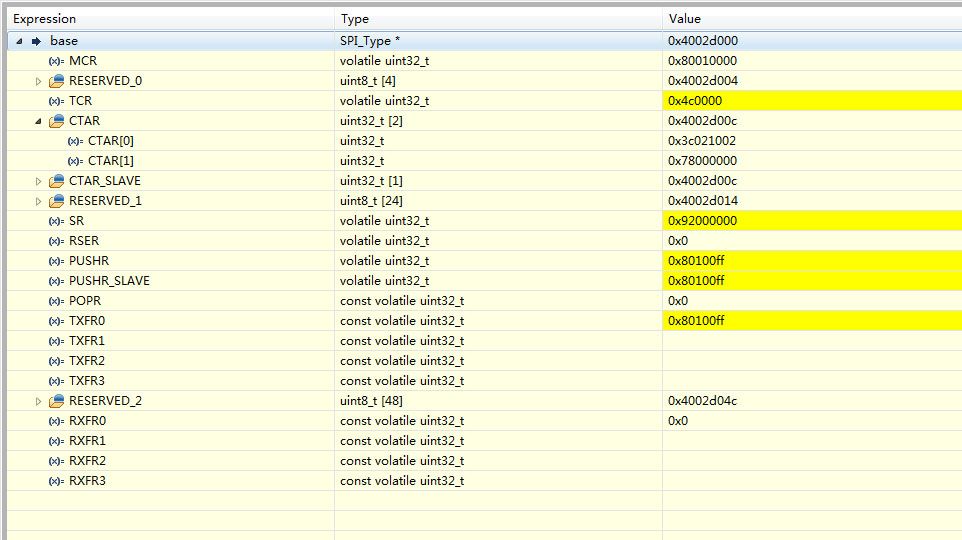

Register define

When I don't have a continuous sck mode, the waveform is below.

Continuous or discontinuous mode, SOUT does not have continuous output data. What is the reason?

Thanks and good luck!

Andy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you have any updated information on the issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The obvious answer is that your data-load code-sequence is unable to 'keep up' with the TX byte-rate. Slow your SPI clock, and/or clean up the code sequence. At BR=30 you've got 240 bus clocks per byte, or (presumably) 480 CPU clocks. Seems like a lot, but clocks are also easy to 'waste' ---- looks like you might be taking over twice that time?

You might also consider loading 16-bits per SPI transaction, rather than 8.

You will probably also have to make sure you are fully utilizing the SPI FIFOs so that the TX hardware always has a byte 'ready to go' on the very next SPI clock. If you wait for each 'TX complete' before even loading the 'next' you will surely skip a clock.

Can you capture your full sequence of 'PUSHR' values in a little debug-array, and show us that after a full message?