- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: imx8mq config dts(SPI)

imx8mq config dts(SPI)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

imx8mq config dts(SPI)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

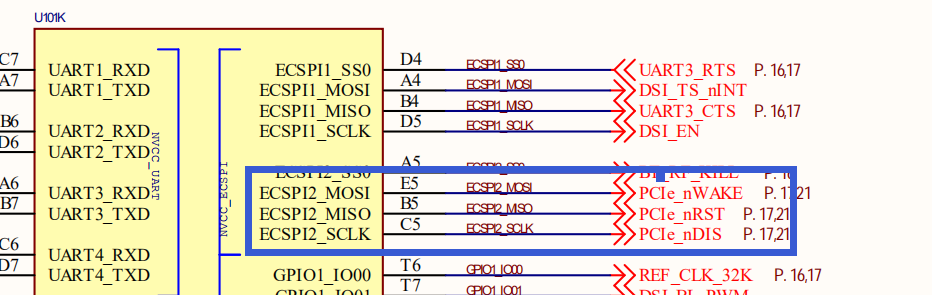

board:IMX8MQ-EVK

Bsp:4.14.78

I want to change the default routing for the next three pins by configuring the device tree.

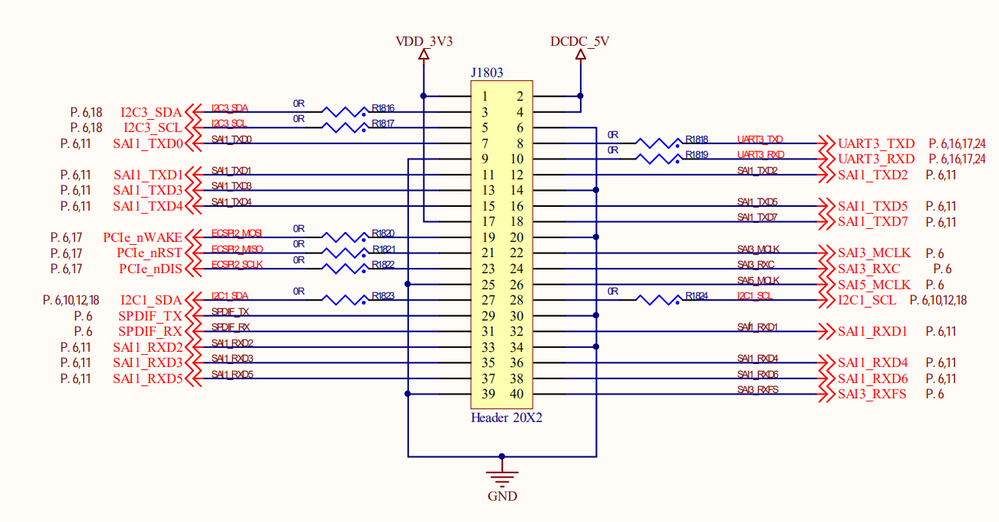

Because we now want to lead out 40 pins on the new board for users' independent development, including SPI,GPIO,UART,I2C device interface.

So,what I shound do through change dts.

Attached is the hardware schematic diagram of customer development board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello gaobo,

See below steps, please!

---------------------------------------

1. Remove these pins related to ECSPI2

pinctrl_pcie1: pcie1grp {

fsl,pins = <

MX8MQ_IOMUXC_I2C4_SDA_PCIE2_CLKREQ_B 0x76 /* open drain, pull up */

MX8MQ_IOMUXC_ECSPI2_SCLK_GPIO5_IO10 0x16

MX8MQ_IOMUXC_ECSPI2_MISO_GPIO5_IO12 0x16

>;

};

By default, on i.mx8mq-evk, above 2 pins are multiplexed as GPIO, both for PCIe port, so you should remove them, and then assign other 2 GPIOs for PCIe port if you also want to use PCIe.

2. Referring to eCSPI code in imx8mn-evk.dts, add ecspi of i.MX8MQ to your board dts.

Below is from imx8mn-evk.dts

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MN_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

MX8MN_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82

MX8MN_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82

>;

};

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MN_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x40000

>;

};

Change related pins to those of i.MX8MQ's, please! then add code to your dts for i.MX8MQ.

3. Adding eCPSI node like below.

Below is from imx8mn-evk.dts:

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>;

cs-gpios = <&gpio5 13 GPIO_ACTIVE_LOW>;

status = "okay";

/* code below is determined by what device is connected to eCSPI, change it to yours */

spidev0: spi@0 {

reg = <0>;

compatible = "rohm,dh2228fv";

spi-max-frequency = <500000>;

};

};

-------------------------------------------------------

OK, above 3 steps are enough for using ecspi.

Hope these steps are helpful for you!

Have a nice day!

B.R,

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wigros Sun:

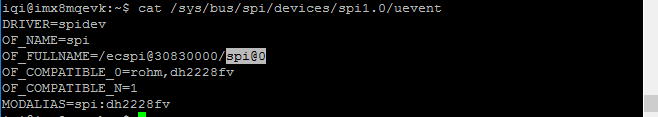

Return the SPI problem.After configuring the device tree in your way.I should get two devices /dev/spidev1.0 and /dev/spidev1.1 because I have a chip selection pin,but now I just get a spidev /dev/spidev1.0.

Should MX8MQ_IOMUXC_ECSPI2_SS0_GPIO5_IO13 is replaced by MX8MQ_IOMUXC_ECSPI2_SS0_ECSPI2_SS0

We look forward to your relpy!

Have a nice day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let us discuss it in Chinese, if you can't understand Chinese, let me know.

你要连接2个device,当你的device tree里需要给spi节点2个chipselect了。你现在只有一个,那么就会只有spidev1.0。

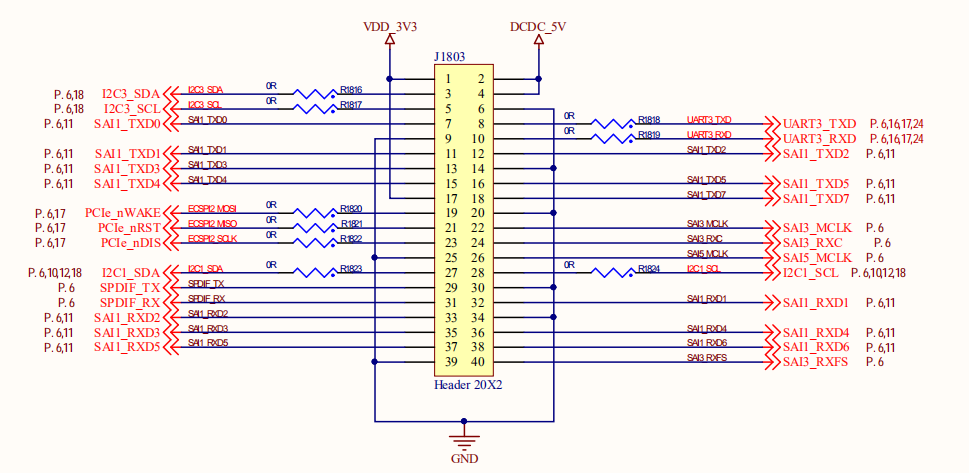

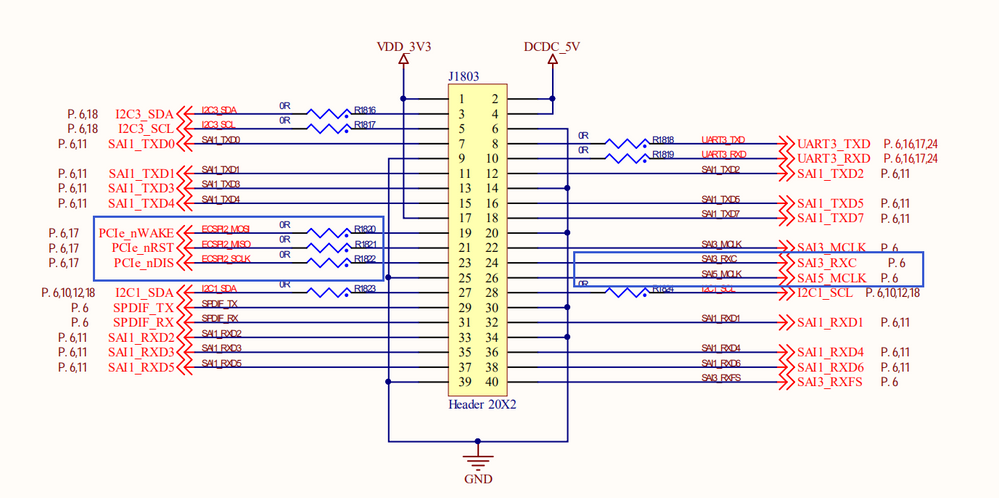

(1)你的引脚定义的24/26脚,没有连接到ECSPI2_SS0上,那么也就是说上面的复用是无效的。你应该一个spidev都看不到的。

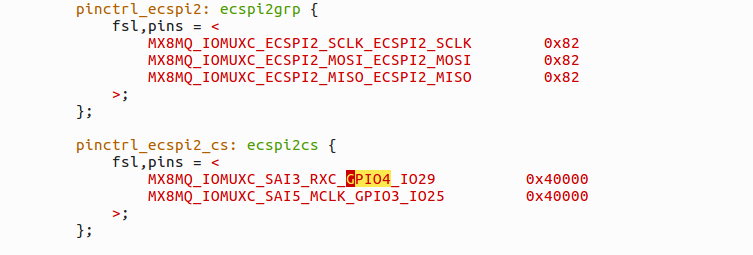

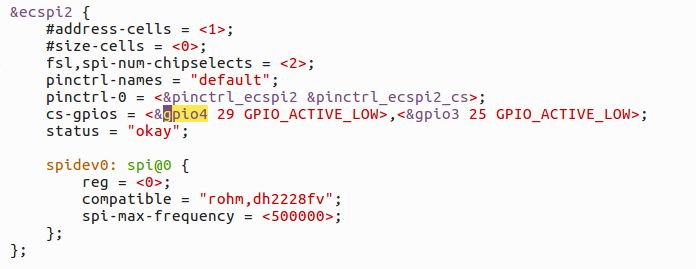

(2)你的CE0/CE1用的是SAI3_RXC和SAI5_MCLK,理论上复用为GPIO做应该可以做CS用。你可以试试行不行。

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MQ_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

MX8MQ_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82

MX8MQ_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82

>;

};

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MQ_IOMUXC_SAI3_RXC_GPIO4_IO29 0x40000 /*CS0*/

MX8MQ_IOMUXC_SAI5_MCLK_GPIO3_IO25 0x40000 /*CS1*/

>;

};

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <2>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>;

cs-gpios = <&gpio4 29 GPIO_ACTIVE_LOW>,<&gpio3 25 GPIO_ACTIVE_LOW>;

status = "okay";

/* code below is determined by what device is connected to eCSPI, change it to yours */

spidev0: spi@0 {

reg = <0>;

compatible = "rohm,dh2228fv";

spi-max-frequency = <500000>;

};

};

你试试上面的方法。

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Weidong:

我按照您的方法对fsl-imx8mq-evk.dts设备树文件进行了配置,但是并没有生成设备节点。我猜想是不是SAI3_RXC和SAI5_MCLK的pad control reg 的值配置错误了,不应该是0x40000,寄存器的值应该是0x15或者0x5吧。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

时间有限,我没有仔细地看寄存器,你可以配置一下看看。

修改 0x40000,其他不用动。

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

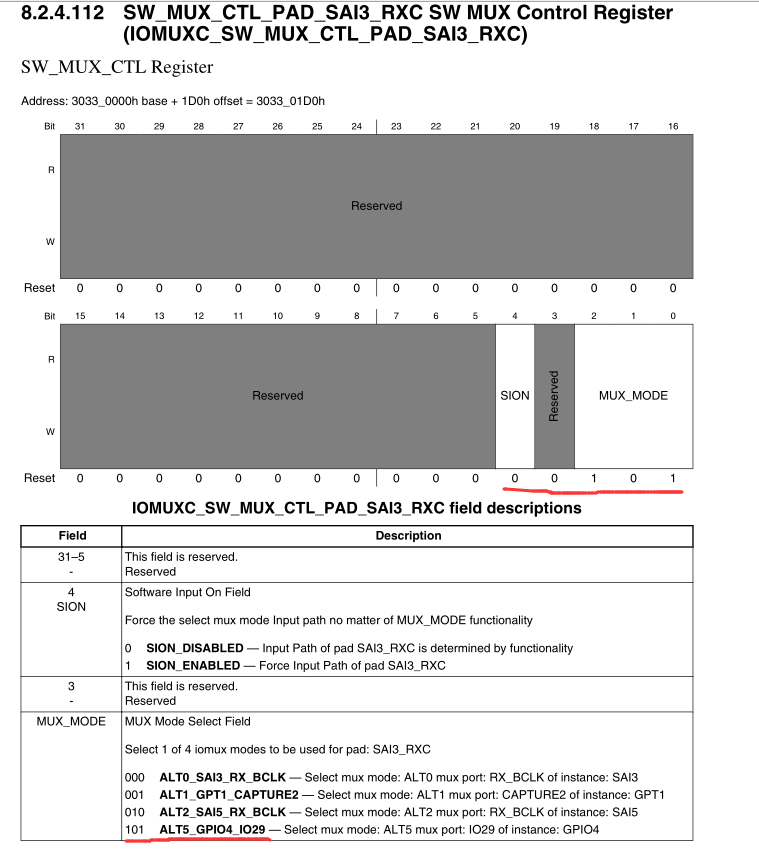

我根据您配置ECSPI2_SCLK、ECSPI2_MOSI、 ECSPI2_MISO三个管脚的控制寄存器的值,来配置了SAI3_RXC和SAI5_MCLK两个控制寄存器的值为0x82但是结果差强人意,还是没有出现相应的spidev,但是新添加的ecspi2节点应该是注册上了。

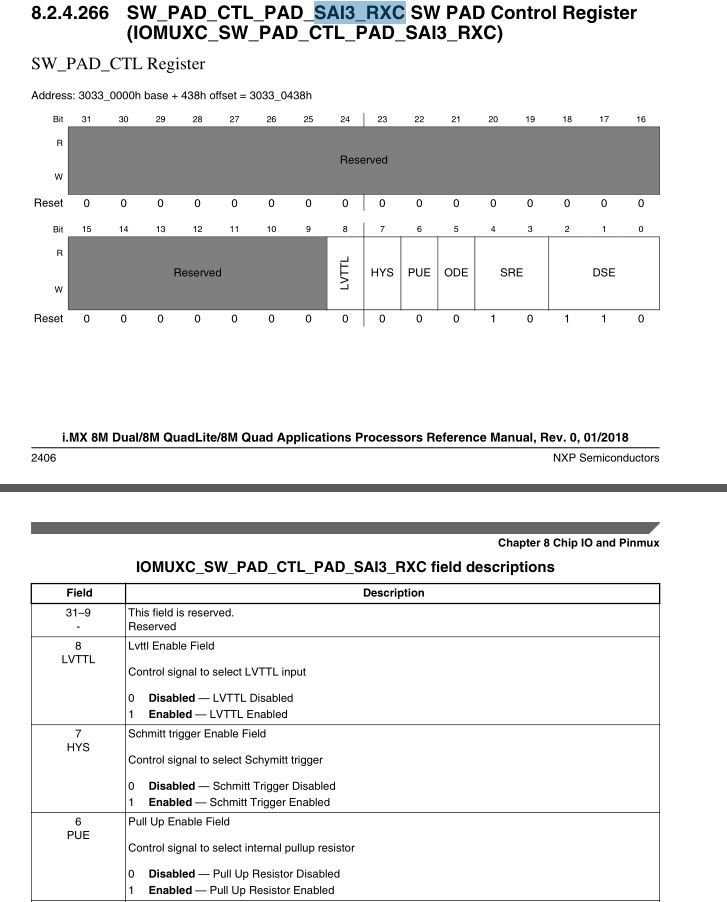

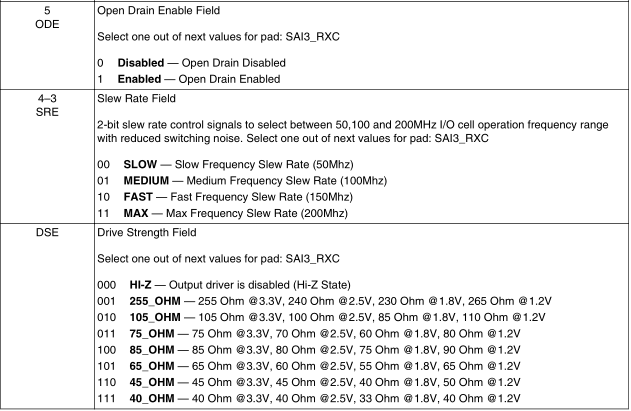

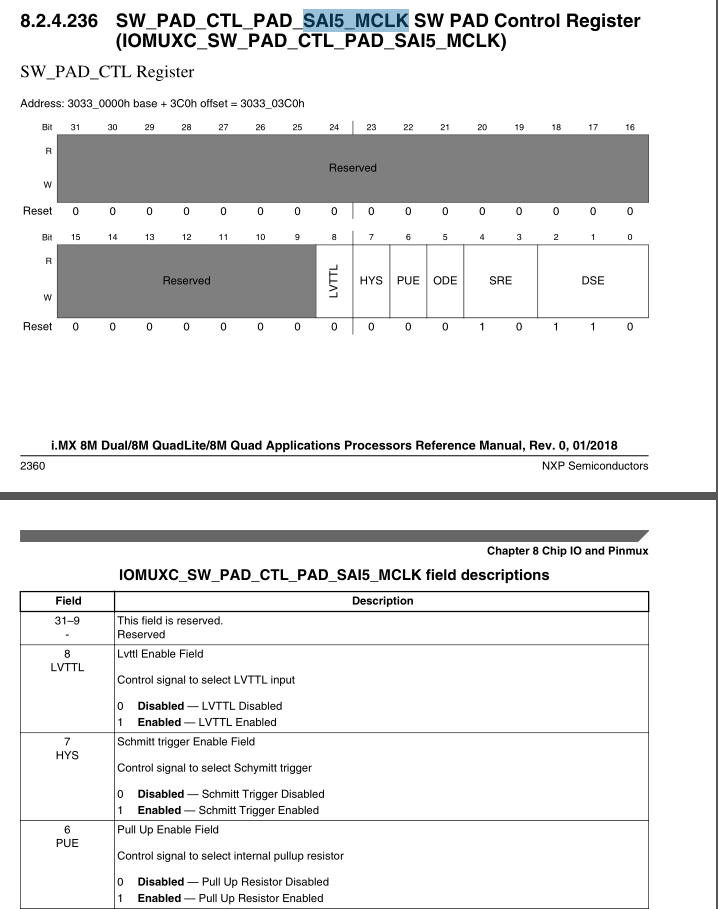

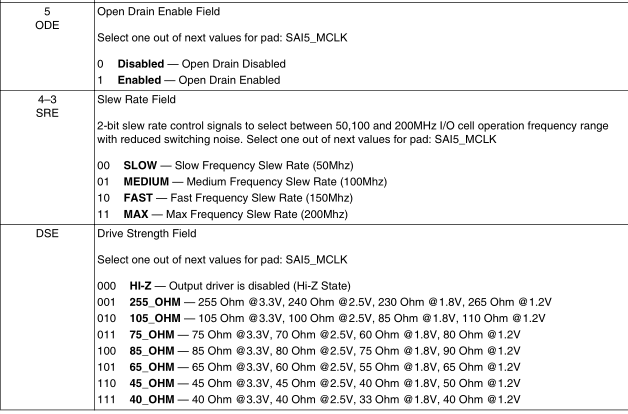

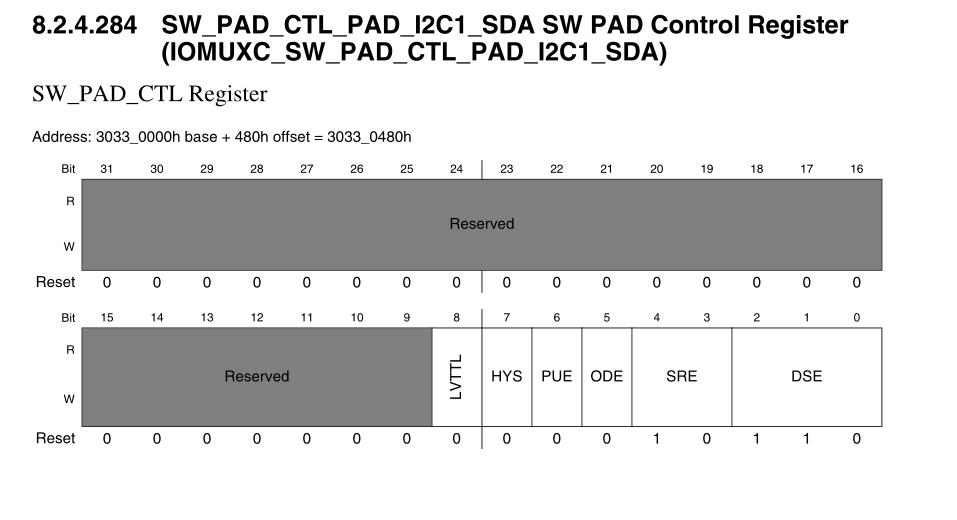

为了节约您的时间。我把SAI3_RXC和SAI5_MCLK两个管脚控制寄存器的datasheet放在下面,麻烦您帮忙解决一下。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

DSE = 100

SRE = 01

ODE = 0

PUE = 0

HYS = 1

LVTTL = 0

凑起来就应该是: 1000 1100 -- >0x8C

你试试行不行。

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

我测试了还是不行。我感觉设备树的问题应该不大,您觉得是否和SPI设备驱动层有关系吗。是否有什么好的解决方法

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

那就不是PAD配置的问题了。

之前你使用ECSPI2_SS0复用为GPIO,并用它们做chipselect时,你有一个spidev出现,这个我觉得很奇怪。

你的CE0和CE1,硬件上没有接这个ECSPI2_SS0,为什么会有spidev产生呢?

那么你现在这样试试:

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MQ_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

MX8MQ_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82

MX8MQ_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82

>;

};

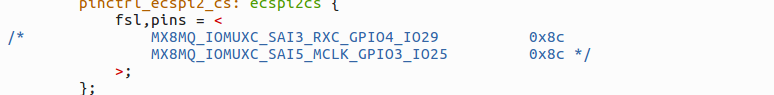

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MQ_IOMUXC_SAI3_RXC_GPIO4_IO29 0x8C

/* MX8MQ_IOMUXC_SAI5_MCLK_GPIO3_IO25 0x8C */

>;

};

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>;

cs-gpios = <&gpio4 29 GPIO_ACTIVE_LOW>;

status = "okay";

/* code below is determined by what device is connected to eCSPI, change it to yours */

spidev0: spi@0 {

reg = <0>;

compatible = "rohm,dh2228fv";

spi-max-frequency = <500000>;

};

};

也就是说用1个GPIO,挂一个SPIDEV,把你设计的SPI device接上去。启动板子,看有没有spidev产生,如果产生了,你访问以下这个实际的spidev,看看能不能正常工作。

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

关于SPI,只需要配置三根线(MOSI,MISO,SCLK)就可以的到spidev,无论cs是否配置引脚,还是配置多个引脚。目前我无法进行测试,因为开发板还在制作当中,目前用的是方案商提供的测试版,没有引出引脚。所以无法确定问题的根本。

编译这个设备树,还是可以得到spidev1.0

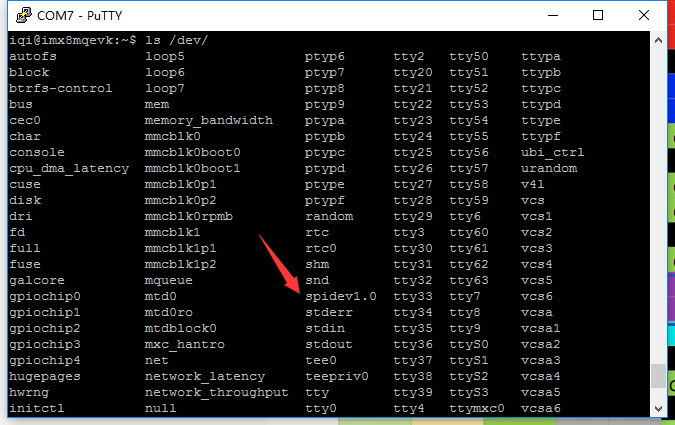

iqi@imx8mqevk:~$ ls /dev/s

shm/ snd/ spidev1.0 stderr stdin stdout

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

你还是需要找一个SPI之类的外部device来测试 一下的,否则,根本不知道是不是正确。哪怕设计一个简单小板子用来测试也行。

weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wigros Sun:

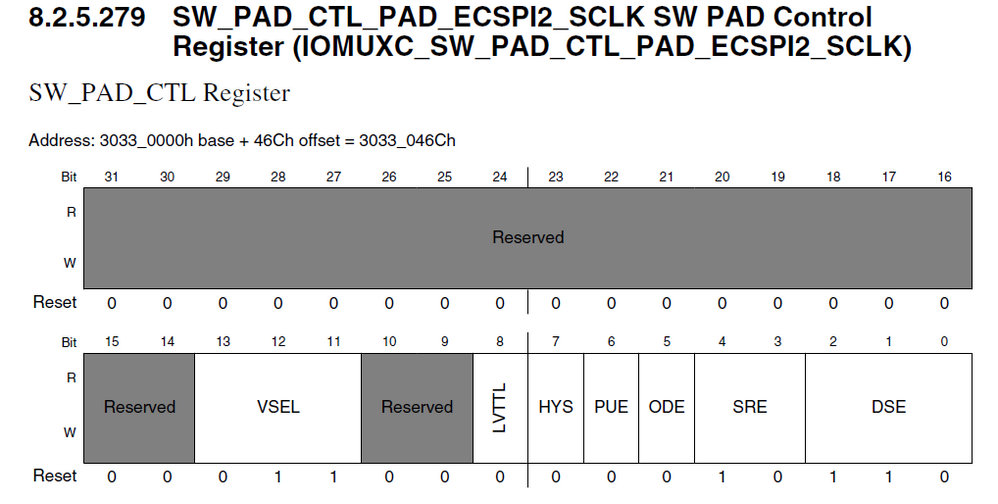

Thanks for you advice.But I still have a question.Why ues 0x82 in node? When I modified GPIO earlier, I looked for the MUX register offset address in the include/dt-bindings/pinctrl/pins-imx8mq.h file.In pins-imx8mq.h I'm not find 0x82.

include/dt-bindings/pinctrl/pins-imx8mq.h

#define MX8MQ_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x204 0x46C 0x000 0x0 0x0

#define MX8MQ_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x208 0x470 0x000 0x0 0x0

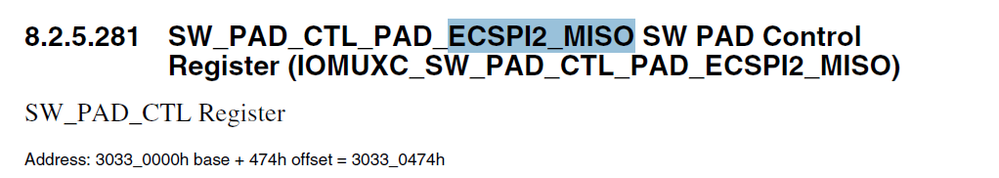

#define MX8MQ_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x20C 0x474 0x000 0x0 0x0

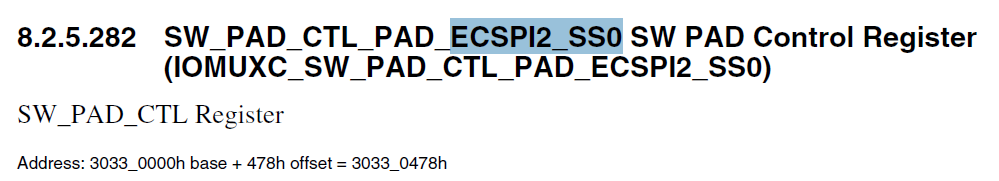

#define MX8MQ_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x210 0x478 0x000 0x5 0x0

We look forward to your reply!Have a nice day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

See below configurations, please!

-------------------------------------------------

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MQ_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

MX8MQ_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82

MX8MQ_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82

>;

};

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MQ_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x40000

>;

};

-------------------------------------------------

0x82 is value of it's PAD control register, for example: ECSPI2_SCLK's pad register is :IOMUXC_SW_PAD_CTL_PAD_ECSPI2_SCLK , page 1744, reference manual.

the register is used to tune driver strengh of the PAD. you can change the configuration for you application.

For other pads, like ECSPI2_MOSI/ECSPI2_MISO/ECSPI2_SS0, they also have related pad control register.

they are all described in reference manual.

Have a nice day!

B.R,

weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wigros Sun:

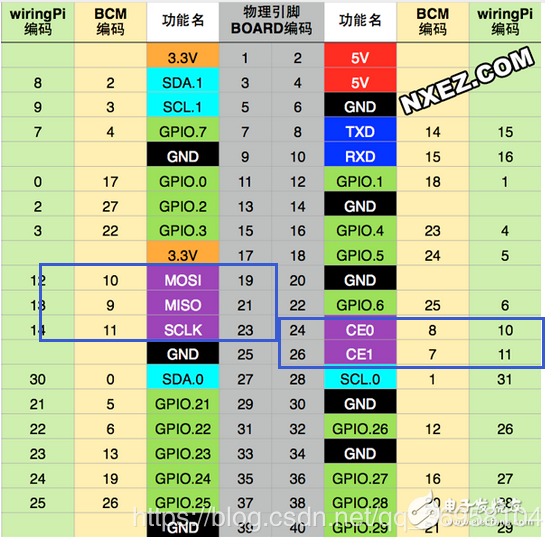

I see what you mean.I want to know how to select the pad register value of other pins in dts.The pins correspond to each other on the two pictures.

We look forward to you reply.

Have a nice day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

MX8MQ_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

it means that 0x82 will be written to IOMUXC_SW_PAD_CTL_PAD_ECSPI2_SCLK. Not Read.

Read and understand each filed of the register. then configure (write value to the register) them.

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wigros Sun:

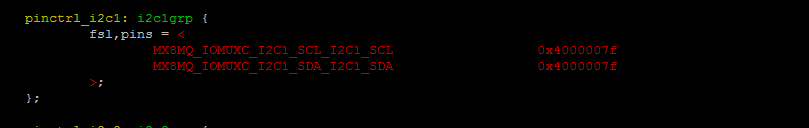

I see that your mean.But i have a problem.The PAD I2C1_SDA value to be written should be between 0x1ff and 0(only bit0~bit8 can be operated),why 0x4000007f ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For Reserved filed, you don't need to set them.

weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi:

I knew that,but I haven't changed I2C1_SDA value.by default ,the I2C1_SDA value is 0x4000007f.What I want to know is why the I2C1_SDA value be set to 0x4000007f.

have a nice day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wigros Sun:

Do you mean this value(0x82) is read through the address of pad register or the register add ?

If not,I check the IOMUX_PAD define,