- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: iMX8MPlus + DDR4 stuck at wait_ddrphy_training_complete()

iMX8MPlus + DDR4 stuck at wait_ddrphy_training_complete()

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Community,

We are bringing up a custom iMX8MP based board using DDR4 (Micron MT40A512M16LY). We were able to follow the steps described in MSCALE_DDR_Tool_User_Guide.pdf and the DDR Calibration completed with success.

However, when integrating the generated ddr4_timing.c into u-Boot lf_v2021.04 aligned to BSP-5.10.52_2.1.0, the board got stuck at the while loop within wait_ddrphy_training_complete()

U-Boot SPL 2021.04 (Jan 12 2023 - 16:20:19 +0700)

DDRINFO: start DRAM init

DDRINFO: cfg clk

DDRINFO: DRAM rate 3200MTS

DDRINFO: ddrc config start

DDRINFO: ddrc config done

DDRINFO:ddrphy config start

DRAM PHY training for 3200MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Enter wait_ddrphy_training_complete() // I added this at the begining of wait_ddrphy_training_complete()

Could you help to point out what could be the issue, please?

In attachment is our custom RPA.

Thanks in advance and best regards,

Khang

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI @Rita_Wang ,

I resolved the issue by being able to select 1 for Number of frequency setpoints

If I kept Number of frequency setpoints as 2, I think it would also work of I modified FREQ1 setpoints Clock Cycle Freq (MHz) from 668 to 533 for having data rate 1066 as the case of other references (including iMX8MP-EVK with DDR4) but I haven't tested yet.

Thanks for your support.

K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you share the DDR datasheet and your DDR section schematic to us?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Rita_Wang ,

I shared with you the DDR4 part of schematic as well as the datasheet of the DDR4 in private message.

Regards,

K.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Rita_Wang ,

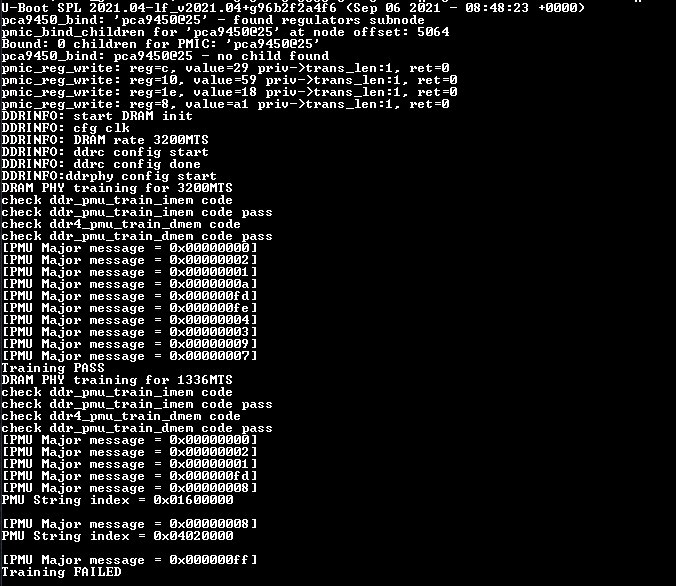

I was able to go a little bit further : not being stuck anymore but training reported FAILED for rate = 1336MTS :

What could be the issue, please ?

Best Regards,

K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Rita_Wang , @khang_letruong

On the i.MX8M Plus EVK, LPDDR4 memory is used. However, on our custom board, we are using DDR4 memory (Part No: MT40A1G16RC-062EIT:B)

we also facing same issue like you , i am attaching the boot prints.

20-11-2025 19:21:50.120 [RX] - <NUL><CR><LF>

U-Boot SPL 2025.04-g44898b9f3cfe-dirty (Nov 20 2025 - 18:39:51 +0530)<CR><LF>

DDRINFO: start DRAM init<CR><LF>

DDRINFO: cfg clk<CR><LF>

DDRINFO: DRAM rate 3200MTS<CR><LF>

DDRINFO: ddrc config start<CR><LF>

DDRINFO: ddrc config done<CR><LF>

DDRINFO:ddrphy config start<CR><LF>

PHY init... configuration cmplted<CR><LF>

DRAM PHY training for 3200MTS<CR><LF>

<NUL><NUL><CR><LF>

U-Boot SPL 2025.04-g44898b9f3cfe-dirty (Nov 20 2025 - 18:39:51 +0530)<CR><LF>

DDRINFO: start DRAM init<CR><LF>

DDRINFO: cfg clk<CR><LF>

DDRINFO: DRAM rate 3200MTS<CR><LF>

DDRINFO: ddrc config start<CR><LF>

DDRINFO: ddrc config done<CR><LF>

DDRINFO:ddrphy config start<CR><LF>

PHY init... configuration cmplted<CR><LF>

DRAM PHY training for 3200MTS<CR><LF>

[PMU Major message = 0x00000000]<CR><LF>

[PMU Major message = 0x00000002]<CR><LF>

[PMU Major message = 0x00000001]<CR><LF>

[PMU Major message = 0x0000000a]<CR><LF>

[PMU Major message = 0x000000fd]<CR><LF>

[PMU Major message = 0x000000fe]<CR><LF>

[PMU Major message = 0x00000008]<CR><LF>

PMU String index = 0x001c0003<CR><LF>

arg[0] = 0x00000002<CR><LF>

arg[1] = 0x00000002<CR><LF>

arg[2] = 0x00000004<CR><LF>

[PMU Major message = 0x00000008]<CR><LF>

PMU String index = 0x04020000<CR><LF>

[PMU Major message = 0x000000ff]<CR><LF>

Training FAILED<CR><LF>

Also attched the RPA file for DDR4(I.MX8MPLUS).

can you please suggest any ideas to go forward.

thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again @Rita_Wang ,

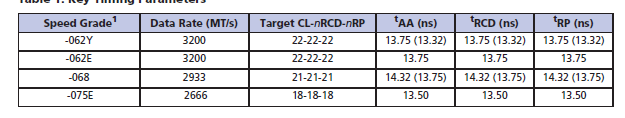

Precisely, our DDR4 is MT40A512M16LY-062:E and it has data rate 3200 in the below table :

So naturally the training is passed at that speed but not others. Do you think so? If yes, how to "by-pass" other training speeds, please?

It looks like there was a similar issue supported by @igorpadykov about iMX8MM with similar DDR4 family.

Regards,

K.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Relate to training rate 1336, I found that it appears in the end of our generated ddr4_timing.c :

struct dram_fsp_msg ddr_dram_fsp_msg[] = {

{

/* P0 3200mts 1D */

.drate = 3200,

.fw_type = FW_1D_IMAGE,

.fsp_cfg = ddr_fsp0_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp0_cfg),

},

{

/* P1 1336mts 1D */

.drate = 1336,

.fw_type = FW_1D_IMAGE,

.fsp_cfg = ddr_fsp1_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp1_cfg),

},

{

/* P0 3200mts 2D */

.drate = 3200,

.fw_type = FW_2D_IMAGE,

.fsp_cfg = ddr_fsp0_2d_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp0_2d_cfg),

},

};

/* ddr timing config params */

struct dram_timing_info dram_timing = {

.ddrc_cfg = ddr_ddrc_cfg,

.ddrc_cfg_num = ARRAY_SIZE(ddr_ddrc_cfg),

.ddrphy_cfg = ddr_ddrphy_cfg,

.ddrphy_cfg_num = ARRAY_SIZE(ddr_ddrphy_cfg),

.fsp_msg = ddr_dram_fsp_msg,

.fsp_msg_num = ARRAY_SIZE(ddr_dram_fsp_msg),

.ddrphy_trained_csr = ddr_ddrphy_trained_csr,

.ddrphy_trained_csr_num = ARRAY_SIZE(ddr_ddrphy_trained_csr),

.ddrphy_pie = ddr_phy_pie,

.ddrphy_pie_num = ARRAY_SIZE(ddr_phy_pie),

.fsp_table = { 3200, 1336, },

};

Meanwhile, in the ddr4_timing.c of iMX8MP-EVK, 2nd data rate is 1066 :

struct dram_fsp_msg ddr_dram_fsp_msg[] = {

{

/* P0 3200mts 1D */

.drate = 3200,

.fw_type = FW_1D_IMAGE,

.fsp_cfg = ddr_fsp0_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp0_cfg),

},

{

/* P1 1066mts 1D */

.drate = 1066,

.fw_type = FW_1D_IMAGE,

.fsp_cfg = ddr_fsp1_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp1_cfg),

},

{

/* P0 3200mts 2D */

.drate = 3200,

.fw_type = FW_2D_IMAGE,

.fsp_cfg = ddr_fsp0_2d_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp0_2d_cfg),

},

};

/* ddr timing config params */

struct dram_timing_info dram_timing = {

.ddrc_cfg = ddr_ddrc_cfg,

.ddrc_cfg_num = ARRAY_SIZE(ddr_ddrc_cfg),

.ddrphy_cfg = ddr_ddrphy_cfg,

.ddrphy_cfg_num = ARRAY_SIZE(ddr_ddrphy_cfg),

.fsp_msg = ddr_dram_fsp_msg,

.fsp_msg_num = ARRAY_SIZE(ddr_dram_fsp_msg),

.ddrphy_trained_csr = ddr_ddrphy_trained_csr,

.ddrphy_trained_csr_num = ARRAY_SIZE(ddr_ddrphy_trained_csr),

.ddrphy_pie = ddr_phy_pie,

.ddrphy_pie_num = ARRAY_SIZE(ddr_phy_pie),

.fsp_table = { 3200, 1066, },

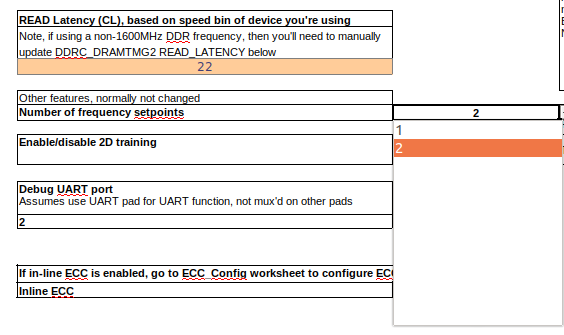

};I tried to modify the RPA by changing number of frequency setpoints from 2 to 1 :

But MSCALE_DDR_Tool denied to run the stress test :

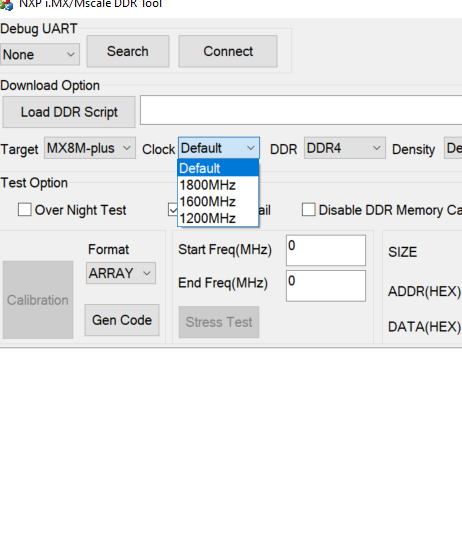

I then changed the Clock to specific value of my DDR4 (1600) instead of Default:

but the ddr4_timing.c is the same as before (i.e 1336 still appeared).

Not sure how to remove that 1336 data rate out of the ddr4_timing.c.

Regards,

K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI @Rita_Wang ,

I resolved the issue by being able to select 1 for Number of frequency setpoints

If I kept Number of frequency setpoints as 2, I think it would also work of I modified FREQ1 setpoints Clock Cycle Freq (MHz) from 668 to 533 for having data rate 1066 as the case of other references (including iMX8MP-EVK with DDR4) but I haven't tested yet.

Thanks for your support.

K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good news it works.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Rita_Wang ,

Thank you. But now I am facing another problem : https://community.nxp.com/t5/i-MX-Processors/iMX8MP-DDR4-bringup-SPL-failed-to-boot-from-all-boot-de...

Could you also provide support, please ?

Best Regards,

Khang