- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

ddr3 data lines swapped + imx6sl

Hi,

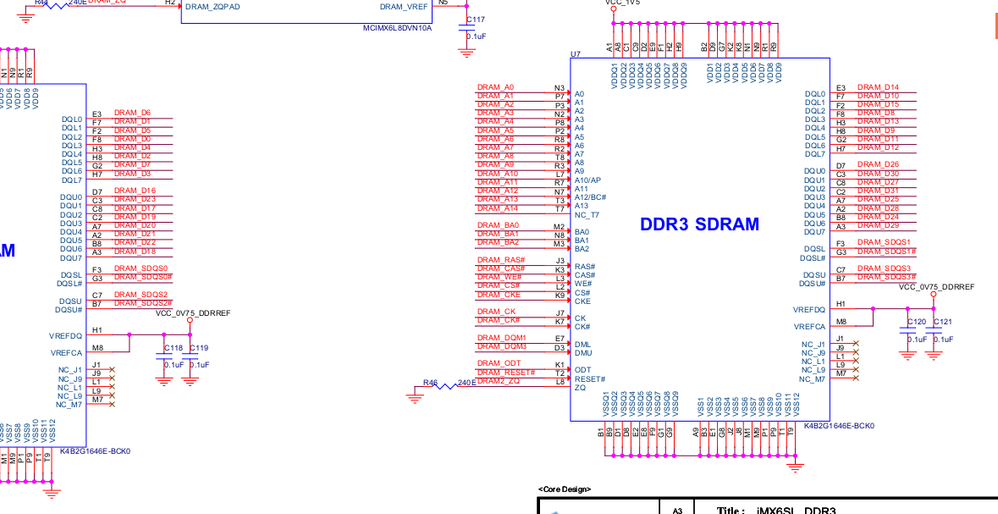

We are developing a custom board based on the imx6sl evolution kit. We are going to use 2 ddr3 through single chip select. both ddr are 256 MB size.

Now for better routing purpose, We have swapped the ddr data lines coming from the processor.

data byte 1 from processor is connected to dql0 to dql7 on 1st ddr. but this line are swapped for efficient routing like, d6 from processor is connected to dql0 of ddr etc.

data byte 2 from processor id connected to 2nd ddr's dql0 to dql7. similarly data byte3 from processor connected to dqu0 to dqu7.

We have also swapped the dqs lines between different bytes. like dqs0 is for byte1, dqs2 is for byte2, dqs1 is for byte3 etc.

So, for dqs and data lines swapping what changes we need to do in ddr controller registers?

Is this approach fine?

Thanks,

Jags

1.

According to section 2.5.1 (Swapping data lines) of the "Hardware Development Guidefor i.MX 6SoloLite" :

The rules are as follows:

• Hardware write leveling – lowest order bit within byte lane must remain on lowest order bit of lane

by JEDEC compliance (see the “Write Leveling” section in JESD79-3E)

— D0, D8, D16, D24, D32, D40, D48, and D56 are fixed

— Other data lines free to swap within byte lane

• JEDEC DDR3 memory restrictions are:

– No restrictions for complete byte lane swapping

– DQS and DQM must follow lanes.

2.

No need for specific memory controller settings.

3.

Please let us look at the connection scheme (i.MX6-SL <-> DDR3) for assurance.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Yuri,

Thanks for the informative reply.

Below is the pic. of my ddr3 connection with imx6sl.

Please suggest the hardware and software changes.

Dear Jags,

Sorry for the totally off-topic message, but we are design a custom board too and we are going to implement a ethernet switch based on Marvell 88E6060 and I would like to talk to you since I saw in previous posts that you already used it and probably have a verified design. Would it be OK for us to have some e-mails about it? ercorreia@gmail.com

Best regards and Thank you!

Hi, Jags Gediya !

The only point :

for Write Leveling it is recommended D0, D8, D16, D24 to be fixed.

Please consult with DDR3 Datasheet if memory requires using just the LSB

in Write Leveling, the DDR3 device can use all byte during Write Leveling.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------