- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hello,

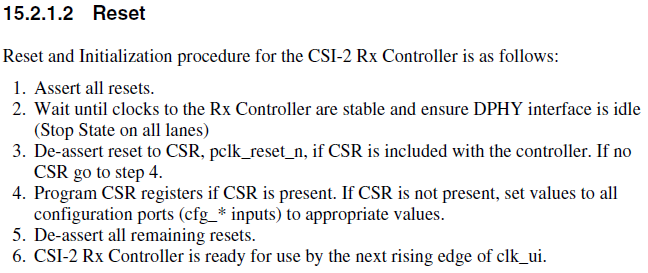

From IMX8DQXPRM.pdf (Rev.0)

I am trying MIPI-CSI2's driver porting to other OS. Please let me confirm detail of above procedure.

<Development Environment>

SoC : i.MX8QXP

Board : MCIMX8QXP-CPU

Based BSP : Linux BSP L4.14.98_2.3.0_ga

<Questions>

Q1. "2. Wait until clocks to the Rx Controller are stable and ensure DPHY interface is idle".

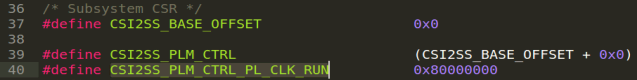

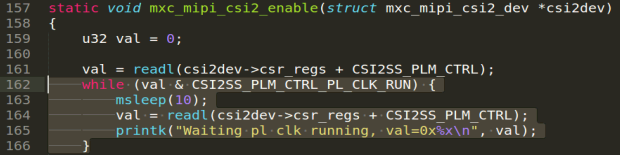

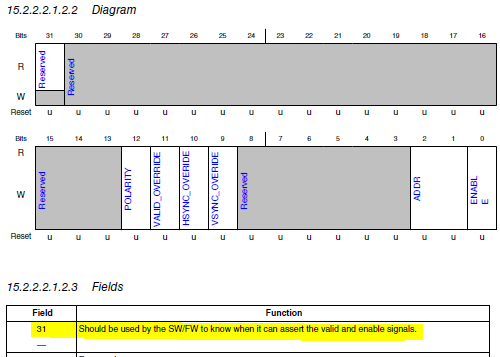

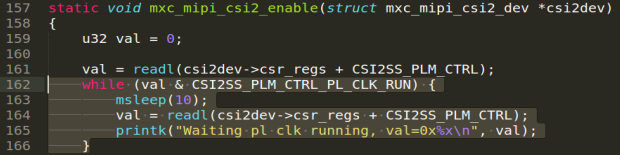

above comments are implemented by following code. Is it right? I could not clearly understand meaning of the bit#31. because it is defined as reserved in RM.

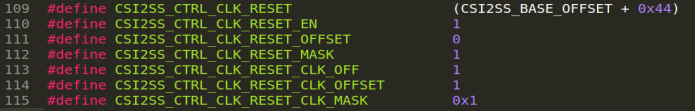

Copy from linux/drivers/media/platform/imx8/mxc-mipi-csi2.h

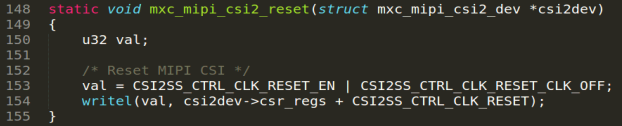

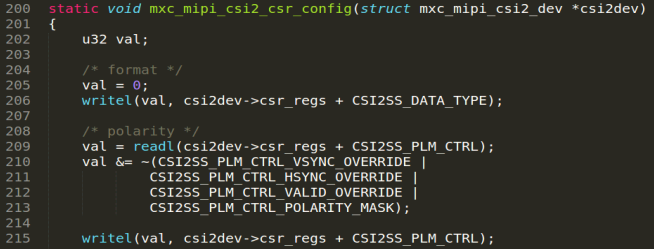

Copy from linux/drivers/media/platform/imx8/mxc-mipi-csi2.c

Q2. "1. Assert all resets." It is implemented by following code. Is it right?

Copy from linux/drivers/media/platform/imx8/mxc-mipi-csi2.h

Copy from linux/drivers/media/platform/imx8/mxc-mipi-csi2.c

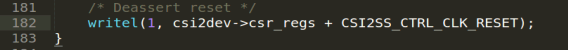

Q3. "5. De-assert all remaining resets." It is implemented by follwoing code. Is it right?

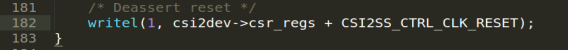

Copy from linux/drivers/media/platform/imx8/mxc-mipi-csi2.c

Q4. Control is different between "Assert reset" and "De-assert reset", but the current settings are same.

Looks like both code set to 1b to CONTROLLER_CLOCK_RESET_CONTROL register. Is it okay?

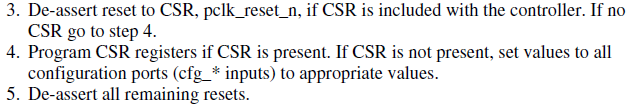

Q5. From description no.3 and no.4 in RM, we should de-assert reset to CSR before program CSR registers.

I could not find suitable code which de-assert reset to CSR in Linux BSP.

How do I de-assert reset to CSR?

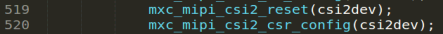

Copy from linux/drivers/media/platform/imx8/mxc-mipi-csi2.c

Best Regards,

Kazuma Sasaki.

已解决! 转到解答。

Q1)yes, since this bit is reserved, it means that the customer don't need to care about this bit, just leave this bit as default

Q2)yes

Q3) it seems this code is for de-assert reset to CSR before program CSR registers

Q4)yes, in the bsp set them as the same value

Q5)see the Q3), in fact you can refer to the sequence from the bsp like:

if (enable) { pm_runtime_get_sync(dev); if (!csi2dev->running) { mxc_csi2_get_sensor_fmt(csi2dev); mxc_mipi_csi2_hc_config(csi2dev); mxc_mipi_csi2_reset(csi2dev); mxc_mipi_csi2_csr_config(csi2dev); mxc_mipi_csi2_enable(csi2dev); mxc_mipi_csi2_reg_dump(csi2dev); }

Q1)yes, since this bit is reserved, it means that the customer don't need to care about this bit, just leave this bit as default

Q2)yes

Q3) it seems this code is for de-assert reset to CSR before program CSR registers

Q4)yes, in the bsp set them as the same value

Q5)see the Q3), in fact you can refer to the sequence from the bsp like:

if (enable) { pm_runtime_get_sync(dev); if (!csi2dev->running) { mxc_csi2_get_sensor_fmt(csi2dev); mxc_mipi_csi2_hc_config(csi2dev); mxc_mipi_csi2_reset(csi2dev); mxc_mipi_csi2_csr_config(csi2dev); mxc_mipi_csi2_enable(csi2dev); mxc_mipi_csi2_reg_dump(csi2dev); }

Dear Joan,

I appreciate your support. Please let me confirm a few points again.

Q1 ) You told me that we don't need to care about this bit.

But, Linux BSP is checking this bit to know the timing of pl condition.

Should we care this bit same as linux BSP?

Q3&Q5 ) You told me that my pointed code is for de-assert reset to CSR before program CSR registers.

But, the above code is writing in mxc_mipi_csi2_enable function.

it means that the above code is for de-assert reset to CSR after program CSR registers.

Therefore, I guessed the above code is for de-assert all remaining resets from RM description.

In any case, Could you please teach me the correct register settings for the following two cases.

case 1. De-assert reset to CSR.

case 2. De-assert reset to all remaining resets.

Should we set 1b to CSI2_SS_CTRL_CLK_RESET register in both cases?

Best Regards,

Kazuma Sasaki.

Q1)YES, I mean you can set as linux bsp, enable this bit, because this bit is reserved, so I don't find any document mentions this, just refer to the linux bsp

Q3&Q5 ) to be honest, I'm not sure if the reset sequence in the linux bsp is the same as Reference Manual, but I confirmed that customer can refer to the linux bsp sequence, the steps are csi2_reset->CSR configuration-> CSI2 enable, for de-assert reset, according to the linux bsp, should set to CSI2SS_CTRL_CLK_RESET to 1