- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

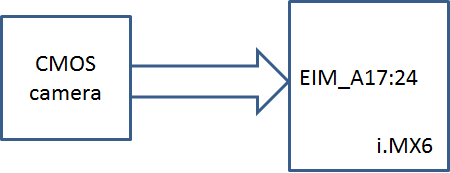

Our customer want to use the second camera using IPU2-CSI1 parallel interface.

IPU2-CSI1 pin allocation may be following.

MX6Q_PAD_EIM_A17 <= IPU2_CSI1_D_12,

MX6Q_PAD_EIM_A18 <= IPU2_CSI1_D_13,

MX6Q_PAD_EIM_A19 <= IPU2_CSI1_D_14,

MX6Q_PAD_EIM_A20 <= IPU2_CSI1_D_15,

MX6Q_PAD_EIM_D19 <= IPU2_CSI1_D_16,

MX6Q_PAD_EIM_A22 <= IPU2_CSI1_D_17,

MX6Q_PAD_EIM_A23 <= IPU2_CSI1_D_18,

MX6Q_PAD_EIM_A24 <= IPU2_CSI1_D_19,

According to i.MX6dq data sheet, after out of reset, these pins become the output port and out low level signal.

Therefore, after reset, Do we must not tie a signal of the CMOS camera to EIM_A[17:24] until MUX_MODE is changed ?

Best Regards.

kanou

已解决! 转到解答。

Hi Mamoru

yes your understanding is correct:

due to signal contention it is not recommended

to tie/enable a signal from CMOS camera to EIM_A[17:24] until

MUX_MODE is changed.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Mamoru

yes your understanding is correct:

due to signal contention it is not recommended

to tie/enable a signal from CMOS camera to EIM_A[17:24] until

MUX_MODE is changed.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------