GPIO1_IO07 Reset condition

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I need some information about the reset condition of a certain pin.

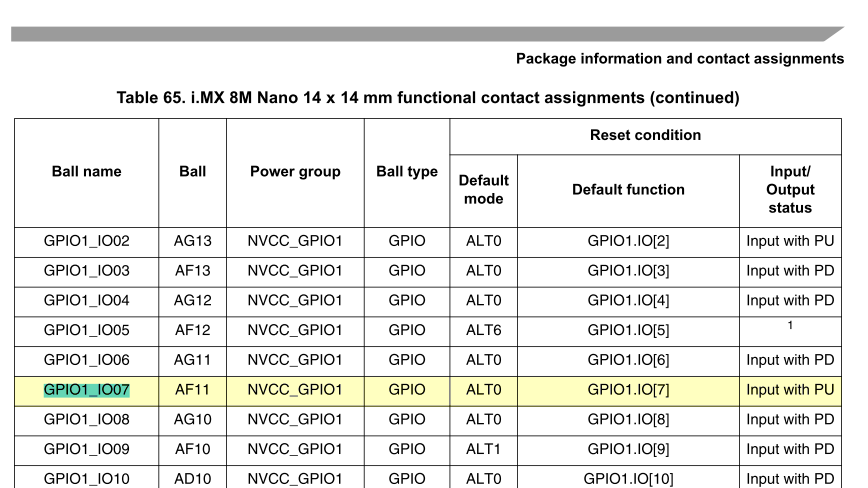

The i.MX8M Nano datasheet lists reset condition in table 65.

For GPIO1_IO07 it lists “Input with PU” after reset.

If I delete our NAND completely and do a reset, so that the i.MX8M Nano cannot boot, the pin has a low level after the reset.

This low level persists.

I measured a ca. 13kOhm internal pull-down.

We expect a high value for this pin after reset on our electronic until U-Boot defines some new configuration for that pin.

How does this fit to the info from the datasheet? Am I misinterpreting the information there?

If there is an internal PD after reset on this pin, we would have to use another pin on our board.

Kind regards

Johannes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Could you compare the measure that you took from the GPIO1_IO07 to another from the same group and share the results? For example the GPIO1_IO02 that has the same configuration.

Regards,

Israel H.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Israel,

GPIO1_IO02 is high after reset.

I do not know if it is active high or has an internal pull-up, but it is definitely high level, even when there is no SW booting.

Thanks

Johannes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johannes,

Ok but please take the measure of the pin with a multimeter in impedance and compare it with the pin that is not working.

Regards,

Israel H.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Israel,

i measured impedance after reset of GPIO1_IO02 using a resistor divider after reset. (A multimeter does not work here, as it also acts as a voltage source).

This is what i measured on a i.MX8M Nano SoloLite:

GPIO1_IO02 internal PU with ca. 11kOhm (ok)

GPIO1_IO07 internal PD with ca. 13kOhm (not like in datasheet!)

As can be seen in the datasheet excerpt above, this is not what it should be.

Could it have to to something with our fuse settings?

Can you confirm that on your HW?

Thank you very much, kind regards

Johannes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johannes,

Before anything this could be caused by many things, first we need to discard any structural issue, could you perform a xray on the ball/pin that is affected? Just to confirm that we do not have any structural issue .

Regards,

Israel H.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Israel,

I cannot make an xray but I am sure we have a systematic issue here. I measured the voltage on 5 different samples and it always showed the same result. Those samples came out of 2 different HW production sites.

So, I am sure, this is not related to ball cracks.

Thanks and kind regards,

Johannes