- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- About setting PHY Register 03 and PHY Register 04

About setting PHY Register 03 and PHY Register 04

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear support,

34.5.166 PHY Register 03 (DDRMC_PHY03)

34.5.167 PHY Register 04 (DDRMC_PHY04)

When I use DLL at Auto-configure mode, it is necessary to set this register?

Best regards,

Keisuke Watanabe

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that is correct but ENCODER is not the DLL_LOCK_VALUE

It is related to but not the same. Basically you don't need to worry about this ENCODER number. It is internal data and It should be transparent for you in auto-configure mode.

At the end you only need to tell what is the percentage of one-cycle delay you want.

So if you want 50% then DLL_WRITE_DL = 64 ===> DLL_WRITE_DL/128 = 0.5

25% then DLL_WRITE_DL = 32 ===> DLL_WRITE_DL/128 = 0.25

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Keisuke,

The DLL corresponds to an internal module which is delay locked loop.

In the case of phy_03 this just represents the starting value for the DLL, the DLL eventually will find a value to lock. In general, this will be transparent for the user so just set this register to 0x4 as recommened.

In the case of phy_04 I am currently investigating, I let you know when I have more details.

Regards,

Ioseph

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ioseph_martinez do you have an update on this case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Ioseph-san,

Is it ok to set PHY_03 as 0x04 with Auto configure mode?

Could you also confirm PHY_04 iwth Auto conifugure mode?

Best Regards

Taku

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

juangutierrez can you continue with the follow up on this case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For Auto configure mode DDRMC_PHY03[DLL_START_POINT] you can set it to 0x04.

This value will be the starting point for the phase detector which will lock at a certain value called DLL_LOCK_VALUE which indicates the delay of one cycle.

The number of delay elements that are needed to capture an entire clock cycle is then converted into an unsigned integer named encoder [7:0]

Let say the period of 1 cycle is 100ms and encoder = 100.

Hence each delay element delays the signal 1ms and encoder = 100 which means that 100 delay elements are needed to delay the signal one complete cycle (100ms)

The actual delay setting for the delay lines is calculated by multiplying the encoder [7:0] integer by the parameter settings for each delay line and then dividing by 128 and rounding.

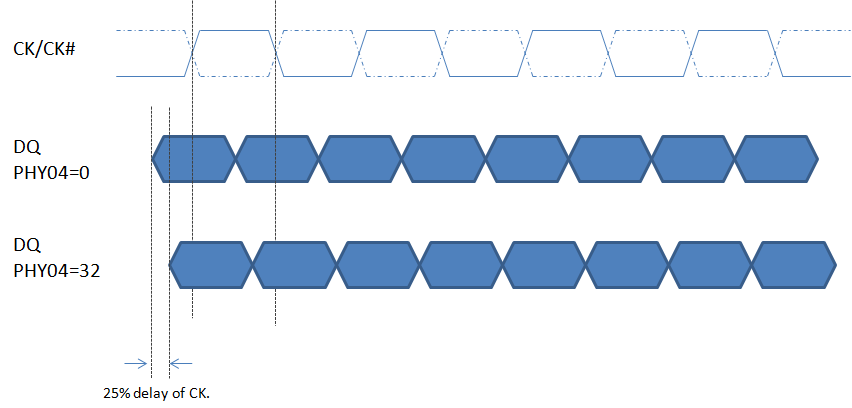

So if you want to delay the signal 25 ms, you need to set DDRMC_PHY04[DLL_WRITE_D] = 0x20 = 32

Numer of delay elemets DLL_WRITE_DL/128 * ENCODER = 32/128 * 100 = 25

This means internally 25 delay elements (of 1ms) will be used to delay the signal 25ms

In conclusion you still need to set DDRMC_PHY04[DLL_WRITE_D] to express the percentage (DLL_WRITE_D/128) you want to delay the output signal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Juan-san,

Thank you for reply.

In auto configure mode, user set as following;

PHY03(DLL_START_POINT) should be set 0x04.

target delay is calculated as below;

PHY04_DLL_WRITE_DL/128 * ENCODER. (ENCODER is DLL_LOCK_VALUE)

Is it correct? Sorry, I could not understand which register is ENCODER...

Best Regards

Taku.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that is correct but ENCODER is not the DLL_LOCK_VALUE

It is related to but not the same. Basically you don't need to worry about this ENCODER number. It is internal data and It should be transparent for you in auto-configure mode.

At the end you only need to tell what is the percentage of one-cycle delay you want.

So if you want 50% then DLL_WRITE_DL = 64 ===> DLL_WRITE_DL/128 = 0.5

25% then DLL_WRITE_DL = 32 ===> DLL_WRITE_DL/128 = 0.25

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Juan-san,

Thank you. I understand it.

PHY04 can configure the how delay the data write from clock. if clock period is 10ns and would like to make 2.5ns delay (25%delay). user should set this register as 0x20.

If my understanding is not correct, could you correct it?

Best Regards

Taku.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that's correct

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Jua-san,

Thank you!

Best Regards

Taku

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Keisuke,

At this time, the engineer most familiar with Vybrid is travelling for training internationally. When he is next available, I will ask him to review this inquiry and provide feedback.

Regards,

Timesys Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

timesyssupport can you help on this case?