- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: FlashNvM how to verify ?

FlashNvM how to verify ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Here am using "flash_partitioning_s32k148" in which

.PFlashBase = 0x00000000U, /* Base address of Program Flash block */

.PFlashSize = 0x00180000U, /* Size of Program Flash block */

.DFlashBase = 0x10000000U, /* Base address of Data Flash block */

.EERAMBase = 0x14000000U, /* Base address of FlexRAM block */

after running the example am able to see source buffer data(o to 256) at 17F000 address which is last sector of P-Flash and also at 0x14000000U 32bits of data(0,1,2,3)

As I understand after partitioning if we write anything to EERAM it has to write in NVM space at some address but how to verify written values in NvM ? here using memory window at 0x10000000U(D-Flash base address) am not seeing any data.

Also is their any specific reason for writing only 32bits of data at 0x14000000U ?, what happens if we write whole 256bytes source buffer data(0-256) ?.

Here am able to write 256bytes at 0x14000000U but not sure what is the effect of it, & how it will effect on endurance cycle.

Please do the needful

Thanks in advance

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

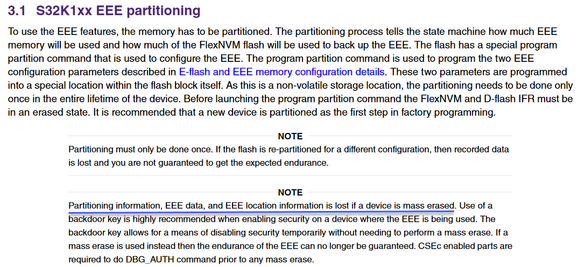

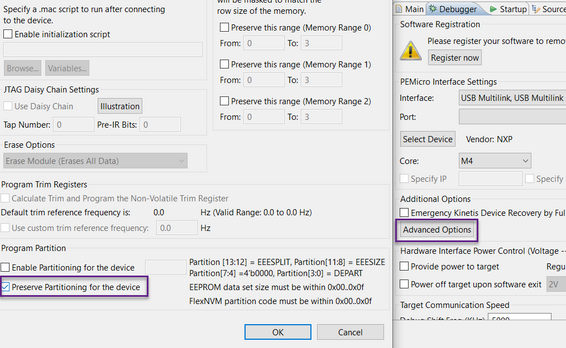

As you can see in the application note:

If you debug with PE Micro in S32DS, you can preserve the partitioning.

The function of the flash driver is blocking, but the MCU allows using CCIF interrupt on completion of the flash operation.

You would need to write your own function and make sure the FlexNVM block is not accessed during the EEPROM background operation.

Best regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Actually, respectfully I don't think that's the problem. I was able to load the values from flash into a variable to test against, and that worked fine. There's something else here, adding any additional lines of code doesn't matter what it does seems to affect other parts of the program.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Glenn,

Is this related to the thread?

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Saitej,

When EEERDY = 1, any data written to FlexRAM are backed up in FlexNVM, but the user does not have access to FlexNVM used as EEE Backup.

It can be verified after a power-on reset, when EEERDY = 1 again, the FlexRAM will contain all the data previously stored to the EEPROM.

Please refer to AN11983 Using the S32K1xx EEPROM Functionality

https://www.nxp.com/docs/en/application-note/AN11983.pdf

I believe it is all explained there.

3.6.1 EEE writes

6 S32K1xx new quick write mode

7 S32K1xx EEPROM endurance

To answer your question,

You can write up to 32b at a time, every write clears the CCIF flag and you need to wait until the flag is set again.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply.

To answer your question,

You can write up to 32b at a time, every write clears the CCIF flag and you need to wait until the flag is set again.

- Yes I see even in example it is writing 32bits only, but we have a scenario to write more than 32bits at a time, for that do we need to call write function as many times as required ?

- In ideal case what is the estimated time consumed for one write function ?

- Also at what location all this Flex NVM partition configuration is stored(considering the same example), would like to preserve them in my debug setting please guide me on this too.

Thanks in advance and please do the need full.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You need to wait until the previous 32b write is complete which is indicated by the CCIF flag.

The execution time is specified in the datasheet, rev.13.

Table 35. Flash command timing specifications for S32K14x series

A write function will have some overhead and this depends on the CPU clock frequency mainly.

The partition configuration is stored in the Flash IFR which is not accessible.

However, the DEPART value is loaded during the reset sequence to the SIM_FCFG1[DEPART] register.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- The partition configuration is stored in the Flash IFR which is not accessible

okay but every time I debug am loosing the partition config and data in E-flash, which locations i need to preserve to avoid this

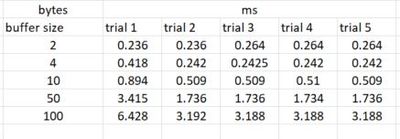

Also here I see write function is consuming too much , is their any way to do it background ? here I see all are blocking calls. for writing 100bytes of data it consumes nearly 6.5ms for first time later it takes 3.2ms still it is high.

Testing using logic analyser by toggling the gpio before and after write function.

Main code:

for(i=0;i<=50;i++)

{

write[i]=i;

}

NvM_Init();

Dio_SetSignal(E_DIO_CH_LED2_DOH, DIO_HIGH );

NvM_WriteDataInSync( 0x14000000, write, sizeof(write), C_TRUE );

Dio_SetSignal(E_DIO_CH_LED2_DOH, DIO_LOW );

Write function:

address = EEEBASEADDRESS; /*TODO: Need to assign proper address*/

if(STATUS_SUCCESS != FLASH_DRV_EEEWrite(&flashSSDConfig, address, (uint32_t)size_u16, ramaddr_pu8))

{

rVal = E_Error;

}

if((verif_flag_u8) && (rVal == E_Ok))

{

while(size_u16>0)

{

/* Verify the written data */

if (*((uint8_t *)ramaddr_pu8) != *((uint8_t *)address))

{

/* Failed to write data to EEPROM */

rVal = E_Error;

}

address += 1U;

ramaddr_pu8 += 1U;

size_u16 -= 1U;

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As you can see in the application note:

If you debug with PE Micro in S32DS, you can preserve the partitioning.

The function of the flash driver is blocking, but the MCU allows using CCIF interrupt on completion of the flash operation.

You would need to write your own function and make sure the FlexNVM block is not accessed during the EEPROM background operation.

Best regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- I assume CCIF_Handler() is triggered for every 32bits writing so, we have a situation of writing 100bytes in this case it has to execute CCIF_Handler() for 50 times ideally, but am seeing it got executed 65 times. any clue ?

- Here I see in call back function interrupt is enabled and in handler function it is disabled again, what is the need of enabling and disabling again and again, in generic the ISR need to execute at once when interrupt occurs, but if I comment out disabling interrupt it is getting struck in CCIF_Handler()

void CCIF_Handler(void)

{

/* Disable Flash Command Complete interrupt */

FTFx_FCNFG &= (~FTFx_FCNFG_CCIE_MASK);

x = x+1;

return;

}

START_FUNCTION_DEFINITION_RAMSECTION

void CCIF_Callback(void)

{

/* Enable interrupt for Flash Command Complete */

if ((FTFx_FCNFG & FTFx_FCNFG_CCIE_MASK) == 0u)

{

FTFx_FCNFG |= FTFx_FCNFG_CCIE_MASK;

}

}

END_FUNCTION_DEFINITION_RAMSECTION

- On S32_NVIC->ISPR registers also not seen updating as when am trying to get INT_SYS_GetPending() or INT_SYS_ClearPending()

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The CCIF flag is cleared by any 8b, 16b or 32b write to the EEPROM (FlexRAM) .

100 bytes written in 4byte words is 25 writes, if I'm not mistaken.

The driver must enable the CCIF interrupt once the CCIF has been cleared.

And it must be disabled as soon as the operation is finished and CCIF is set.

Otherwise the interrupt will became active again.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I have mistaken it has to call CCIF interrupt 25 times, but if you keep a counter in CCIF_Handler() it shows CCIF_Handler called for 54 times for 100 bytes & for 200 bytes it called for 65+ times.

Also why we are not able to see updates on S32_NVIC->ISPR registers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The ISPR bit would be set if the interrupt was pending.

I guess the interrupt becomes active immediately so you don't see the ISPR bit set.

Please make sure that CCIF == 0 when the CCIF interrupt gets enabled.

Thank you,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply

Okay !

Also is their any comment on time consumption of flash driver write function, here I see almost 3.2ms for 100 bytes of data writing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I mentioned, the execution time is specified in the datasheet, this is the time during which CCIF reads 0.

Then there is some CPU overhead of the driver that is not specified.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any update !

am using integrated freertos which is not allowing me to write data using "FLASH_DRV_EEEWrite" which is blocking function call.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

any update please