- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

AN12522 states about ECC RAM:

- 2.2 Used ECC algorithm

The ECC implementation for the SRAM uses a Modified Hamming Code scheme with 40-bit check base that consists of 32-bits of data plus 8-parity bits.

Clearly RAM initialization should be done in 32-bits aligned word writes. I thought that initializing RAM writing byte by byte could easily trigger ECC error flags set in ERM (I'm using S32K144 and S32K148). But S32DS startup code indeed seems initializing RAM byte by byte:

uint8_t * data_ram;

uint8_t * code_ram;

uint8_t * bss_start;

...

/* Copy initialized data from ROM to RAM */

while (data_rom_end != data_rom)

{

*data_ram = *data_rom;

data_ram++;

data_rom++;

}

/* Copy functions from ROM to RAM */

while (code_rom_end != code_rom)

{

*code_ram = *code_rom;

code_ram++;

code_rom++;

}

/* Clear the zero-initialized data section */

while(bss_end != bss_start)

{

*bss_start = 0;

bss_start++;

}

Since it is told that out of power on SRAM isn't initialized and ECC bits are most likely not OK, I decided to check it. Cloning flash Debug configuration and making debugger not reload flash but connect without reset to running MCU, powering MCU down for a while, then powering on, connecting debugger and inspecting ERM status registers I found that indeed status bits do report ECC problems. Then I added loop code into startup_S32K144.S to step through the rest of startup and figuring out what actually triggers ECC flags. ECC errors start flipping from the first byte by byte initialization loop.

My question are here. "Modified Hamming Code scheme with 40-bit check base that consists of 32-bits of data plus 8-parity bits.". Does it mean that 1) every RAM byte has dedicated 8/4=2 ECC bits? 2) Is it safe to write just single byte to uninitialized RAM DWORD and expect to read the same byte value after writing remaining 3 bytes of the same RAM DWORD?

Thanks

Edward

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward,

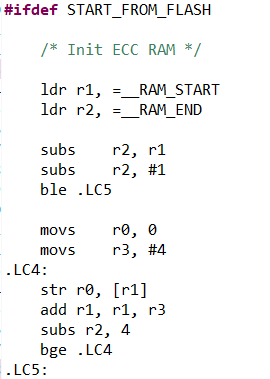

The SRAM ECC is initialized in the startup_S32K144.S file and this is done by 32b writes.

I was able to reproduce your test results only when I removed the ECC initialization.

I don't know which version of S32DS you are using.

As far as I know, the first version of the startup code didn't include the ECC initialization, it was added later.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward,

The SRAM ECC is initialized in the startup_S32K144.S file and this is done by 32b writes.

I was able to reproduce your test results only when I removed the ECC initialization.

I don't know which version of S32DS you are using.

As far as I know, the first version of the startup code didn't include the ECC initialization, it was added later.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

thank You! I started from creating new "S32DS Project from Example". Example projects seem being not updated and use old startup files. Creating new "S32DS Application Project" I see what you provided in startup*.S file.

Initializing only used locations could make startup bit faster. As well ECC handler could be used to detect unexpected accesses to locations which shouldn't be used (not initialized locations)... But initializing all available RAM is quite good as well.

Regards,

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward,

I see, the non-SDK examples haven't been updated.

Let me report that.

Thank you,

BR, Daniel