- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

QSPI Boot fail to load image application after NOR flashing to SRAM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP Team,

I have problems with the NOR Flash to SRAM process when using the QSPI boot process.

The same application works finds when it is booted from SD Card or by the S32 Debug Probe. When the same application image is flashed by serial, starting the QSPI to Boot from NOR flash to SRAM the code is partially executed and stops.

I got from the manufacturer of the SoM the QSPI config to assure that the image application is loaded respecting the 500ms, (the code is 2.6 Mb).

The same code that is able to start when SD Card or S32 Debug Probe is used, presents that behaviour start and stop. The same procedure using an UART example using the NOR flash to SRAM booting works without problem.

Are they conditions to assure that the image application is able to start and execute at the same level as from Sd Card or S32 Debug?

I see the same problems in the forum but I don't see a definitive answer for most of them.

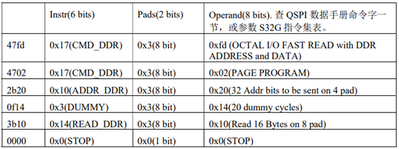

The QSPI bin I programmed using the reference from the SoM provider, and it is the same from one of the documents in the forum (S32G_QSPINOR_定制_20211125_V3).

Thank you in advance for you support.

Hugo

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @ARM_Kami @alejandro_e ,

Has the issue been solved?

We had the same Nor Flash used on our board and the S32G3 has issue booting from nor flash.

Could you share the solution is possible?

Thanks in advance.

Regards,

Jalsey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @JalseyXie,

We had a long discussion and at the end I understood that the problem was not exactly at boot time, it was related to the SPI Write function. I am not aware if @ARM_Kami was able to solve the problem.

You can create a new post in this community and one of my colleagues or myself can help you.

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @alejandro_e ,

I've created a post regarding this issue already:

Re: S32G399A Fail to Boot from NOR Flash - NXP Community

Regards,

Jalsey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @JalseyXie,

I see you are already being helped by one of my colleagues.

Thanks for letting me know.

Best regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @ARM_Kami,

From the information you sent I am assuming the following:

- You are using a custom board, not a RDB2/RDB3

- You are using a MT35XU256ABA1G12-0AAT as the QSPI flash of your board, which is the one presented in the document you mentioned.

- We can be sure that the IVT (without the QSPI parameters) is correctly configured since you can boot from SD card.

- The only difference in the IVT for SD card and QSPI is the qspi parameters binary.

Please help me confirming if my assumptions are correct.

Also please help me with the following information:

- are you using an S32G2 or an S32G3?

- can you share your QSPI configuration from S32 Desing studio?

- Is this the first time using this QSPI flash as a boot source?

Thanks in advance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alejandro,

Answereing your questions:

- You are using a custom board, not a RDB2/RDB3-> I'm using a custom board.

- You are using a MT35XU256ABA1G12-0AAT as the QSPI flash of your board, which is the one presented in the document you mentioned. -> I am using a similar NOR Flash from the same provider (Same instructions set; bigger capacity).

- We can be sure that the IVT (without the QSPI parameters) is correctly configured since you can boot from SD card.-> Yes, same application image by SD card runs without problems.

- The only difference in the IVT for SD card and QSPI is the qspi parameters binary. -> Yes, even adding or not the DCD config to the IVT has the same effect.

Please help me confirming if my assumptions are correct.

Also please help me with the following information:

- are you using an S32G2 or an S32G3? -> I'm using a S32G274A

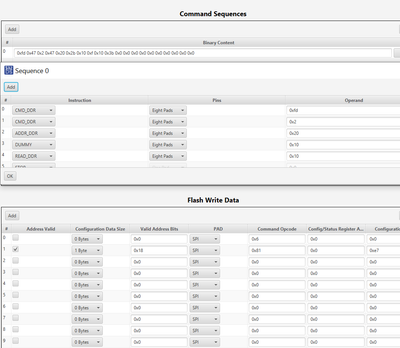

- can you share your QSPI configuration from S32 Desing studio?->Yes, I will share it.

- Is this the first time using this QSPI flash as a boot source?->No, we used with "small" examples and this works but never with the aapplication image.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @ARM_Kami,

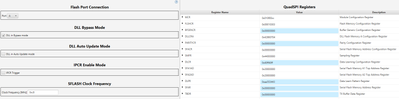

Thanks a lot for the information. I was checking the guide you referenced and I see the suggested changes in some registers you have modified in the QSPI parameters you just sent. However, there are some registers I did not see mentioned in the guide but were modified:

I notices that this register was mentioned in a Linux related patch, for BSP30, my understanding is that it does not need to be changed for the QSPI parameters used for Boot ROM.

For the following registers, can you provide more information as why you changed them? since I cannot access the memory documentation.

Also, have you checked the QSPI lines in the board with an oscilloscope? if so, can you share the signals you see in the QSPI lines or if you don't see anything at all?

Thanks in advance for the information.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alejandro,

I created the file for the QSPI config based on info from the SoM provider, they use a similar config to boot Yocto based system, (by similar I mean they don't use the nxp IDE to program their system).

When I saw the resulting file, this was the same as the one in the reference I quote.

the note about "However, there are some registers I did not see mentioned in the guide but were modified":

In the NXP ide the setting as you saw them are:

As I mentioned it ia custom board, using a SoM, I don't have the option to instrument it to get the requested signals.

About the " For the following registers, can you provide more information as why you changed them? since I cannot access the memory documentation. " => The changes I did were based on the info from the SoM provider.

And they are the same as in the quoted ref.:

The QSPI config. are confirmed to work in a linux system.

The 500 ms timeout doesn't seem to be a problem for the code size loaded in SRAM (2.6Mb).

Do we have a way to confirm that the code is completed loaded? a flag to confirm?

Do we have further contrains about the use of NOR Flash loading to SRAM when using Ethernet, SPI, FreeRTOS?

If only the QSPI config. is the key for being able to boot from NOR Flash please provide further support.

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @ARM_Kami,

I think there might be a confusion, I was asking why the change in the registers: MDIS, PPWB, TPADA1 and TPADA2, since I don't see those registers mentioned in the guide (1399906). I checked your binary in S32DS and saw the changes. To reduce the problem, please share the following information:

- RCON word value

- Are you using parallel RCON (dip switches) or serial RCON (EEPROM memory)?

- I understand you obtained your board from a manufacturer, what is the brand and model of the board?

- With your last message I understand that the register configuration and the LUT sequence you are using have been tested with Linux during runtime, is that correct?

- Comparing one of the available configurations with yours I notices that de padded part is in 0xFF in yours and it is 0x00 in one of the provided by us, on the right is your configuration and on the left is one of the available after isntalling S32DS:

- Did you changed this deliberately?

- When you use the flash tool, what is the result?

- To check if the chip is loading the full image in less than 500ms you can perform some tests:

- You can monitor the RESET_B pin with an oscilloscope and check the waveform

- You can compile a simple application, like a Blink LED, flash it and check if the behavior changes.

- You can monitor the consumption of the board and compare it with the configuration you know are working, like SD card.

Let me know if you find this information useful and please share the results of the tests in case you are able to perform them.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @ARM_Kami,

You mentioned: "The result is the that the code seems to be (partially) loaded, executes part of it and then stops at the beginning during the system initialization"

Can you share the steps you follow the flash memory? with screenshots please. I want to confirm the flashing process is working correctly before checking the boot.

Can you elaborate more about this "executes part of it and then stops at the beginning during the system initialization", how did you came to that conclusion? what indicators of the chip/board being ON did you see?

Were you able to perform one of the test I proposed to check if the chip is actually booting?

You mentioned that your are using parallel RCON, how are you writing the 32 bit word in the EEPROM memory?

You mention that your board is based miriac-sbc-s32g274a, can you please contact them in parallel? since they may already have the information on how to fix this issue.

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I added UART messsages in different parts of the code to check where the this stops its execution. So I am comparing the expected answer between SD Card / Flashing by S32 Debug Probe / NOR Flash.

If the code was not booting I would not being able to see any message from UART.

I have already contacted the SoM provider, they provided reference C code that I used to setup the QSPI the one I shared, but they are not NXP SW users and their application works under yocto using an U-boot.

If you saw the board and SoM info the combination of dipswitch positions allows to use the serial to program the NOR memmory using the S32 FlashTools.

Please provide a mail to share the requested info.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @alejandro_e and @ARM_Kami

Has the issue been solved?

We had the same Nor Flash used on our board and the S32G3 has issue booting from nor flash.

Could you share the solution is possible?

Thanks in advance.

Regards,

Jalsey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The issue has not been solved, I didn't continue with it due new assigments.

I identified an issue with the spi communication with one of the components causing a hardfault. Again issue not observed when booting from SD Card or by directly flash using the S32 debug probe for the same application code.

The spi uses DMA and it seems a clock configuration, there is no spi signals when the code boots from NOR flash.

Regards,

Hugo

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hugo,

Thanks for the information.

We successfully boot from Nor Flash by using the QSPI parameters you shared in this post.

Regards,

Jalsey