- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- ソフトウェア・フォーラム

- :

- S32 デザインスタジオ

- :

- Re: Machine check exceptions in MPC5748G

Machine check exceptions in MPC5748G

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everybody!

Now and then I encounter situations where a machine check exception results in the program getting stuck in IVOR1_Vector which has no implementation.

I would very much like to be able to analyze the exception information to track down the reason why this is happening.

More specifically I would like to know:

1) I can't seem to find the exception registers (MCSR in particular) in the register lists, are they at all available to be read in Design Studio?

2) Is there some sort of example code that actually does something, that can replace the default IVOR1_Vector loop?

Any information and tips would be highly appreciated.

Best Regards

Ville

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ville,

1) Yes, you are correct, MSCR is not in register list. But there is a workaround you can use. While debugging, click on Display selected console icon and choose powerpc-eabivle-gdb and write to the console command monitor spr 572t.

MCSR is marked as special purpose register 572.

2) Look at the example in the attachment. This simple example shows, how to create your own IVOR1 handler. Also you can look at the following example, which is created for GHS and also shows, how to create IVOR1 handler.

Example MPC5777C-1b+2b_RAM_ECC_error_injection GHS614

If you have any other question, please feel free to write me back.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ville,

1) Yes, you are correct, MSCR is not in register list. But there is a workaround you can use. While debugging, click on Display selected console icon and choose powerpc-eabivle-gdb and write to the console command monitor spr 572t.

MCSR is marked as special purpose register 572.

2) Look at the example in the attachment. This simple example shows, how to create your own IVOR1 handler. Also you can look at the following example, which is created for GHS and also shows, how to create IVOR1 handler.

Example MPC5777C-1b+2b_RAM_ECC_error_injection GHS614

If you have any other question, please feel free to write me back.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

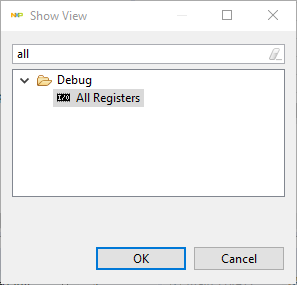

To view all registers of the MCU, including the ESR registers you could also use the "All registers" debug view.

Window --> Show View --> Other...

using S32DS 2017.R1

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi , Martin

Your project "MPC5748G-IVOR1_ExceptionHandler-S32DS "is really helpful. But would you give me an example about how to get out of the "IVOR1_Exception_Handler" ,and back to the "int main(void)" again? My project is on the MPC5748G.

Thanks,

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have created new example for you, because I found an error in previous example I had shared here. In the previous example, IVOR1 is not caused by SMPU, but by reading uninitialized SRAM. New example shows, how to handle IVOR2 exception cause by SMPU. Please look and carefully read my comments into the example.

If you have any question about the example, please write me back.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have a similar problem.

MPC574XX uSDHC_DriverIRQHandler ()

These two connections are the problems I raised, but there is no good solution, please give me a look

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

I have run you IVOR2_Exception project on my MPC5748G EVB. But it seems it will cause a IVOR1 error.

When I suspend the project, it will became as the figure shows. I try to add a breakpoint in the function of IVOR2_Exception_Handler, but it seems that the project didn't run into the IVOR2_Exception_Handler .

Is there something that I misunderstanding?

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I did not test the project via PEMicro debugger. I used Lauterbach and it works correct. I will try it on Monday and will write you back.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

Thanks for your help!

Regards,

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I found the issue. If you step the code, IVOR2 occurs, but if you run the code, IVOR1 occurs. I am not sure, why this behavior becomes, but it could be possibly cause by some synchronization. Please give me a time, I will update the example.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

Thank you for your help.

Besides, I have a question about the register SMPU.RGDn. For example , UTest use the SMPU_0.RGD[0], BAF use the SMPU_0.RGD[1], HSM code use the SMPU_0.RGD[2]...When config the SRAM(768kB-4kB), use the SMPU_1.RGD[0],when config the SRAM(last 4kB), use the SMPU_1.RGD[1].

I know when to choose SMPU_0 or SMPU_1, but how about the "n" for RGD[n]? I can not found any information in the reference manual. Does it matter if the "n" have different value?

Regards,

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Martin,

Thanks for the whole information. I need small clarification is possible:

a) Statement (in MPC5777CRM.pdf says) : When a master tried to access the address space that is restricted for it by MPU Region descriptor, the MPU generates "PROTECTION_ERROR".

b) So, can I assume that this "PROTECTION_ERROR" generation is nothing but updating the EARn, EDRn registers of MPU.

c) Also, assume the MACHINE_CHECK exception is triggered by the MASTER that tried to access the mem_address not that is protected from it. So, there is no MPU intervention in generating the MACHINE CHECK exception.

So please let me know on this if possible. Eager to here from you.

Thank you in advance.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Martin,

Your example is very helpful for me, but there is something which I do not understand. Your IVORx_Handlers always start with following code:

| IVOR4_Handler: prologue: e_stwu r1,-0x50 (r1) # Create stack frame and store back chain |

My question is: What is the value loaded inside r1 before the execution of e_stwu ?

Where can I find some additional information regarding the values loaded inside register r0-r31 when interrupt service routine is called?

Best regards,

Yulian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Yulian,

r1 is used as a stack pointer. Before interrupt is executed, it is necessary to save same register values and it is necessary to create stack frame for the values. So the value stored in r1 is current top of the stack address.

Please see the document in the attachment. There are some useful information about registers.

If you have any other questions, please feel free to write me back.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

Sorry to interrupt you.

I add a breakpoint in IVOR1_Exception_Handler, the project would stop into it when running the code.

But if I add a breakpoint in IVOR2_Exception_Handler, the project would not stop when running the code.

So it seems the IVOR1_Exception (machine check) would happen while IVOR2_Exception (data storage) did not happen?

You said that "IVOR1 is not caused by SMPU, but by reading uninitialized SRAM."

I got a little puzzled.

I use the SMPU module to set last 4kB read only for M0(Z4a). And then I write the one the last 4kB.

And then the IVOR1 happened while the IVOR2 not.

I also run the code " i = *(unsigned int *)0x400bf000; *(unsigned int *)0x400bf000 = 0xAABBCCDD; " without setting any SMPU. It would run normally.

Then I thought IVOR1 was caused by SMPU.

Can you help me to understand those codes?

Thanks!

Regards,

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang,

sorry for that confusion.

I shared here example called MPC5748G-IVOR1_ExceptionHandler-S32DS.zip. In this example I have incorrectly initialized RAM (only 256KB from 768KB is initialize - look at the linker file). But SMPU is configured to protect last 4KB (764KB-768KB). So in this case there the problem is on the line i = *(unsigned int *)0x400bf000; because I read RAM, which is not initialized, ECC problem could happen and it causes IVOR1 exception (but it can behave randomly).

So I created second example and there is the problem which I describe above. IVOR2 occurs when you single step over this line: *(unsigned int *)0x400bf000 = 0xAABBCCDD; and IVOR1 occurs when you do not single step.

Obviously writing to protected area can create IVOR1 and also IVOR2 exception. I am not sure, why it behaves this way, but it could be caused because of synchronization (I will study this problem later).

So the behavior you describe is correct. You should get IVOR1 exception when you do not single step asm code on line *(unsigned int *)0x400bf000 = 0xAABBCCDD.

I hope I clarified it a little bit. If you have any other question, please feel free to write me back.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

Your reply helps me a lot. mem.id is different between two example.

Thanks you!

Infact, I could not have IVOR2 occurs both in "step into (F5)" mode and "resume" mode with S32 Design Studio.

All have IVOR1 occurs.

Maybe I have something configurations different from you. I am not quite sure.

I will try to find what's wrong with me tomorrow.

Thank you for your help!

Regards,

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang,

I am also not able to get IVOR2 exception using PEMicro and S32DS Debugger. This occurs only if I use Lauterbach debugger and because I use only Lauterbach when I write examples, I thought SMPU generates IVOR2 (what a mistake :-)).

So I think you do not have to look for the mistake, because there is not any one. But this example can show you, how to handle IVOR2 (it is little bit different than IVOR1), when you will need it.

Regards,

Martin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

Your IVOR1 and IVOR2 examples are helpful for me.

Thanks!

Regards,

Qiang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Martin

It works well now.

Thank you for your help!

Regards,

Qiang