- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- ソフトウェア・フォーラム

- :

- S32 デザインスタジオ

- :

- Re: How can i use the same variables in different sub-project using S32DS?

How can i use the same variables in different sub-project using S32DS?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

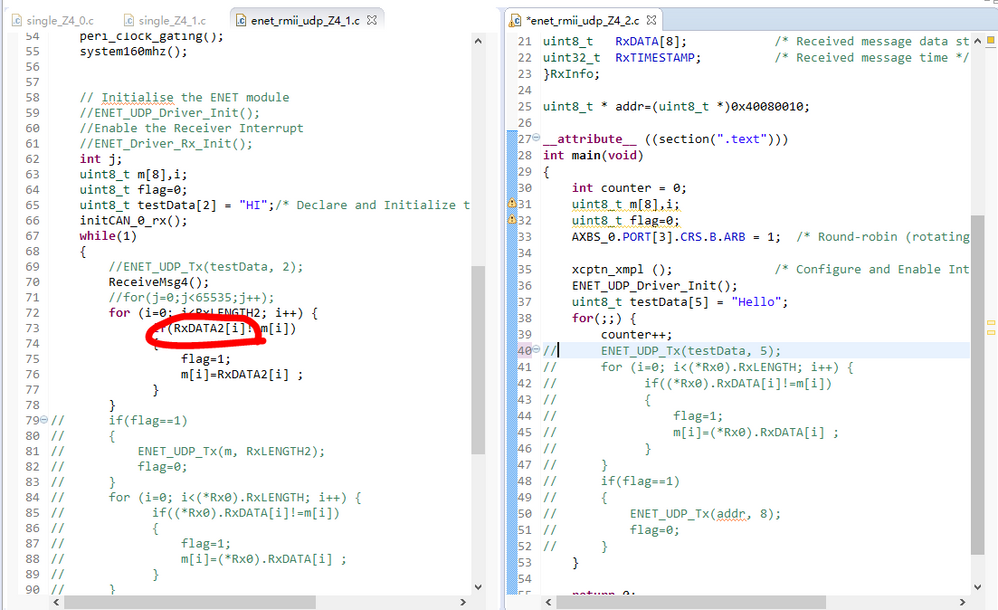

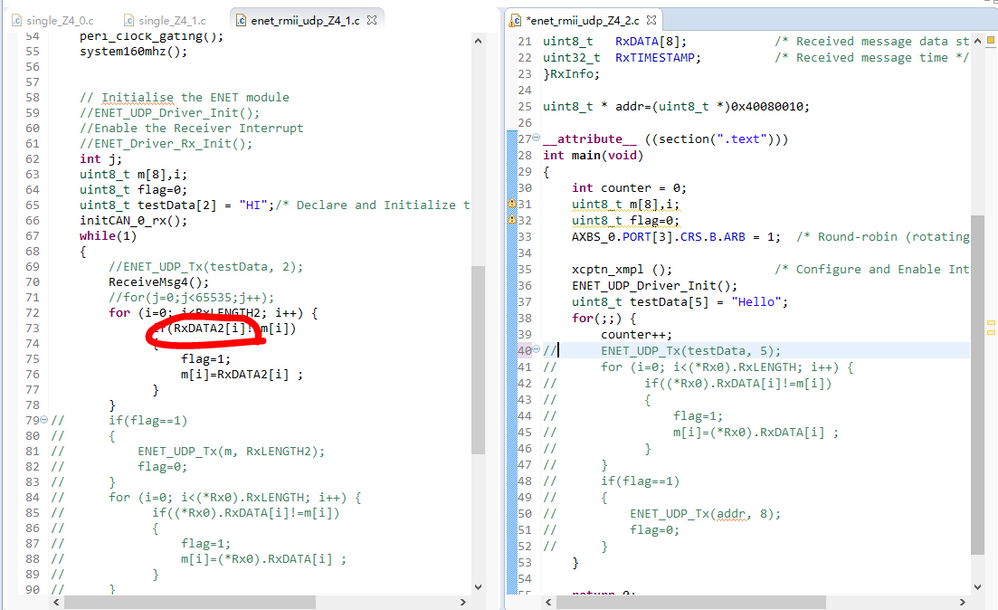

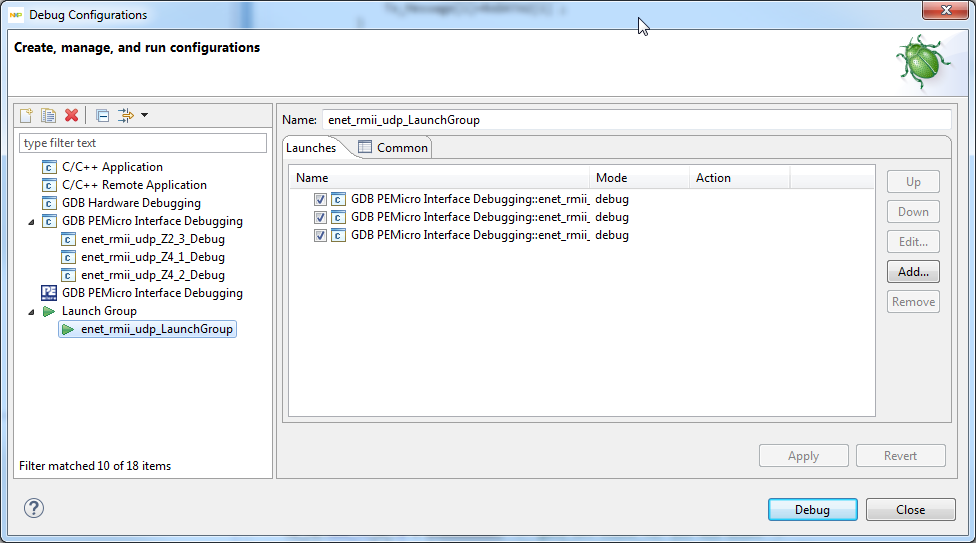

I want to use core0 to receive some CAN data,and then transmit these data to the terminal by using core1.So i write some code in these two sub-project,how can i transmit the data which i received in project Z4_1 in project Z4_2?

My development board is devkit-mpc5748g。

The following attachment is my project!

Regards

Original Attachment has been moved to: enet_rmii_udp.rar

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

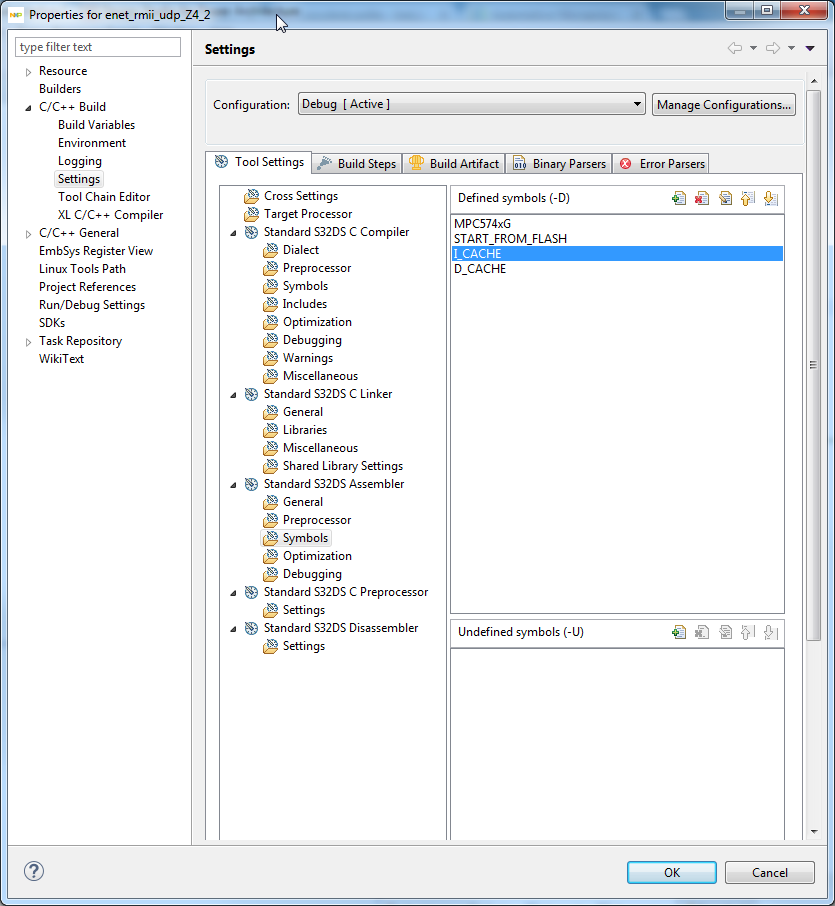

this is really strange. But technically - there is only one Tx_Message instance on address 0x400B8090 - as you can see in your debug window. I can't reproduce it with test data. You have enabled I_CAHE and D_CACHE for Z4_2 core - try to remove these defines from your project settings for test:

I also can't see any difference on screenshots - may be I don't get the correct order. there are the very same data on picture #1 and #2 and different same data on #3 and #4.

Jiri

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

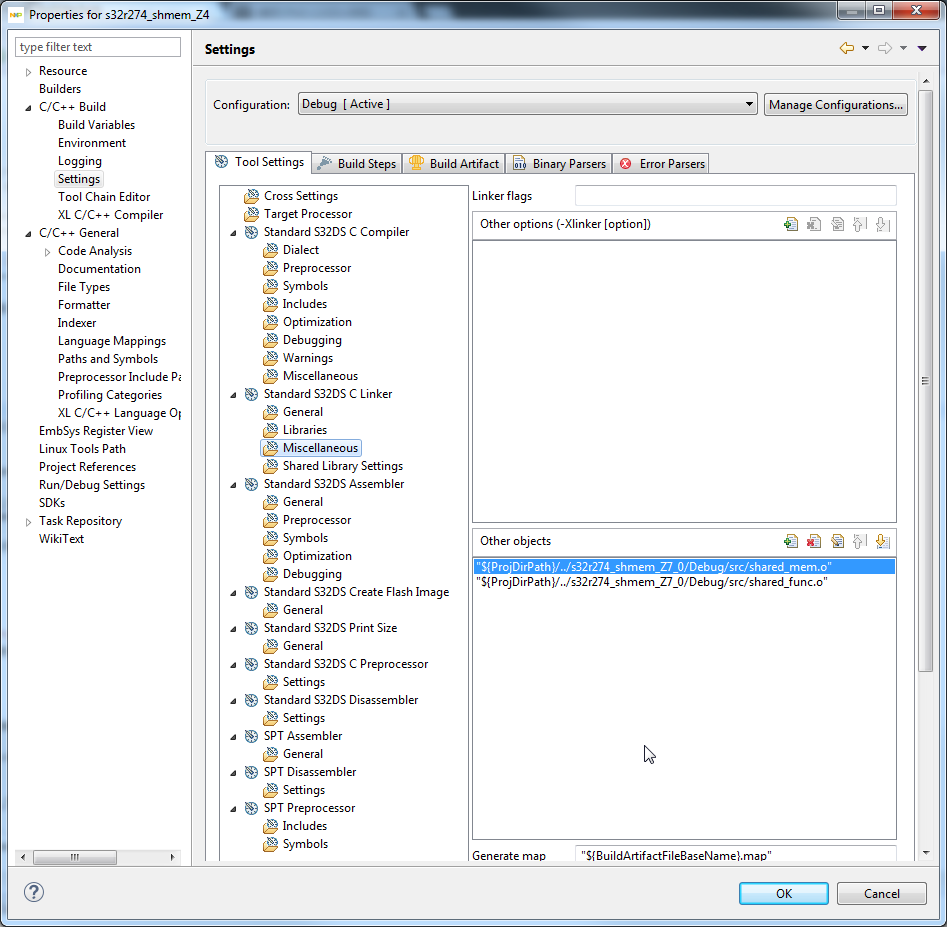

you can use shared memory. Here is example for multi-core shared memory usage:

https://community.nxp.com/docs/DOC-335344

Example is for S32R274, but you can use this technique for MPC5748G too.

Jiri

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Do i have to add the two files into all the sub-project?

In this example,only the z7_0 project contain the 'shared_mem' and the 'shared_func' file.

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

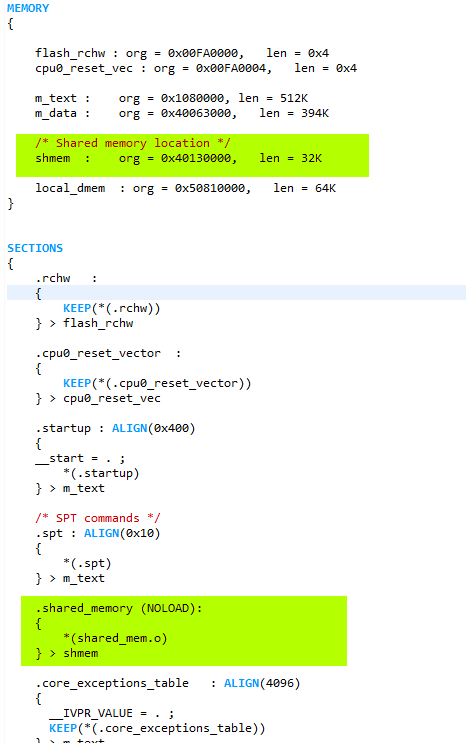

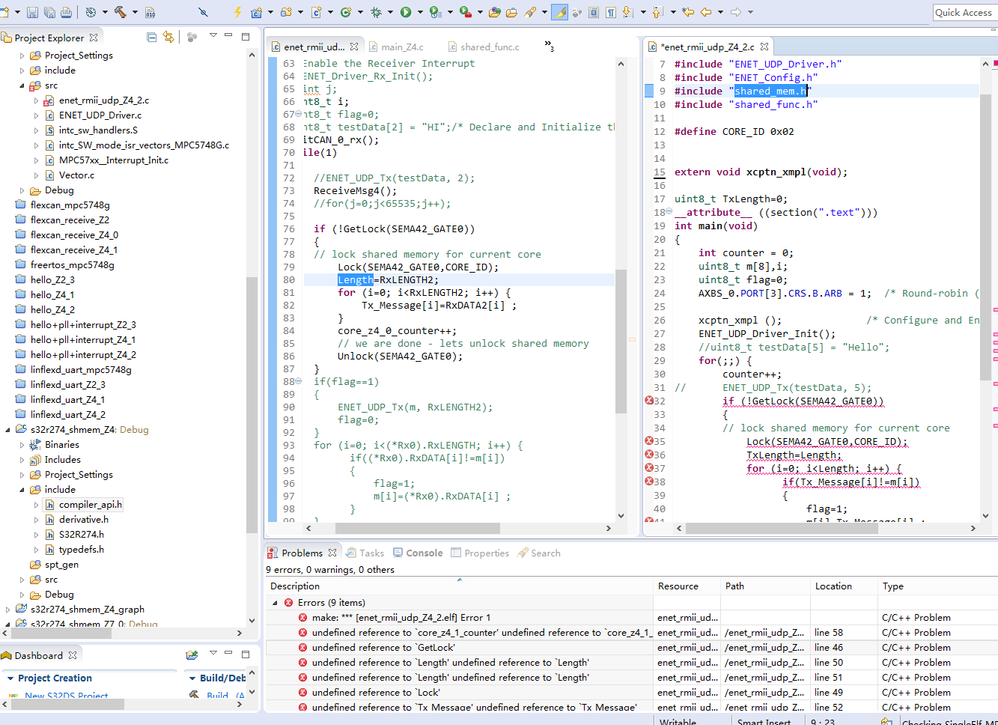

you also need to modify linker files for all cores. Please check the linker files in the example and your project (Your Project Name->Project_settings->Linker_files). You need to add path for shared objects (shared_mem.o and shared_func.o) into project settings (see screenshot bellow). Source codes - shared_mem.c and shared_func.c needs to be build by the firstly built core project (one of the cores is always build as the first and I can't find way how to change the build sequence - looks like that it is alphabetically sorted).

The basic idea is

- one memory space and starting address shared across cores (one instance for all cores) - technically linked shared_mem.o object on the very same address for each core

- usage semaphores for accessing shared memory (one instance per core) - technically linked shared_func.o on unique address for each core.

Here is linker file with added shared mem location:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jiri,

Thank you very much !

It works for me!

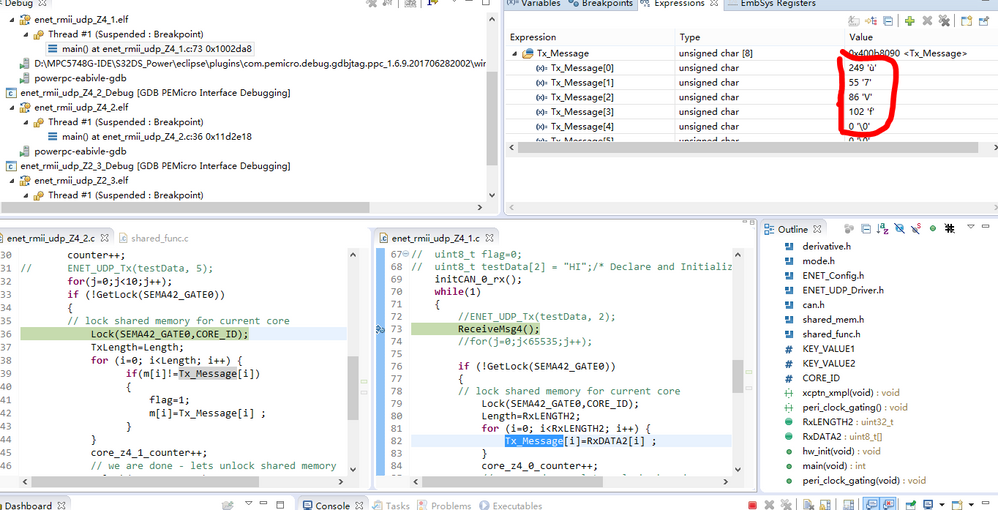

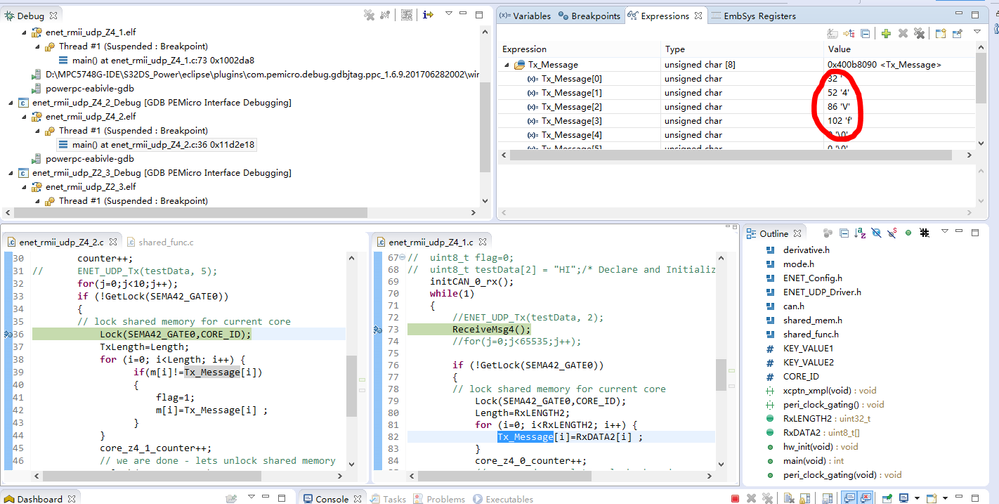

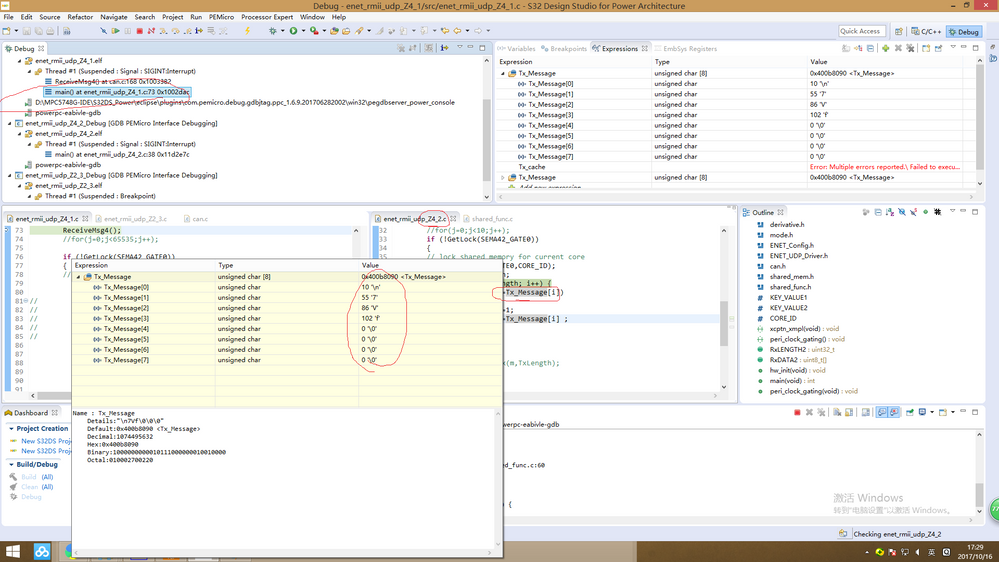

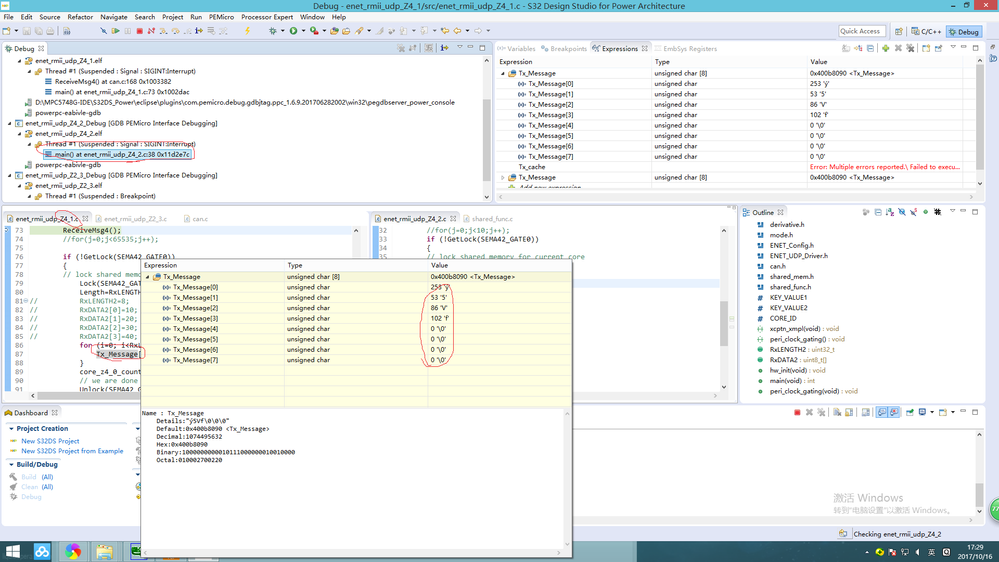

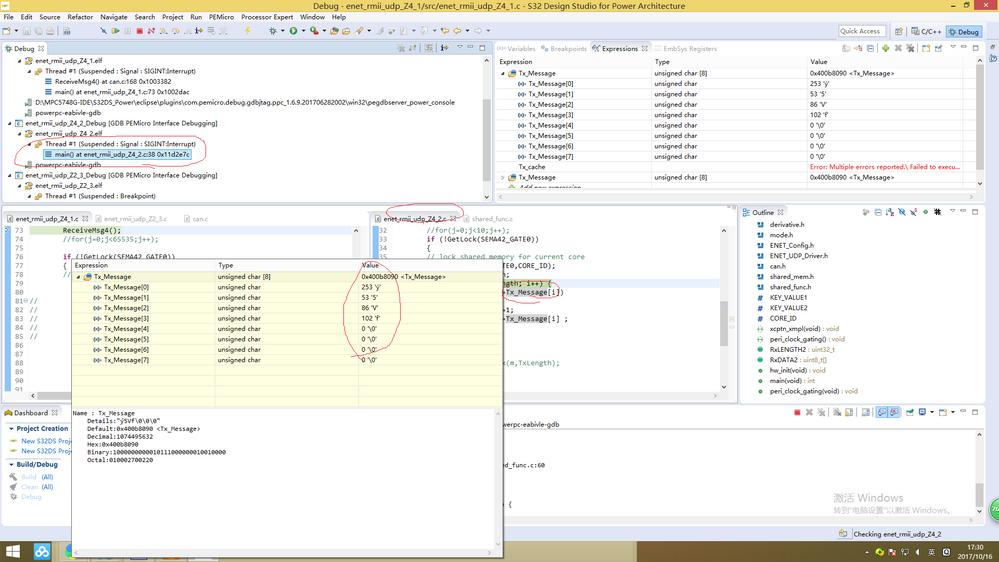

But i still have this problem.As the picture showed below,In project Z4_1,i have change the value of the Tx_Message which is a shared variable,but in project Z4_2,the value of the Tx_Message is still previous value,Why?How can i solve this problem?

Thanks

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There may be couple reasons. Are you unlocking shmem access? Do you have only one source code for shmem/shfunc in the Z2_3 project and for other cores is linked object file from Z2_3 core?

If you attach your update project - I'll look at it.

Jiri

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

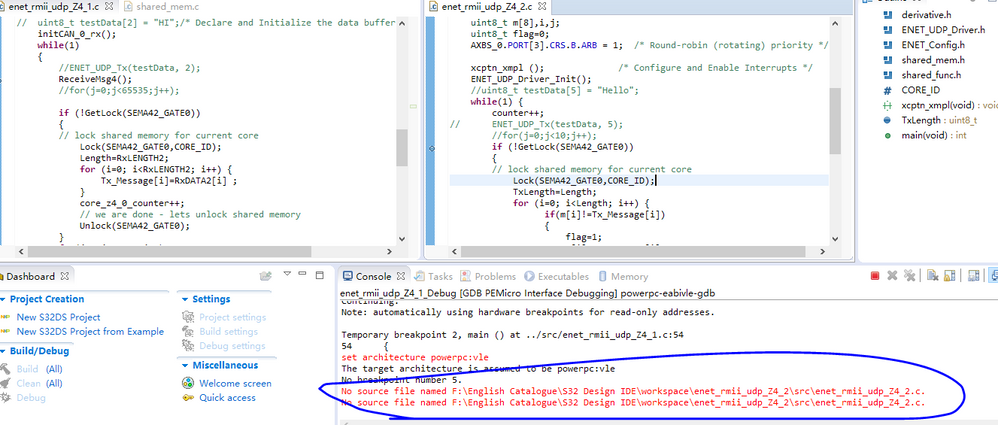

I still have a question that when i import a project,in debug process,if i want to set a breakpoint in Z4_2 project,it always can not be effective,and the console window shows these messages:

And the breakpoint in Z4_1 project is effective.

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have no issue about sources. Did you start debug session as a launch group?

Your issue also may be caused by spaces in the path - like "S32 Design IDE". You can try to locate your workspace in the path without spaces.

Jiri

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jiri,

Actually,in core0 ,i keep receiving data from CAN_0,and store the data in Tx_Message.In core1,i read the data in Tx_Message and transimit them by ENET.

My problem is that in core1,only the first data in Tx_Message can be read normally.When the data that core0 received changed,Tx_Message should also change.But in Z4_2 project,the Tx_Message didn't change.

For example,the data that core0 recevied first are{253,53,86,102},then the data changed to {10,55,86,102},the Tx_Message shoule change to{10,55,86,102}.But on debugging,if i choose the Z4_1 debug,the Tx_Message are{10,55,86,102}, if i choose the Z4_2 debug,the Tx_Message are still{253,53,86,102}.

The pictures below show the state

I dont't know why it happend.Please help me.

Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

this is really strange. But technically - there is only one Tx_Message instance on address 0x400B8090 - as you can see in your debug window. I can't reproduce it with test data. You have enabled I_CAHE and D_CACHE for Z4_2 core - try to remove these defines from your project settings for test:

I also can't see any difference on screenshots - may be I don't get the correct order. there are the very same data on picture #1 and #2 and different same data on #3 and #4.

Jiri

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jiri,

Thank you very much!

Disabling I_CAHE and D_CACHE for Z4_2 core works for me!

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I tested your project - and for me it is working normally. But I used test data only (no real message from ethernet).It is good idea to add some flag in the shared memory - like NewDataReady - and Core 2 should process incoming data only when new data is ready.

In attachment is project with test values.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jiri,

I have added these two files shared_mem and shared_func into my project.But i still have thses faults,do i have to make some other configuration?

Regards