- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Re: Why target reset failed using COP reset on S12XHY128

Why target reset failed using COP reset on S12XHY128

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I referred some questions and use COP reset to do my reset for bootloader like:

S12Z SW example of COP Watchdog Reset

I just wrote like this:

COPCTL = 0x41U;

/* Create COP reset */

ARMCOP = 0x00U;

I also tried like this:

//in board.c

COPCTL = 0x41U;

while(1);

//in .prm

/* use these definitions in plane of the vector table ('vectors') above */

VECTOR 0 _Startup /* reset vector: this is the default entry point for a C/C++ application. */

VECTOR 1 _Startup

VECTOR 2 _Startup

But it always shows "target reset failed"

And it didn't enter cop interrupt neither.

So any idea why it failed?

Thank you very much.

Kim

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

In fact, the COP reset didn’t fail.

The asynchronous reset like COP is not debuggable by BDM – The reset broke the BDM connection and debugger is simply confused from that.

Since the debugger probably tries to continue in communication with MCU, the final MCU mode after such reset is rather random = sometimes MCU reset to the normal single chip mode and sometimes to the special single chip mode where the final mode depends on BKGD pin value during the reset sequence.

Please use for example the LEDs for debugging the COP reset.

For example:

unsigned int i;

//function prototype of _Startup function (Start12.c)

void _Startup(void);

//******************************************************************************

// COP interurpt

//******************************************************************************

#pragma CODE_SEG NON_BANKED

interrupt 2 void COP_ISR(void)

{

DDRA = 0xff;

PORTA = 0x00; //LEDs on - show we entered the COP_ISR

for(i=0; i<60000; i++) //delay

{

asm nop;

}

PORTA = 0xff;

asm jmp _Startup; //jump to power-on reset vector

// !!! RTI instruction cannot be executed because this is not interrupt !!!

}

#pragma CODE_SEG DEFAULT

//******************************************************************************

// Main program

//******************************************************************************

void main(void) {

DDRA = 0xff;

PORTA = 0xff; //LEDs off

COPCTL = 0x47; //enable watchodg

for(;;) {} /* wait forever */

}Please be aware that external capacitance on reset pin may influence correct reset source recognition. For more details, please see https://community.nxp.com/docs/DOC-103737

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

In fact, the COP reset didn’t fail.

The asynchronous reset like COP is not debuggable by BDM – The reset broke the BDM connection and debugger is simply confused from that.

Since the debugger probably tries to continue in communication with MCU, the final MCU mode after such reset is rather random = sometimes MCU reset to the normal single chip mode and sometimes to the special single chip mode where the final mode depends on BKGD pin value during the reset sequence.

Please use for example the LEDs for debugging the COP reset.

For example:

unsigned int i;

//function prototype of _Startup function (Start12.c)

void _Startup(void);

//******************************************************************************

// COP interurpt

//******************************************************************************

#pragma CODE_SEG NON_BANKED

interrupt 2 void COP_ISR(void)

{

DDRA = 0xff;

PORTA = 0x00; //LEDs on - show we entered the COP_ISR

for(i=0; i<60000; i++) //delay

{

asm nop;

}

PORTA = 0xff;

asm jmp _Startup; //jump to power-on reset vector

// !!! RTI instruction cannot be executed because this is not interrupt !!!

}

#pragma CODE_SEG DEFAULT

//******************************************************************************

// Main program

//******************************************************************************

void main(void) {

DDRA = 0xff;

PORTA = 0xff; //LEDs off

COPCTL = 0x47; //enable watchodg

for(;;) {} /* wait forever */

}Please be aware that external capacitance on reset pin may influence correct reset source recognition. For more details, please see https://community.nxp.com/docs/DOC-103737

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

Thanks for your reply!

So it's correct for my code...

For my understanding, using LED to debug cop reset is to verify if it triggers a cop reset and I can't debug functions when using debugger. If I add some features in my code, I have to run program on ECU without debugger? And to test these features I need to write some test code like LED control you mentioned?

Besides, I tried to use LED to debug cop reset but failed.

It always ON while should be On, Off , reset.

BR,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Yes, your understanding is correct.

The debugger cannot expect asynchronous COP reset. When the reset is not directly triggered by the debugger, the BDM connection is lost and clocks with registers are revert back to the default values during reset sequence.

If you want to test the COP reset behavior, please do it in normal mode (without debugger).

Instead of LEDs, you may use for example SCI channels or any other way for signalization…

Note: You should use just one definition for COP reset vector. If you will define COP reset vector like “interrupt 2 void COP_ISR(void)”, you should comment out definition in prm linker file “//VECTOR 2 _Startup”.

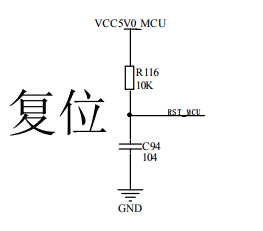

Please check capacitance on the RESET pin.

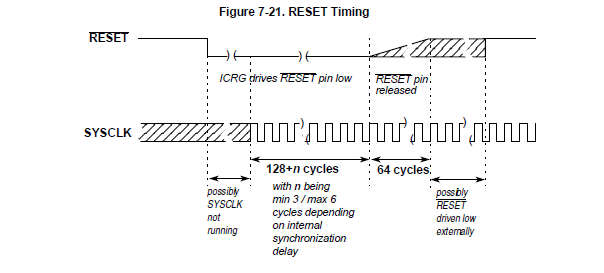

For example: The DEMO9S12XHY256 board has 100nF capacitor at RESET pin and 10KOhm external pull-up. The board is assembled by the 8MHz crystal.

If we omit internal pull-up and internal capacitance of RESET pin, the time constant t=R*C is 1ms. In this case, the POR reset vector is always used for all type of resets.

The RESET pin is tested after 64 SYSCLK cycles from RESET pin release. For MCU reset, the SYSCLK=OSCCLK. So, it presets 8us time window where the voltage at reset pin should reach a high level which is necessary for correct COP/CM reset source recognition. If we stay with 10kOhm pull-up, the maximum capacitor value at RESET pin should be below approximately 800pF.

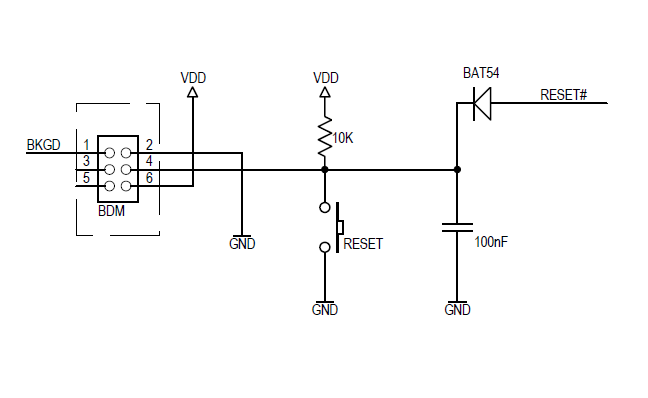

Note: Optionally, you may connect reset button and capacitor to the RESET pin through a Schottky diode. In that case, the capacitor will be not discharged by a system reset like COP or CM.

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

I tried like this:

(in borad.c)

/* enable Watchdog, which will no be refresh to create a reset */

COPCTL = 0x47U;

/* Create COP reset

ARMCOP = 0x01U;*/ /* Wait for trigger cop reset */

for(;;){}

(in board_irq.c)

unsigned int i;

void _Startup(void);

#pragma CODE_SEG NON_BANKED

void interrupt 2 COP_ISR(void)

{BoardInitLed();

BoardToggleLed(1U);

for(i=0; i<60000; i++) //delay

{

asm nop;

}

BoardToggleLed(0U);

for(i=0; i<60000; i++) //delay

{

asm nop;

}

BoardToggleLed(1U);

for(i=0; i<60000; i++) //delay

{

asm nop;

}

BoardToggleLed(0U);

asm jmp _Startup;

}

#pragma CODE_SEG DEFAULT

But I can't see LED is on and off in COP_ISR.

I'm sure these two function are correct because I tested in other code

BoardInitLed();

BoardToggleLed(1U);

And I also comment out VECTOR 2 _Startup”.

I still have no idea why I can't see the change for LED.

Br,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Thank you for more details.

Please be aware that COP_ISR() is executed just directly after reset. So, the stack and global variables are not initialized yet. If BoardInitLed() and BoardToggleLed() are real functions, the stack must be initialized first.

Please use INIT_SP_FROM_STARTUP_DESC(); command defined in hidef.h file.

Here is the appropriate code for initialize stack:

extern char __SEG_END_SSTACK[];

asm LDS #__SEG_END_SSTACK;

Note: this code will show warning C12053 Stack-pointer change not in debugging-information.

This may be disabled by pragma:

#pragma MESSAGE DISABLE C12053

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

I tried to directly set register instead of using functions. But it didn't work neither.(use COP_ISR without VECTOR 2 _Startup)

So I just wrote some code in my program(on-off-on-off).(use VECTOR 2 _Startup without COP_ISR)

When I use trace32 to debug, it was on-off-on-off and then showed me reset failed.

Then I disconnect trace32 and power-off then power-on the board. I could see it repeat the on-off-on-off process. Can I regard it as success reset?

But I am still confused why i can't get evidence from COP_ISR...

Br,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Please let me know what is connected to the RESET pin on your board.

Unfortunately, I am not experienced with the Trace32 tool. But, if LED signalizes new MCU start after unvalid ARMCOP register writes, it looks like correct behavior.

Anyway, the COP_ISR() code is useful only if you need to know the reset source (POR, COP, …) and you want to apply different codes per this reset source.

If the MCU behavior after a reset should be identical for both POR and COP resets, you don’t need to bother with COP_ISR() and capacitance on the RESET pin. In this case, you may simply watch RESET pin for testing COP reset.

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

As for RESET pin, please refer to this:

Enough for this pic? If not I may have to ask my colleague for I don't know much about hardware.

Thanks.

Br,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Thank you for these details.

If you want to use COP_ISR() code, you have to disassemble C94 from your board.

As I already wrote above, the maximum C94 capacitance only approximately 800pF may be connected to the RESET pin for correct recognition of COP as the reset source. Higher capacitance (10nF in your case) will lead to the situation that POR reset vector will be used for all kinds of resets – COP/CM resets are detected as External pin reset.

The optional hardware solution is here:

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raked,

Now I also have problem when using COP reset on S12G128, referring to the answers above. I tried to verify the cop reset by LED output pin ( high 2s -> low 2s -> high 2s ). Though it seems to be reset for i can continue to see the change of the levle, it became low 2s -> high 20s and keep this loop, on the oscilloscope.

There's no other control on this output anywhere else. I can't figure out why it shows like this.

Do you have some ideas about it?

Best regards,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Could you please share here your code?

Is RESET pin activated during this 2s/20s loop?

Did you configure default value of FOPT register at address 0xFF0E?

The interrupt 2 COP_ISR() must be ended by a jump to a code (like asm jmp _Startup).

Have a great day,

Radek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

Reset triggering code is like this, same as S12XHY128:

/* enable Watchdog, which will no be refresh to create a reset */

CPMUCOP = 0x47U;/* Wait for trigger cop reset */

while(1);

I didn't implement COP_ISR() but used

VECTOR 2 _Startup

also same as what I did in S12XHY128.

And I did nothing towards FOPT for my platform test.

As for reset pin activated or not I can't test now for the board not on my site. I have to ask my colleague to do this for me. I will update the result later.

Best regards,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Thank you for more details.

Since you defined COP reset vector the same way as POR reset vector, the behavior should be the same.

So, I expect that issue should be rather somewhere in software for LED output.

Could you please share a code for LED blinking?

Have a great day,

Radek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

LED blinking code is like this:

int i =0;

/* Toggle LED 2 since LED 1 is used in BoardInit */

BoardToggleLed(1U);

while( i <2000 )

{

if ( 1 == BoardSchedulingTimer() )

{

i++;

}

}

i=0;BoardToggleLed(0U);

while( i <2000 )

{

if ( 1 == BoardSchedulingTimer() )

{

i++;

}

}

i=0;BoardToggleLed(1U);

while( i <2000 )

{

if ( 1 == BoardSchedulingTimer() )

{

i++;

}

}

i=0;BoardPerformReset(PLATFORMS_SW_RESET);

BoardSchedulingTimer returns 1 every 1ms

Best regards,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

Hmm, currently I do not see any obvious issue in your code.

Idea: could you please try replacing “int i =0;” declaration by “volatile unsigned int i = 0;” for avoiding potential optimizations?

Have a great day,

Radek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Radek,

Thank you really much for your replies!

It helped me know much about cop reset.

Have a nice weekend,

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And no reset button used.