- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 产品论坛

- :

- PowerQUICC处理器

- :

- Re: MPC8280和SDRAM问题

MPC8280和SDRAM问题

When we say "an external multiplexer", we mean SDRAM memory with 11-bit column addressing. If SDRAM has 10-bit column addressing (or less), "an external multiplexer" is not required. See sections 4.2 and 4.3 of the AN2165 to feel the difference.

Regards,

Bulat

If I use two MT48LC4M32B2 to form 64bit data, connect to the CS1 chip on the 60x BUS. B60x_ADD28 is connected to A0 of SDRAM, B60x_ADD27 is connected to A1 of BDRAM...B60x_ADD16 is connected to A12 of SDRAM, where SDA10 is connected to A10 of SDRAM, and BNKSEL is connected to BA of SDRAM. PSDMR is configured as 0xc24b36a3, OR1 is configured as 0xfe002ec0, BR1 is configured as 0xf0000041, and SIUMCR is configured as 0x0e200000. Is this correct?

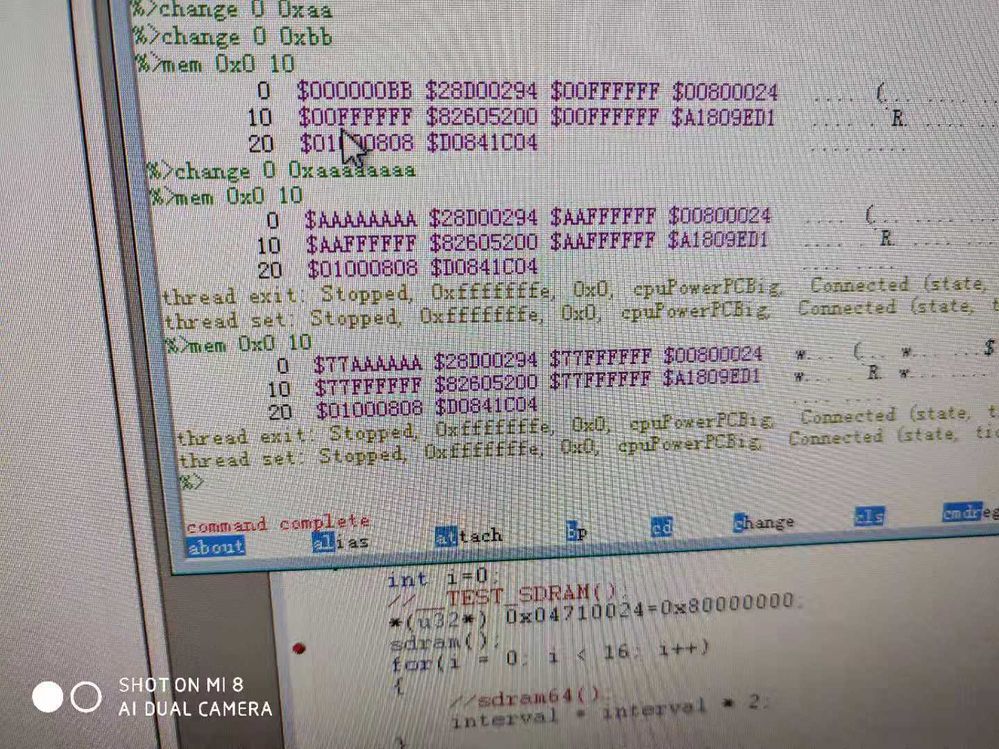

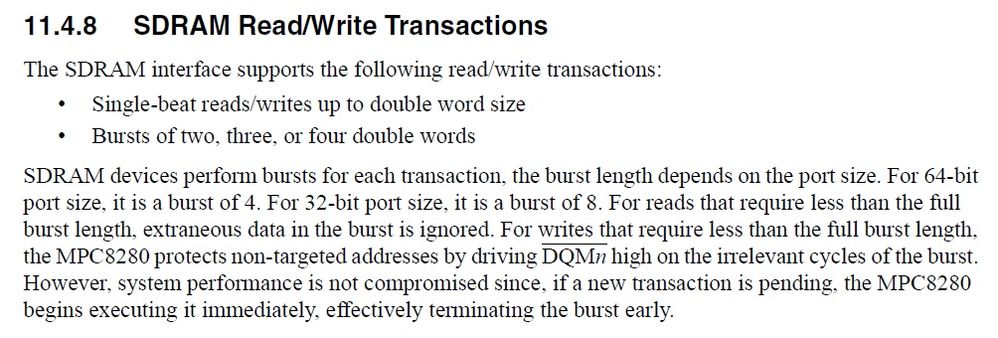

I am now experiencing a problem where the SDRAM base address is 0, writing byte 0xaa (or other data) to the 0 address will automatically change the byte 0x8, 0x10, 0x18 address to the same value as 0xaa. As shown in the figure, can you help me analyze what might be the reason? The board is made with reference to the development board.

Do you have one board or more? Would be helpful in case of SDRAM malfunction.

Do you properly initialize the SDRAM?

As per your BR1 setting, SDRAM base address is 0xf0000000. Why do you test the SDRAM at address 0x0?

There is another identical board, and the problem is the same. The address in the figure is the photo when I configured the SDRAM base address to 0xf0000000. The same problem as the SDRAM base address is configured to zero.