- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 基于模型的设计工具箱(MBDT)

- :

- 基于模型的设计工具箱(MBDT)

- :

- MPC5744P does not work properly for PWM input capture based on MBD

MPC5744P does not work properly for PWM input capture based on MBD

MPC5744P does not work properly for PWM input capture based on MBD

Hi,

When I configured input capture based on MBD to measure the frequency and duty cycle of PWM, I encountered a problem:

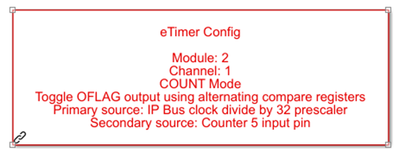

First of all, I configured one input capture according to the official example, as follows:

The code generated by this model is working properly,Then I continued to configure a few others, but found that they did not work properly, the configuration is as follows:

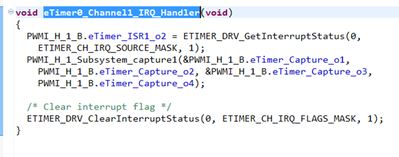

Through debug, it was found that this inoperable code did not generate a configured interrupt, that is, Input Capture 2 Flag Interrupt, and the corresponding interrupt function is as follows:

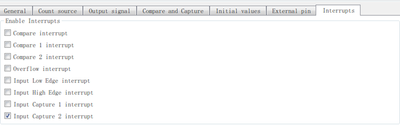

Of course, I have set the corresponding interrupt in the model and made sure that the PWM signal is input to the chip, as follows:

Later, normal operation can be realized through the register, and the corresponding configuration is as follows:

void ETimer_EtcInit(u8 ucETimerNo, u8 ucChNo)

{

pETIMER[ucETimerNo]->ENBL.R &= (~((1<<ucChNo)));// disable Timer channels

/* CTRL1---0x3F00

* bit15-13: CNTMODE = 1 count rising edge of primary source

* bit12-8: PRIsrc=0x1F ip bus clock divide by 128

* bit12-8: PRIsrc=0x1C ip bus clock divide by 16

* bit7: ONCE = 0 count repeatedly

* bit6: LENGTH = 0 continue counting to roll over

* bit5: DIR = 0 count up

* bit4-0: SECsrc=n counter #n input pin

*/

#if (PWM_FRE_RANGE == RANGE_HIGH)

pETIMER[ucETimerNo]->CH[ucChNo].CTRL1.R = 0x3C00 | (ucChNo);

#else

pETIMER[ucETimerNo]->CH[ucChNo].CTRL1.R = 0x3F00 | (ucChNo);

#endif

pETIMER[ucETimerNo]->CH[ucChNo].COMP1.R = 0xFFFF;

/* CCCTRL---0x0264

* bit15-13: CLC2 = 0 never preload

* bit12-10: CLC1 = 0 never preload

* bit9-8: CMPMODE = 2 comp1 for counting up; comp2 for counting down

* bit7-6: CPT2MODE= 1 CAPT2 capture falling edge

* bit5-4: CPT1MODE= 2 CAPT1 capture rising edge

* bit3-2: CFWM = 1 capture FIFO water mark

* bit1: ONESHOT = 0 free running(not one shot mode)

* bit0: ARM = 0 input capture disable

*/

pETIMER[ucETimerNo]->CH[ucChNo].CCCTRL.R = 0x0264;

/* INTDMA---0x0080

* bit15: ICF2DE = 0 Input Capture 2 Flag DMA disable

* bit14: ICF1DE = 0 Input Capture 1 Flag DMA disable

* bit13: CMPLD2DE= 0 Comparator Load Register 2 Flag DMA disable

* bit12: CMPLD1DE= 0 Comparator Load Register 1 Flag DMA disable

* bit9: WDFIE = 0 Watchdog Flag Interrupt disable

* bit8: RDFIE = 0 Redundant Channel Flag Interrupt disable

* bit7: ICF2IE = 1 Input Capture 2 Flag Interrupt enable

* bit6: ICF1IE = 0 Input Capture 1 Flag Interrupt disable

* bit5: IEHFIE = 0 Input Edge High Flag Interrupt disable

* bit4: IELFIE = 0 Input Edge Low Flag Interrupt disable

* bit3: TOFIE = 0 Timer Overflow Flag Interrupt enable

* bit2: TCF2IE = 0 Timer Compare 2 Flag Interrupt disable

* bit1: TCF1IE = 0 Timer Compare 1 Flag Interrupt disable

* bit0: TCFIE = 0 Timer Compare Flag Interrupt disable

*/

pETIMER[ucETimerNo]->CH[ucChNo].INTDMA.R = 0x0080; //Input Capture 2

pETIMER[ucETimerNo]->CH[ucChNo].CTRL3.R = 1;

pETIMER[ucETimerNo]->ENBL.R |= (1<<ucChNo); // enable Timer channels

pETIMER[ucETimerNo]->CH[ucChNo].CCCTRL.B.ARM = 1;// input capture enable

}Finally, after configuring the model according to the corresponding register, the code generated by the model still does not work properly。

I put all the models in the attachment:

The first model is a model that can work normally, and the second is a model that does not work properly。

Kind regards,

zhang.