- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

My first Question:

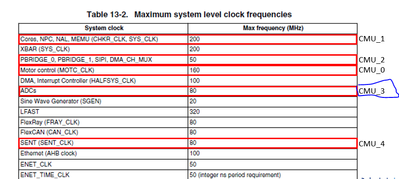

Shall I configure CMU_3 to monitor the ADC on the max value given in the below table ,and Shall I consider the frequencies below in all CMUs.

I did so in the HFREF and LFREF

=80Mhz*16*4/16Mhz =320

LFREF = 320*0.95 = 304 --> 0x130

HFREF = 320*1.05 = 336 --> 0x150

if this is correct how shall I test this implementation?

I have added an ADC and tried to change the LFREF and HFREF to other values in order for the CMU to write 1 to CMU_ISR[OLRI] but it failed to do it.

Is there any other configuration to be done?

- the configuration that I have done

- CME -> CLKMN1 monitor enable. to 1

- RCDIV->CLKMT0_RMN division factor. to 11

- CKSEL1 -> CLKMT0_RMN is selected to 11

LFREF = 320*0.95 = 304 --> 0x130

HFREF = 320*1.05 = 336 --> 0x150

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

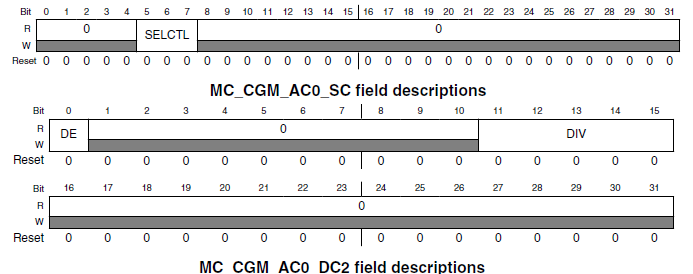

you need to select clock source in MC_CGM.AC0_SC and then enable divider MC_CGM.AC0_DC2 (set DE bit and DIV)

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your reply,

I have enabled the MC_CGM_AC0_DC2 divider and read the MC_CGM_AC0=0x0400 0000, however, the CMU_ISR register is fetching the same value written in the CMU_CSR register

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

if you increase AC0_DC2 divider, will a low reference flag be set?

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, it changes, however Now I have another Issue,

In CMU0, CMU3, CMU4

the ISR of each fire 0x02, FLLI

What are the values should be written in their division register in order to clear the ISR FLLI bit

CMU0

=160Mhz*16*4/16Mhz =640

LFREF = 640*0.95 = 608 --> 0x260

HFREF = 800*1.05 = 672 --> 0x2A0

MC_CGM_AC0_DC0=0x80010000

CMU3

=80Mhz*16*4/16Mhz =320

LFREF = 320*0.95 = 304 --> 0x130

HFREF = 320*1.05 = 336 --> 0x150

MC_CGM_AC0_DC2 = 0x80000000

CMU4

=80Mhz*16*4/16Mhz =320

LFREF = 320*0.95 = 304 --> 0x130

HFREF = 320*1.05 = 336 --> 0x150

MC_CGM_AC1_DC1= 0x80000000

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

how to enable the in MC_CGM_AC0 is enabled in MC_ME ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

you need to select clock source in MC_CGM.AC0_SC and then enable divider MC_CGM.AC0_DC2 (set DE bit and DIV)

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

CLKMN0_RMT monitor is only implemented on CMU0, so on CMU3 just LFREF, HFREF and CME can be written, also only FLL, FHH flags can be set.

Calculation is correct, so be sure selected clock in MC_CGM_AC0 is enabled in MC_ME and MC_CGM_AC0_DC2 divider is enabled. With divider you can also test low freq reference.

BR, Petr