- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 产品论坛

- :

- MCX Microcontrollers

- :

- RAM and ECC

RAM and ECC

I'm developing on the MCXN947.

Right now, my SRAM starts at 0x20000000 and has a size of 0x50000 (which is 320KB). Part of the RAM is dedicate to the ECC. But I need more RAM. Since I'm not planning on using the ECC, would it be possible to disable the ECC and repurpose the RAM banks that are allocated for it into my SRAM?

Thanks!

已解决! 转到解答。

If you don't need ECC, you can disable ECC to have more SRAM used for ECC as regular SRAM, which will increase the available memory.

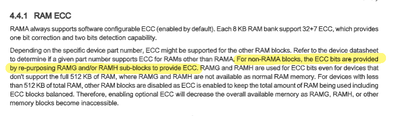

All SRAM blocks (except RAMA) ECC bits are located in .SRAMG and SRAMH. But if you disable ECC, they free up for general use. see below extracted from RM:

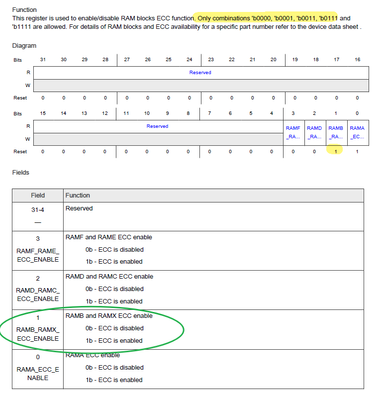

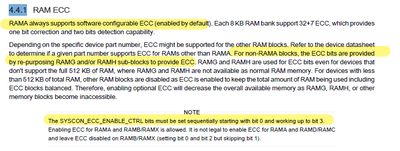

To do it, we need to configure SYSCON_ECC_ENABLE_CTRL register. Note that ECC is enabled by default for RAMB and RAMX on ECC-supported parts, but you can turn it off via this register.

Just make sure to follow the specified sequence when setting the register bits to avoid issues. see below I extracted from RM

For more, see MCXNx4xRM, chapter 4 Memory.

Hope this will help you.

Jun Zhang

If you don't need ECC, you can disable ECC to have more SRAM used for ECC as regular SRAM, which will increase the available memory.

All SRAM blocks (except RAMA) ECC bits are located in .SRAMG and SRAMH. But if you disable ECC, they free up for general use. see below extracted from RM:

To do it, we need to configure SYSCON_ECC_ENABLE_CTRL register. Note that ECC is enabled by default for RAMB and RAMX on ECC-supported parts, but you can turn it off via this register.

Just make sure to follow the specified sequence when setting the register bits to avoid issues. see below I extracted from RM

For more, see MCXNx4xRM, chapter 4 Memory.

Hope this will help you.

Jun Zhang