- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MCX Microcontrollers

- :

- MCXN947 failed to control GPIO in slave core (CPU1)

MCXN947 failed to control GPIO in slave core (CPU1)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello NXP,

I need to control GPIO or other interface in MCXN947 slave core (or CPU1, not CPU0).

Based on example <multicore_examples\rpmsg_lite_pingpong> in v25.06 FRDM-MCXN947 sdk, then take a P0_10(RED_LED)configuration and create control code to salve core main function. After built, I find that RED_LED can't be controlled.

Hope you can help me find the reason and fix it.

Thanks very much.

----Test code

1>for RED_LED pin configuration, I used MCUXPresso IDE to config and generate code automatically.

shown as below.

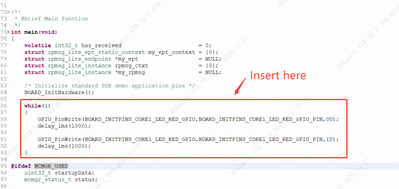

2>for RED_LED control, below is the code I create in slave core project.

//---------------------------

#include "fsl_gpio.h"

#include "fsl_clock.h"

#include "fsl_common.h"

#include "pin_mux.h"

void delay_1ms(uint32_t dt)

{

uint32_t Core_Freq;

Core_Freq = CLOCK_GetCoreSysClkFreq();

for(uint32_t i=0; i<dt; i++)

{

SDK_DelayAtLeastUs(1000,Core_Freq);

}

}

//----------------------------

while(1)

{

GPIO_PinWrite(BOARD_INITPINS_CORE1_LED_RED_GPIO,BOARD_INITPINS_CORE1_LED_RED_GPIO_PIN,0U);

delay_1ms(1000);

GPIO_PinWrite(BOARD_INITPINS_CORE1_LED_RED_GPIO,BOARD_INITPINS_CORE1_LED_RED_GPIO_PIN,1U);

delay_1ms(1000);

}

BTW, I have tested that the code shown above can work in single example, as <demo_apps\hello_world\cm33_core0>

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jimmyli

Could you please share your code snippet?

To use LPUART peripheral does not require GPIO's configuration.

The attachment is demo code which print message from both Core0 and Core1.

Best Regards,

Logiase Song

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Logiase,

Thanks very much.

I will take test with your example.

Any question, I will give a feedback soon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, jimmyli

Please configure the register `PCNS` in GPIO peripheral. This register controls if the corresponding pin‘s registers can be modified in Secure/NonSecure state.

The Core1 in MCXN947 does not implement SAU(Security Attribute Unit), which means that the Core1 is always in NonSecure state, so register read/write to corresponding pin's registers under Core1 has no effect.

Best Regards,

Logiase Song

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, jimmyli

Please configure the register `PCNS` in GPIO peripheral. This register controls if the corresponding pin‘s registers can be modified in Secure/NonSecure state.

The Core1 in MCXN947 does not implement SAU(Security Attribute Unit), which means that the Core1 is always in NonSecure state, so register read/write to corresponding pin's registers under Core1 has no effect.

Best Regards,

Logiase Song

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Logiase,

Thanks very much for your replying.

Yes, I have found that before booting core1, it needs to config the referent pin to non secure state and can be controlled by core1 , and the pin can be controlled by core1.

----below code is added to initHardware() in core0 project

CLOCK_EnableClock(kCLOCK_Gpio0);

GPIO_EnablePinControlNonSecure(BOARD_LED_RED_GPIO, (1 << BOARD_LED_RED_GPIO_PIN));

But, I have a new question that when I only config uart pin to non secure state and initialize uart model in core1 project, the uart interface can't work.

Do you have some tips for this problem ?

Thanks very much.