- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- SDRAM data bytes shifting

SDRAM data bytes shifting

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the scenario is

when we write and read immediate it is working fine ,if we read after some time the the data bytes are shifting 2-4 bytes but occur randomly

example

the data written to SD RAM

0xA0000000 -> 0x00000000 0x44332211 0x88776655

0xA000000C->0x000000001 0x44332211 0x88776655

....

.....

data reading after some time

0xA0000000 -> 0x00000000 0x44332211 0x88778877

0xA000000C->0x000000001 0x44332211 0x88776655

the SD RAM we used is AS4C4M16SA-6TIN

the timming we have initialized

are

#define SDRAM_REFRESHPERIOD_NS (64 * 1000000 / 4096) /* 4096 rows/ 64ms */

#define SDRAM_TRP_NS (21u)

#define SDRAM_TRAS_NS (42u)

#define SDRAM_TSREX_NS (67u)

#define SDRAM_TAPR_NS (20u)

#define SDRAM_TWRDELT_NS (6u)

#define SDRAM_TRC_NS (60u)

#define SDRAM_RFC_NS (60u)

#define SDRAM_XSR_NS (67u)

#define SDRAM_RRD_NS (14u)

#define SDRAM_MRD_NCLK (2u)

#define SDRAM_RAS_NCLK (2u)

#define SDRAM_MODEREG_VALUE (0x33u)

#define SDRAM_DEV_MEMORYMAP (0x05u) /* 64Mbits (4M*16, 4banks, 12 rows, 8 columns)*/

we used SDK emc files .

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi mike

thanks for replay

probability is reduced when EMC CLK is reduced to 45Mhz from 90Mhz

Refresh interval where we configure the EMC register

the information regarding Refresh interval is not provided in the datasheet.

please provided layout consideration for the SDRAM design.

if need I will send the our schematic files

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

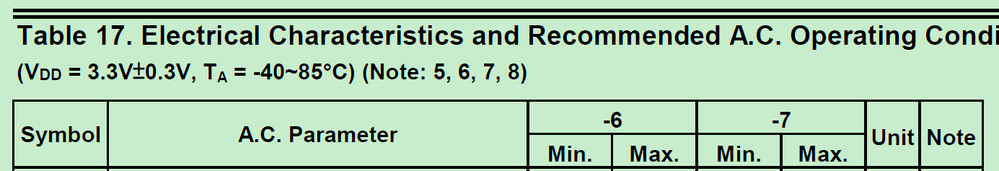

I check the Max. refresh interval time below at AS4C4M16SA datasheet:

There are some application notes about SDRAM design with LPC EMC module:

AN11508: SDRAM interface to LPC18xx/43xx EMC

− Comprehensive information about connecting EMC to different SDRAMs

− Some advanced skills like clock compensation options

− PCB layout guide

AN10771: Using the LPC24xx EMC peripheral to drive SDRAM

− Similar as AN11508, but early and simpler document

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi mike

thanks for replay

probability is reduced when EMC CLK is reduced to 45Mhz from 90Mhz

Refresh interval where we configure the EMC register

the information regarding Refresh interval is not provided in the datasheet.

please provided layout consideration for the SDRAM design.

if need I will send the our schematic files

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

First of all, thank you for the patience.

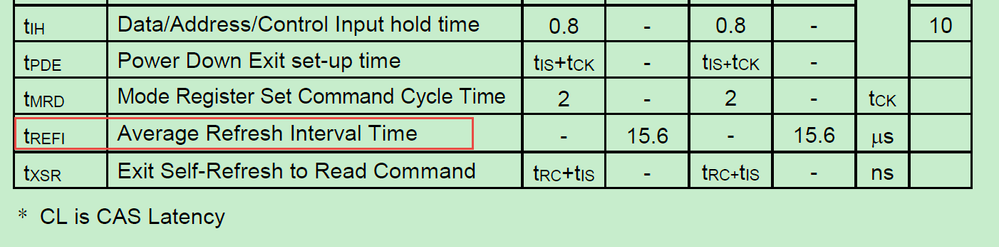

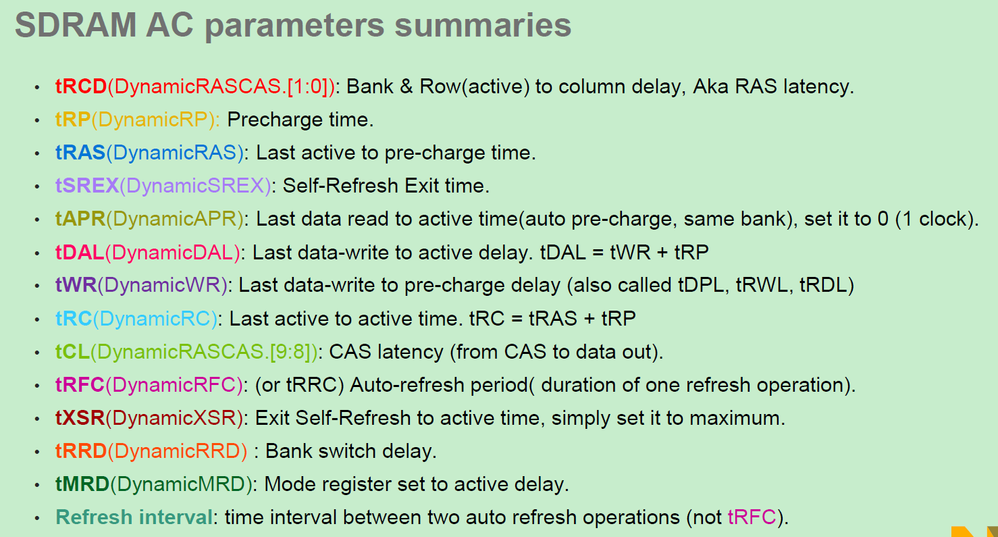

Please check below definition about SDRAM timing:

I checked the SDRAM timing value with below concerns:

#define SDRAM_TRP_NS (21u) From AS4C4M16SA datasheet the value should be 18u;

#define SDRAM_TSREX_NS (67u) is Self-Refresh Exit time, tRC+tIS = 60+1.5 , which should be 62u;

#define SDRAM_TAPR_NS (20u) the value is 18u;

#define SDRAM_RRD_NS (14u) should be 12u;

When you slow down the SDRAM clock frequency, if the issue happen probability reduced?

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi mike

thanks for replay

probability is not reduced when EMC CLK is reduced to 45Mhz from 90Mhz

Refresh interval where we configure the EMC register

the information regarding Refresh interval is not provided in the datasheet.

please provided layout consideration for the SDRAM design.

if need I will send the our schematic files