- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

LPC54102 Deep sleep wake up on I2C slave

I'm using a LPCXpresso54102 board and I'm trying to enter DEEP_SLEEP mode and wake up by I2C slave interrupt. I've followed the instructions in the manual (UM108050, section 25.4.3.2) and done all the steps in the required order. Anyway, no matter what order I try, I don't manage to wake up on I2C. Code works well if I don't sleep.

Any ides of what I'm doing wrong. See the code below:

#define MK_BRIDGE_I2C_PORT LPC_I2C2

#define MK_BRIDGE_I2C_INTHAND I2C2_IRQHandler

#define MK_BRIDGE_IRQNUM I2C2_IRQn

#define MK_BRIDGE_WAKEUP_SRC SYSCON_STARTER_I2C2

#define MK_BRIDGE_I2C_SCL_PIN 27

#define MK_BRIDGE_I2C_SDA_PIN 28

#define MK_BRIDGE_I2C_SCL_FN IOCON_FUNC1

#define MK_BRIDGE_I2C_SDA_FN IOCON_FUNC1

#define MK_BRIDGE_I2C_SLVADD 0x29

#define MK_BRIDGE_I2C_CLK_DIVIDER (2)

#define MK_BRIDGE_I2C_SPEED NRF_TWI_FREQ_100K

int main(void)

{

Board_Init();

NVIC_EnableIRQ(MK_BRIDGE_IRQNUM);

Chip_SYSCON_EnableWakeup(MK_BRIDGE_WAKEUP_SRC);

/* Enable the I2C controller */

Chip_I2C_Init(MK_BRIDGE_I2C_PORT);

Chip_I2CS_Enable(MK_BRIDGE_I2C_PORT);

/* Initialize I2C pins */

Chip_IOCON_PinMuxSet(LPC_IOCON, MK_BRIDGE_I2C_SCL_PORT,

MK_BRIDGE_I2C_SCL_PIN,

(MK_BRIDGE_I2C_SCL_FN | IOCON_DIGITAL_EN));

Chip_IOCON_PinMuxSet(LPC_IOCON,

MK_BRIDGE_I2C_SDA_PORT,

MK_BRIDGE_I2C_SDA_PIN, (MK_BRIDGE_I2C_SDA_FN | IOCON_DIGITAL_EN));

/* Setup clock rate for I2C */ //JH: check if we need that

Chip_I2C_SetClockDiv(MK_BRIDGE_I2C_PORT, MK_BRIDGE_I2C_CLK_DIVIDER);

/* Slave address on index 0 */

Chip_I2CS_SetSlaveAddr(MK_BRIDGE_I2C_PORT, 0, MK_BRIDGE_I2C_SLVADD);

/* Clear interrupt status and enable slave interrupts */

Chip_I2CS_ClearStatus(MK_BRIDGE_I2C_PORT, I2C_STAT_SLVDESEL);

Chip_I2C_EnableInt(MK_BRIDGE_I2C_PORT, I2C_INTENSET_SLVPENDING | I2C_INTENSET_SLVDESEL);

while(1) {

for(int j = 0; j < 5; j ++) {

for (int i = 0; i < 100000;i++);

Board_LED_Set(1, 1);

for (int i = 0; i < 100000;i++);

Board_LED_Set(1, 0);

}

Chip_POWER_EnterPowerMode(

POWER_DEEP_SLEEP,

SYSCON_PDRUNCFG_PD_WDT_OSC |

SYSCON_PDRUNCFG_PD_SRAM0A |

SYSCON_PDRUNCFG_PD_SRAM0B |

SYSCON_PDRUNCFG_PD_SRAM1 |

SYSCON_PDRUNCFG_PD_SRAM2 |

SYSCON_PDRUNCFG_PD_32K_OSC|

SYSCON_PDRUNCFG_PD_BOD_RST|

SYSCON_PDRUNCFG_PD_BOD_INTR);

}}

Hi Genis,

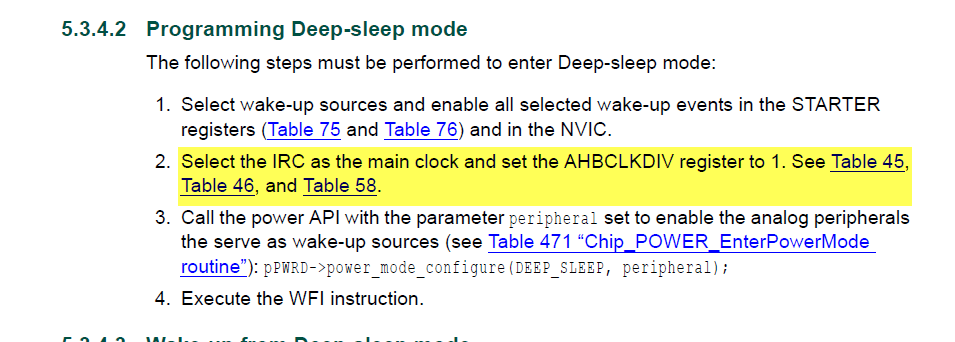

Before you enter deep sleep mode, did you change the clock to use the internal IRC as the the main clock?

Please check this information from the user manual:

Please check it at first.

Any updated information, please let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thank you Kerry, that was it. After changing to IRC clock now LPC wakes up on I2C. Still, I noticed that the first packet after waking up was always lost, I don't exactly know the reason why. I added a pin interrupt that awakes the micro some milliseconds before the master sends the I2C address.

Hi Genis Aguilar,

Thanks for your updated information.

Please do the test in the I2C slave after it is waked up. After it is waked up, you can toggle the GPIO, just to check the MCU is really waked up. Then you can send some other I2C data to the slave.

Besides, you said:the first packet after waking up was always lost.

Do you mean the second packet has no problem?

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Yes, that's it: first packet wakes up the microcontroller but is lost, whereas the second one is received correctly. That may be due to implementation details or some timing issues, I don't know. Anyway I could sort that out by connecting a new line from I2C master which wakes slave mcu a few milliseconds before the I2C address is sent. I have plenty of free pins so that's not a problem right now.