- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- LPC-LinkII ADC speed and progress

LPC-LinkII ADC speed and progress

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC-LinkII ADC speed and progress

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, experts.

I am trying to run HSADC to 80M on LPC-Link-2.

But I am confusing about it.

When I set the ADC clock as:

Chip_USB0_Init();

Chip_Clock_SetDivider(CLK_IDIV_A,CLKIN_USBPLL,4);

Chip_Clock_SetDivider(CLK_IDIV_B,CLKIN_IDIVA,15);

Chip_Clock_SetBaseClock(CLK_BASE_ADCHS,CLKIN_IDIVB,true,false);

Chip_Clock_EnableOpts(CLK_MX_ADCHS, true, true, 1);

Chip_Clock_Enable(CLK_ADCHS);

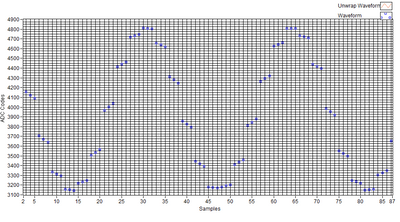

The ADC resault will looks like this:

It did not match the 80M sample rate. It looks only 20~30M. And also this is a sine wave. Why does it break and look not like a sine wave? I tried 8M sampling rate. It works great. But if I try to speed up the ADC sample clock it will do like this.

And also I would like to know is it possible to track the progress of ADC?

I know I can use like CH[DMA_CH].DESTADDR to know where the ADC writing now.

But if I can get the signal every time ADC filled up a sample (a RAM) it will be way more better.

I appreciate any help.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello JiaAn,

The HSADC demo under LPCopen is 80M .

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Alice.

Where can I get that LPCOpen? I guess my LPC Open is too old or incomplete. Can you tell me the example name and where can I get the newest LPC Open? Thank you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello JiaAn,

Download LPCopen from:

BR

Alice

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I tried to output the ADC base clock and it's only 12Mhz.

What I did is just add like:

Chip_Clock_SetBaseClock(CLK_BASE_OUT, mappedCGUDuv, true ,false);

Chip_SCU_PinMuxSet(0x1, 19, (SCU_PINIO_FAST |SCU_MODE_FUNC4));

That shouldn't effect ADC clock. Any idea why is that?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jia,

Try to this thread code:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hey Alice,

I am still confusing about the example. How should I read the UART? I attach the UART on J3 and set baud 9600. The data seems not correct. Can you tell me how to read the ADC results out on this example? Thanks.

What I recived on UART is:

ADC VALUE_0]z 00000bga=

ADC VALUE_0]z 00000x00

ADC VALUE_0}z 00000cb1=

PÔVALUE_0}z 000001d

ADC VALUE_0]z 00000cw2=

ADC VALUE_0]: 00000x00

PÔVALUE_0}z 00000c00=

ADC VALUE{0}z 00000113=

ADC VALUE_0}: 000001xx

ADC VALUE_0}z 00000d1d

ADC VALUE{0]z 00000x0e

JiaAn.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The UART output is partially recognizeable, which suggest the problem is in your code. Especially in the printf (PRINTF() ?) call.

Not sure what you want to ouput there, but I hope you are aware of the bandwidth differences between the ADC and the UART.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hey, Frank.

I use the example code without change anything. So I wonder how to receive the ADC result from the example code correctly. The code is set band as 115200. But the result is a mess like I wrote early. Is there anything I need to do before I start the code and UART?

With my code early, If the band is higher than 9600 it will be totally a mess. But because it could be my problem so I didn't change any example code but just upload to my LPC Link 2 and test it.

BTW, I did try to set the baud rate to 9600 but with no luck.

Is the UART send out every ADC data without skip any one of them?

Another question just popup today. Can the RAM store the 80M ADC result correctly? Do I need to consider the bandwidth differently between RAM and ADC? If so, where can I find more details about this? What's the maximum speed can ADC run and store into RAM?

Thank you for keep try to help me. I really need it and appreciate it.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I don't have/use a LPC4370, so I cannottest code myself.

But first, it should be clear that you cannot output 120MBps ADC data over a 0,0096Mbps UART channel in realtime. I am pretty sure the LPC4370 has no output channel which can sustain this high data rate in a feed-though manner, you will need to buffer the ADC data in RAM.

Secondly, with a 80Msps rate, internal bus bandwidth can become a problem, and needs at least a consideration. I am quite sure an interrupt-based approach will not work out, you will get ADC overflows immediately. You will need to setup a DMA channel for the number of samples your ADC is supposed to take. I would check the LPC-Link sources, how they do it. Perhaps even use this project as starting point for your project.

> BTW, I did try to set the baud rate to 9600 but with no luck. ...

The simplest way would be to enable semihosting in the project, and add PRINTF calls in the debug version of your code/project. These outputs are routed via the debug adapter, and it's VCOM functionality, and show up in the debug console of the IDE. If you want to a separate UART, you could use a UART example from the LPC4370 SDK, and adapt it if necessary.

As stated before, do not try outputs/printf, or other calls during the sampling phase, this will not work. Run your ADC sampling first, and output via UART/semihosting afterwards.

> Can the RAM store the 80M ADC result correctly? ... What's the maximum speed can ADC run and store into RAM?

Sure. But you will need DMA, which transfers the ADC results directly to RAM.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I did try DMA. But the weirdest thing is I tried output ADC clock and find out it's only 12Mhz.

/* Now to setup clocks */

if (maxCGUDiv == 1) {

/* CCU divider and base clock only */

/* Select best clock as HSADC base clock */

Chip_Clock_SetBaseClock(CLK_BASE_ADCHS, savedClkIn, true, false);

Chip_Clock_SetBaseClock(CLK_BASE_OUT, savedClkIn, true ,false);

Chip_SCU_PinMuxSet(0x1, 19, (SCU_PINIO_FAST |SCU_MODE_FUNC4));

}

else {

/* CCU divider with base clock routed via a CGU divider */

Chip_Clock_SetDivider(bestDivider, savedClkIn, savedMaxCGU);

Chip_Clock_SetBaseClock(CLK_BASE_ADCHS, mappedCGUDuv, true, false);

Chip_Clock_SetBaseClock(CLK_BASE_OUT, mappedCGUDuv, true ,false);

Chip_SCU_PinMuxSet(0x1, 19, (SCU_PINIO_FAST |SCU_MODE_FUNC4));

}

/* Enable ADC clock */

Chip_Clock_EnableOpts(CLK_ADCHS, true, true, 1);

So if the ADC clock is only 12Mhz the ADC sample rate probably won't be 80Msps. But I only add the clock output code into the example code without change anything.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I honestly don't know, I don't have experience with the LPC4370.

12MHz vs. 80Msps sounds weird and contradictory, yes. But for most Cortex M devices I know, the maximal peripheral clock is core_clock/2, which (assuming 204MHz), would not be sufficient to drive a 12-bit 80Msps ADC in the usual successive-approximation fashion.

The HSADC might use an internal PLL. I would suggest to check the HSADC section of the MCU user manual.

PS: looking into it, the HSADC performs a conversion in one cycle, so it's most probably a flash converter, not a SA-ADC. Maximal ADC clock is stated to be 80MHz.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I guess I need to check UART first. Why can't it work? Do you have any idea?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Going out on a limb, since I have no experience with the LPC4370 ...

But you got 3 consecutive samples, and then a "gap", followed by another 3 consecutive samples - and so on.

A interrupt handler routine to clean out ADC results from a "FIFO half-full" interrupt ?

80 MSPS is a serious number, I think it is illusory to handle that throughput with core involvement.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I had tried both

Chip_HSADC_SetupFIFO(LPC_ADCHS, 8, FALSE);

Chip_HSADC_SetupFIFO(LPC_ADCHS, 8, TURE);

These two settings has same result.

The datasheets wrote it can be 80M. So I guess it's possible. But might need in a perfect condition...

Still finding how to do it right now.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

My point is - I think the 80 Msps data rate is achievable/sustainable only with DMA.