- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: ADC output distortion in LPC54608J512BD208

ADC output distortion in LPC54608J512BD208

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

ADC output distortion in LPC54608J512BD208

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have used LPC54608J512BD208 microcontroller in protection relay. The external input voltage is stepped down,superimposed on a 1.65V DC signal and fed to the ADC input of microcontroller. I am using 6 ADC channels namely ADC0_0, ADC0_4, ADC0_5, ADC0_6, ADC0_7 & ADC0_8. The controller is driven by an external crystal of 16 MHz stepped up through PLL to 100 MHz. The following are the connections to adc pins:

I am getting no fluctuations when passing only DC signal at the ADC.

ADC gives distorted output when AC signal is superimposed on DC signal and applied to ADC.

I have observed the waveforms at ADC input pin without any distortion on a DSO.

I have attached my project, ADC samples and controller schematic for reference. Please help in resolving this issue.

Thanks & best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Prasanna Naik,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

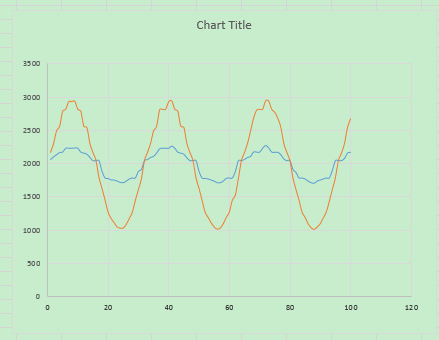

In your ADC_Test_Reslut.xls, it presents the signal which is superimposed on a 1.65V DC signal, these two lines are not only different but also both of them are a bit distorted.

So I'd like to suggest that you increase the sampling frequency and sample point to rebuild the signal. In further, I had done similar testing before, it may give you an insight into this phenomenon.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi jeremy,

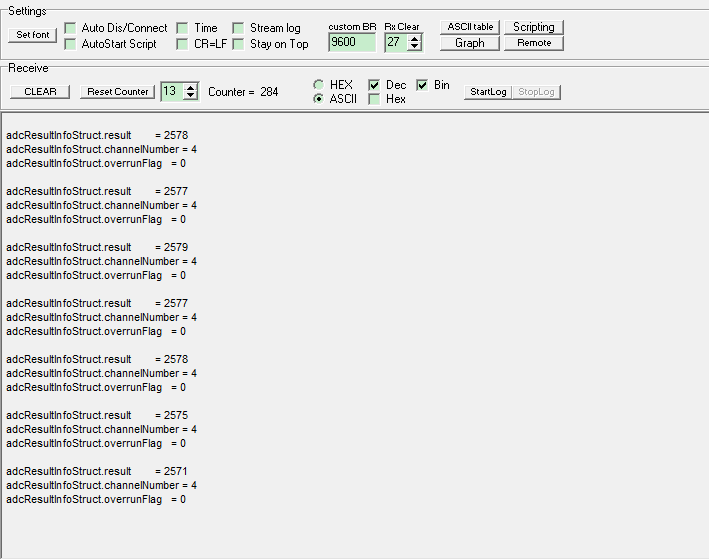

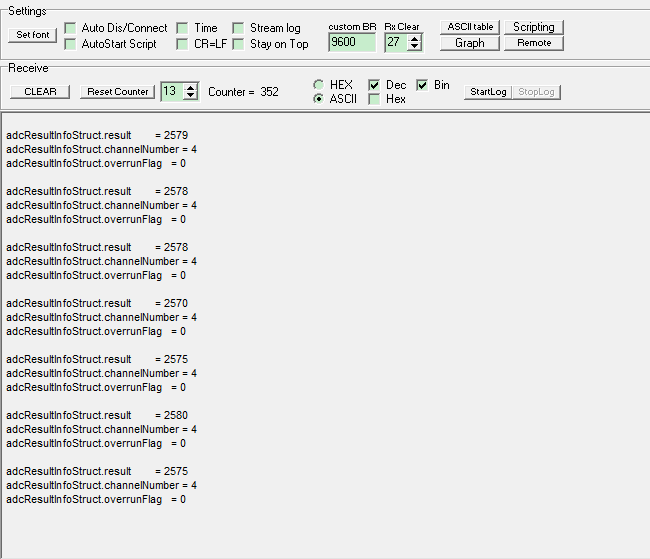

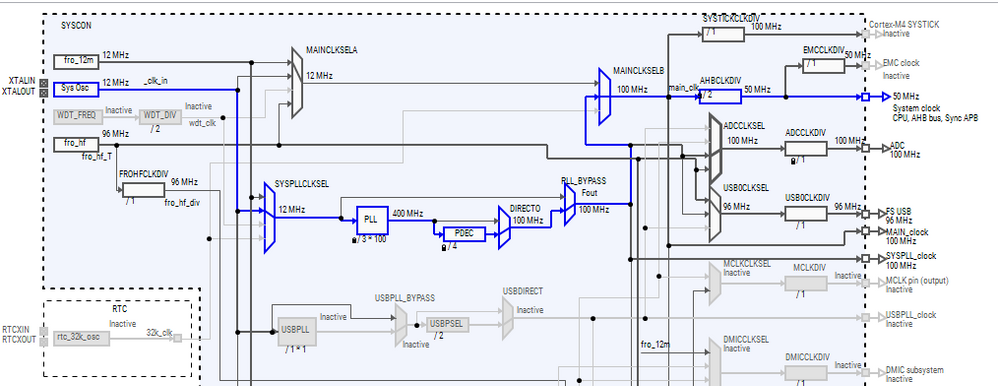

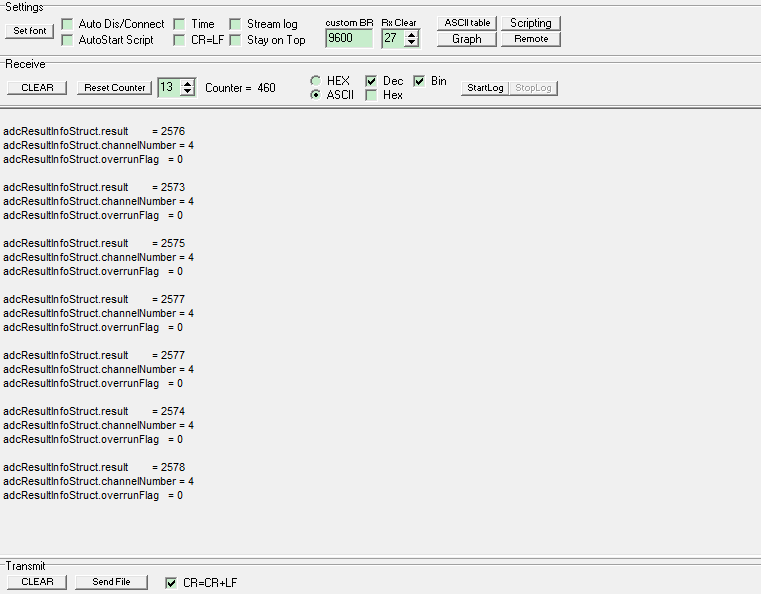

i have resolved the ADC distortion issue but i am facing a different issue now. i am applying constant 1.65 V DC at input of ADC but i am getting varying output depending on my clock configuration. I have attached the test results for your reference.

When i keep my core at 100 MHz then ADC gives very low output(1980 instead of 2048) whereas when i keep the core clock below or equal to 80 MHz ADC gives better results. Please check the attached results. I couldn't find any explaination for this. please help.

Thank and best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Prasanna Naik,

Thanks for your reply.

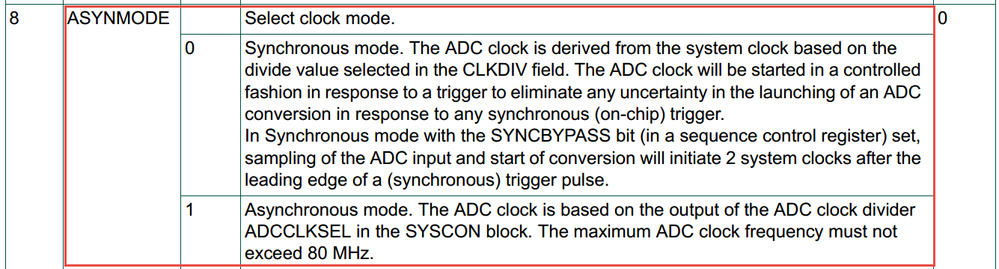

Whether you can tell me which clock mode you selected.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeremy,

I have tried both async and sync adc clocks with 100 MHz core clock but still no effect.

I have attached the test results of the various experiments that i tried with clock in "adc_clock_test_results.xlsx"

Thanks and best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Prasanna Naik,

Thanks for your reply.

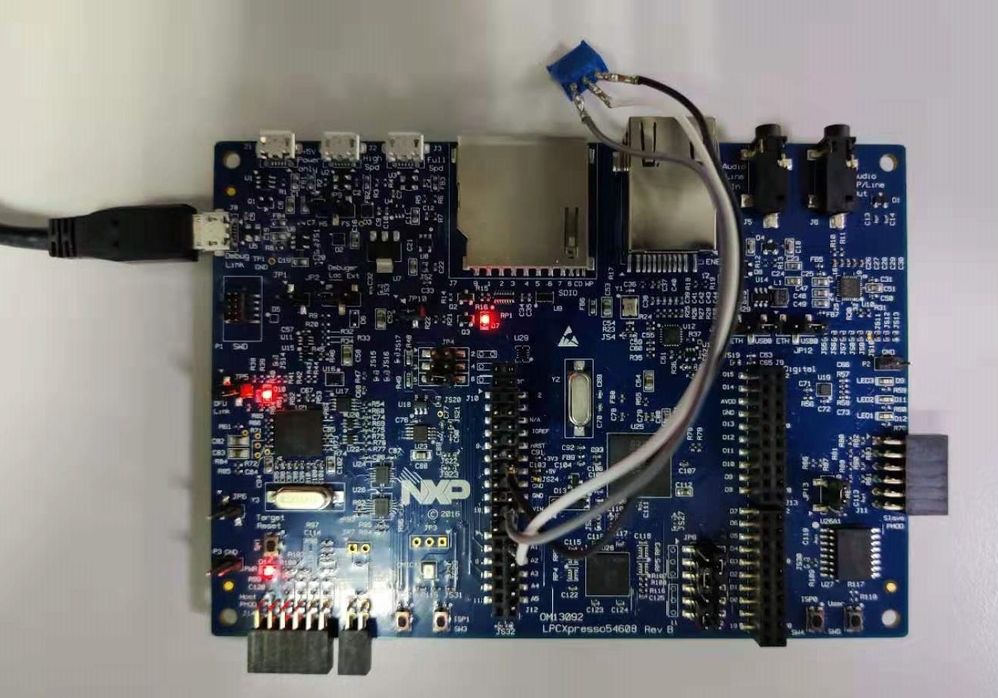

It seems a bit weird actually, so I was wondering if you can share your demo project, then I can replicate the phenomenon on the OM13092 board and it can help me to figure it out.

Looking forward to your reply.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi jeremy,

I have already attached the project in this query.

Please refer the following link.

ADC output distortion in LPC54608J512BD208

Thanks & best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi jeremyzhou,

Any update on this query?

We are stuck because of this in our development.

Please help.

Thanks and best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Prasanna Naik,

Thanks for your reply.

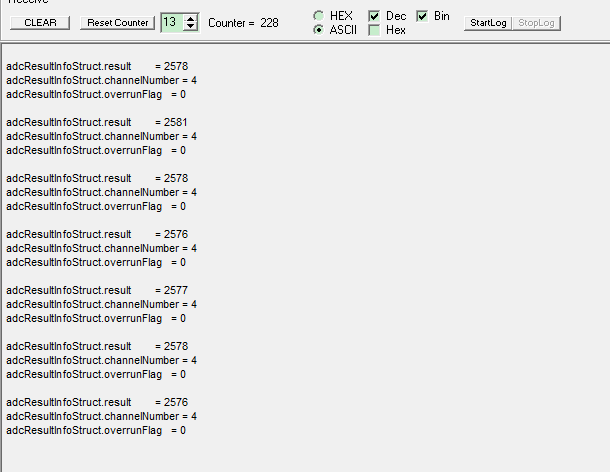

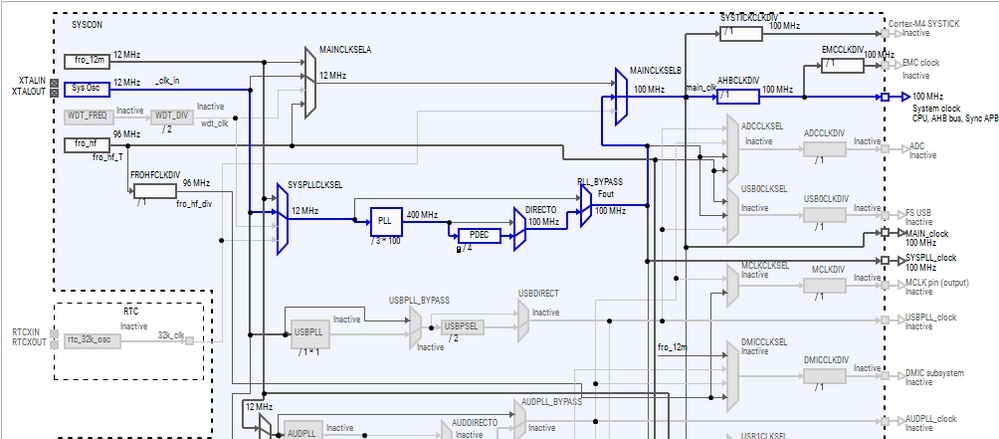

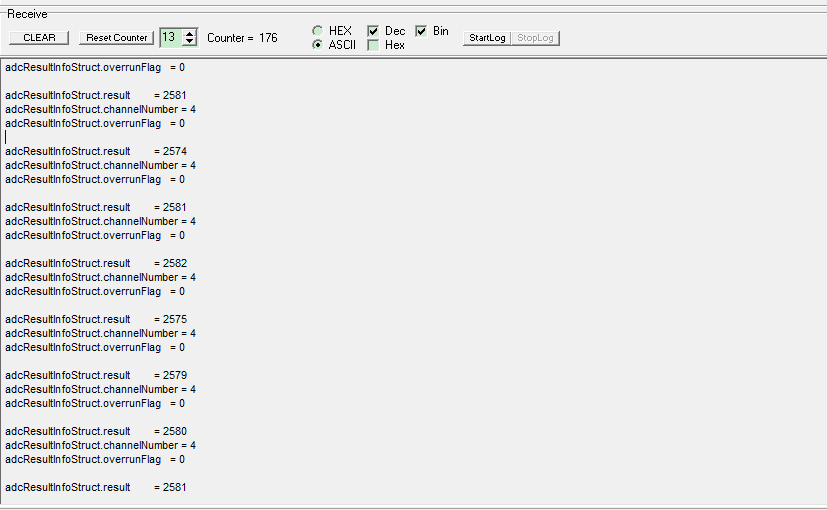

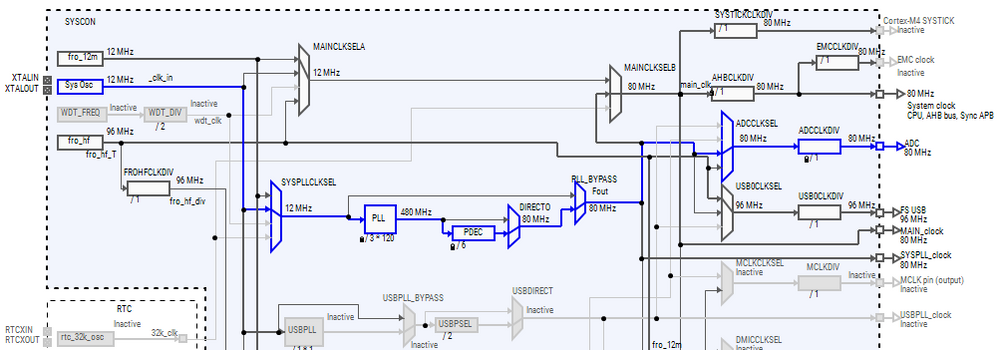

I've used the ADC channel4 pin to convert a 2.07V DC signal and the testing result is presented below.

Board: OM13092, demo project: lpcxpresso54608_lpc_adc_basic (From the SDK library)

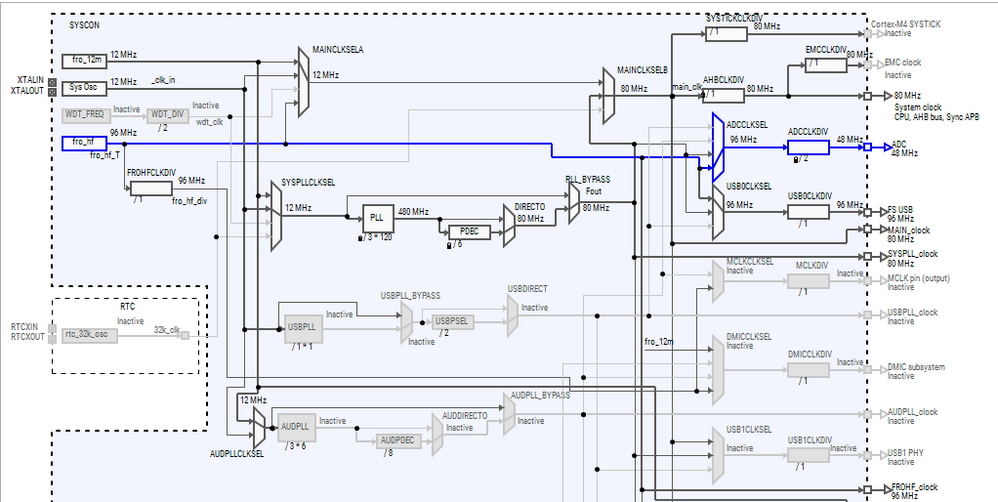

1) async clock 80 MHz:

Clock tree:

ADC conversion result:

2) async_clock_100MHz:

Clock tree:

ADC conversion result:

3) sync_clock_80MHz

Clock tree:

ADC conversion result:

4) sync_clock_100MHz

Clock tree:

ADC conversion result

5) sync_clock_50MHz

Clock tree:

ADC conversion result

Conclusion: These results are almost the same actually.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeremy,

I have tested this on two boards and results are still the same as i explained in earlier query.

What could be going wrong any idea?

Thanks and best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Prasanna Naik,

Thanks for your reply.

It seems a bit weird, and I have no idea about the phenomenon now.

In my opinion, maybe you can do these tests on the OM13092 as I did, as I hadn't encountered the phenomenon you explained.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

| ADC channel | ADC output | |

| Min | Max | |

| ADC0_4 | 0 | 10 |

| ADC0_5 | 0 | 6 |

| ADC0_6 | 0 | 5 |

Experiment 2: 1.65V DC generated through a Voltage divider circuit of 10K each fed to channel ADC0_4

| ADC Channel | ADC Output | |

| Min | Max | |

| ADC0_5 | 2041 | 2053 |

Card 1:

| Input Voltage(V) | ADC Channel | With PE Micro | Without PE MIcro | ||

| Min | Max | Min | Max | ||

| 1.65 V (DC) | ADC0_0 | 2014 | 2075 | 2047 | 2051 |

| ADC0_4 | 2020 | 2064 | 2045 | 2054 | |

| ADC0_5 | 2032 | 2058 | 2046 | 2051 | |

| ADC0_6 | 2016 | 2060 | 2048 | 2056 | |

| ADC0_7 | 2021 | 2056 | 2046 | 2052 | |

| ADC0_8 | 2018 | 2051 | 2041 | 2048 | |

Card 2:

| Input Voltage(V) | ADC Channel | With PE Micro | Without PE MIcro | ||

| Min | Max | Min | Max | ||

| 1.65 V (DC) | ADC0_0 | 2010 | 2066 | 2046 | 2052 |

| ADC0_4 | 2035 | 2061 | 2047 | 2054 | |

| ADC0_5 | 2031 | 2062 | 2045 | 2051 | |

| ADC0_6 | 2025 | 2059 | 2050 | 2056 | |

| ADC0_7 | 2019 | 2056 | 2046 | 2052 | |

| ADC0_8 | 2037 | 2049 | 2041 | 2048 | |

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @Jeremy,

Any update on the above query?

Thanks & best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Prasanna Naik,

Thanks for your reply.

After having a review of the schematic, I've not found something wrong with it, and I hope I can dig deeper later.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeremy,

Any update on the issue?

Thanks & best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Until now, I've not encountered a similar phenomenon as you mentioned when running the code on OM13092 for testing.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeremy,

On bypassing adc calibration, the adc seems to be working fine. Usually we provide adc calibration at power up so that offset will be calibrated but this observation seems strange.

Thanks and best regards,

Prasanna

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeremy,

Any update on the query?

Thanks & best regards,

Prasanna