- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisソフトウェア開発キット

- :

- Re: BOARD_BootClockRUN for MK22FN128VLH10

BOARD_BootClockRUN for MK22FN128VLH10

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

BOARD_BootClockRUN for MK22FN128VLH10

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I faced a trouble with the configuration of the BOARD_BootClockRUN for MK22FN128VLH10.

I want to configure MCG mode FEE, FLL output 80MHz, Core clock 80MHz, Bus clock 40MHz, Flash clock 20MHz.

IDE: KDS 3.2

SDK: 2.1

MCU: MK22FN128VLH10

How to configure BOARD_BootClockRUN for 80MHz in MK22FN128VLH10?

Best Regards,

Frank Yang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no hardware problem for Oscillator (OSC).

This target board is good to operate with KSDK 1.3.

I think your SDK has a problem.

Clock operation is not good with SKD 2.1 in the same hardware condition.

but Clock operation is good with KSDK 1.2, KSDK 1.3 and ProcessorExpert in the same hardware condition.

and this hardware has been used for 1 year and half. and there is no problem yet at the point of clock operation.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

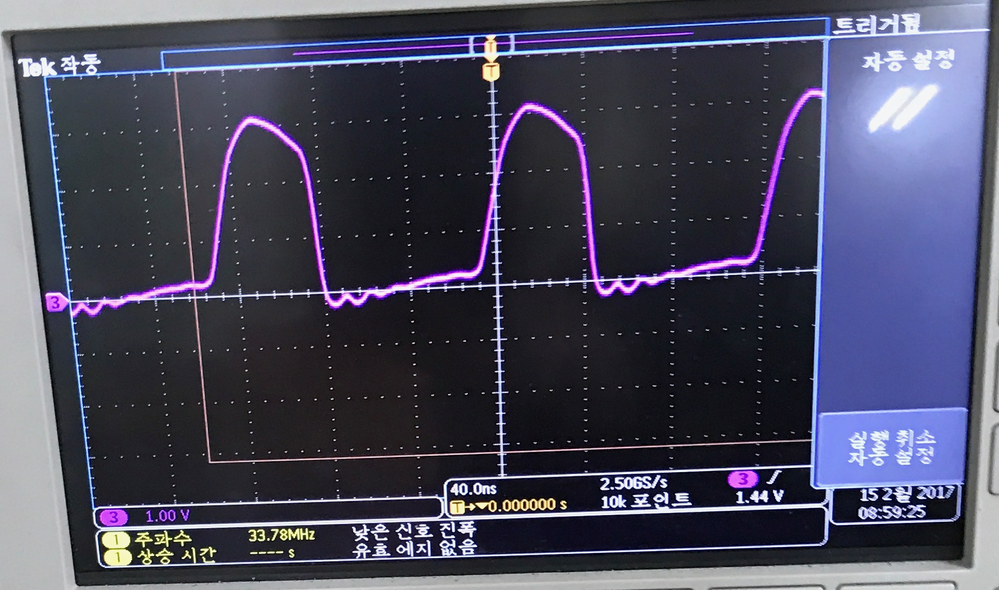

Clock is generated but it is not sine wave and wrong operation example code.

It is waveform from EXTAL0 pin.

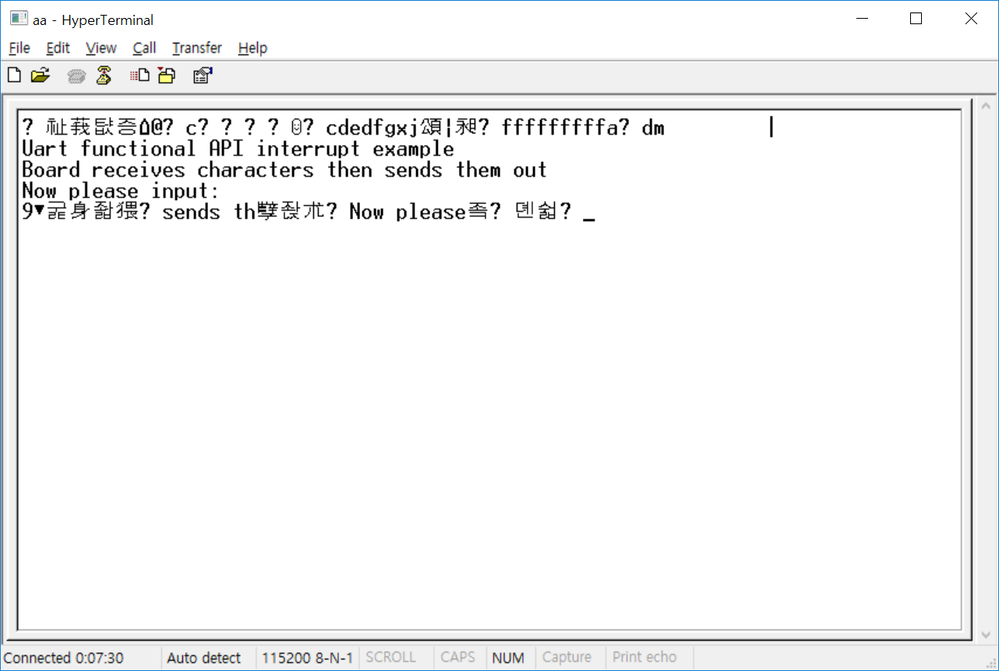

ther broken chracteristics of the uart interrupt example in SDK 2.1.

Attached is the generated clock configuration tool file:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Frank,

It seems to be an issue of the oscillator circuit design. Please, verify the design according to reference manual of the MK22FN128xxx10 - Oscillator (OSC) chapter and datasheet of the crystal oscillator. You must use the correct crystal oscillator connection and components. You can also find additional details in the Crystal Oscillator Troubleshooting Guide (see http://www.nxp.com/assets/documents/data/en/application-notes/AN3208.pdf).

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I generated the code from Clock Tool in your web site.

Even thought generating the code and X-tal hardware was verified with processorExpert in the past, it didn't work.

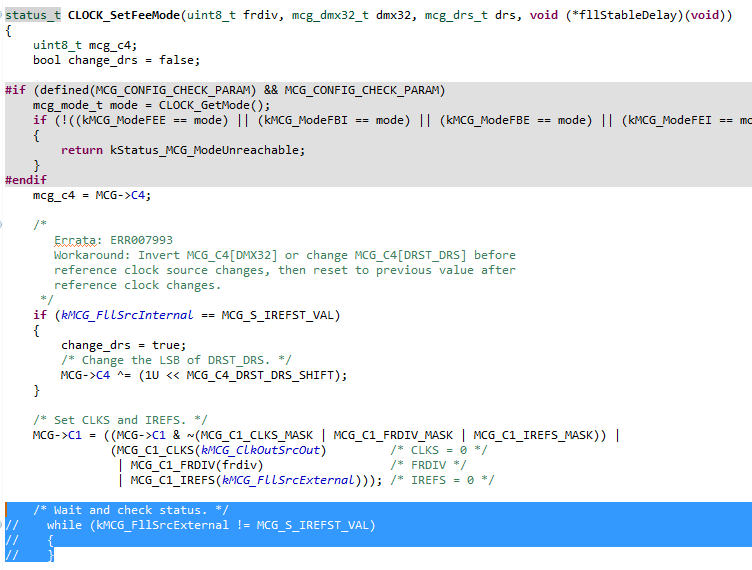

Now, it works after marking // some lines: wait and check status as following: I think it is not normal.

status_t CLOCK_SetFeeMode(...)

{

...

/* Wait and check status. */

//while(kMCG_FllSrcExternal != MCG_S_IREFST_VAL)

//{

//}

...

}

Clock Frequency is nothing at probe to x-tal hardware, EXTAL0, XTAL0.

I attached the files which was generated in you web site.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

After choosing OSC mode : Using oscillator with external crystal (low power)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Frank,

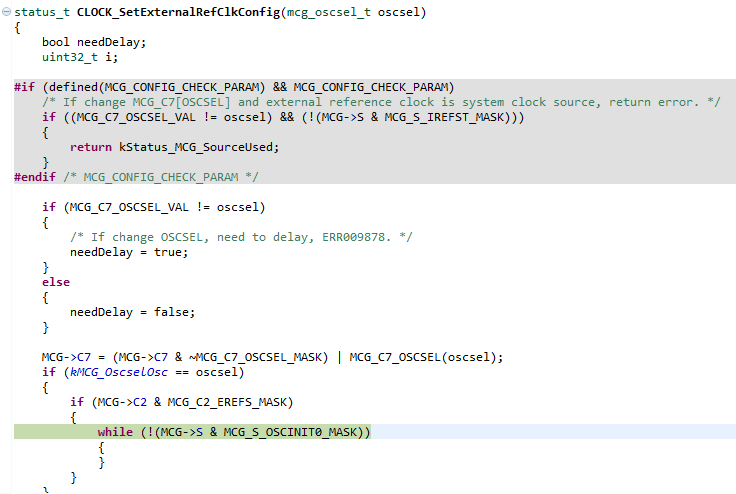

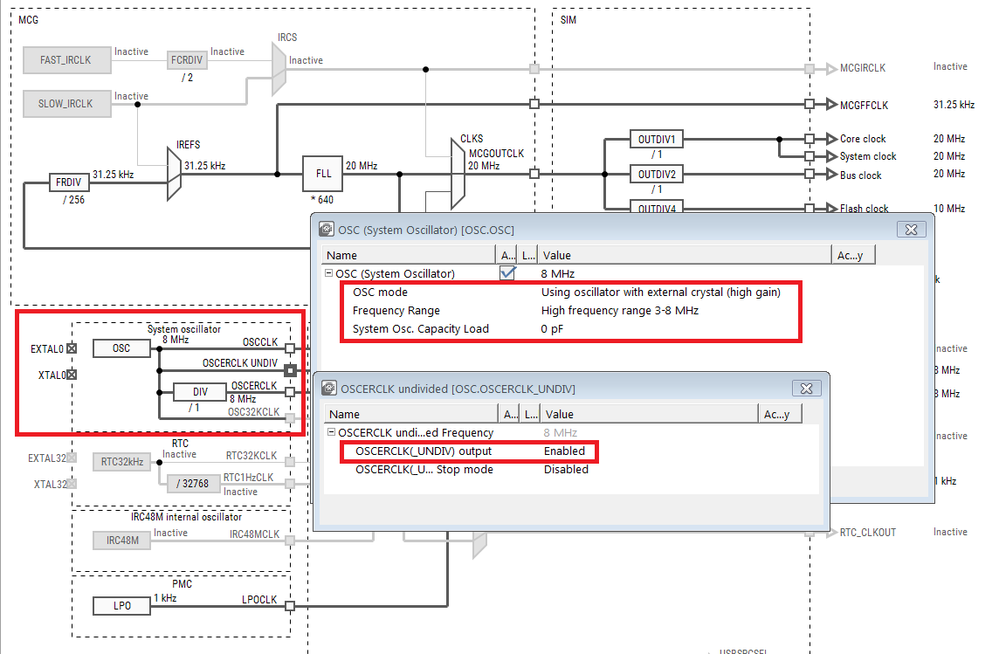

I have analyzed you source code and you have selected incorrect configuration of the OSC. When you connect external crystal you must select an external crystal mode and frequency range (and capacity if required). In your application the external reference clock is selected (EXTAL0 pin only is used).

See the following screenshot for details:

Note:

SDK 2.0 contains a defect - when FEE mode is selected and OSCERCLK is disabled the initialization code does not finished (a while loop does not finish due to an error). Enable OSCERCLK as a workaround for this issue.

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Frank,

i think you can use the code to set the MCG in FEE mode, but you have to connect the crystal to Extal/Xtal or Extal32/Xtal32 pins and know the clock frequency of crystal, so that you can figure out frdiv, drs parameters.

void BOARD_BootClockRUN(void)

{

CLOCK_SetSimSafeDivs();

CLOCK_InitOsc0(&g_defaultClockConfigRun.oscConfig);

CLOCK_SetXtal0Freq(BOARD_XTAL0_CLK_HZ);

/* CLOCK_BootToPeeMode(g_defaultClockConfigRun.mcgConfig.oscsel, kMCG_PllClkSelPll0,

&g_defaultClockConfigRun.mcgConfig.pll0Config);*/

CLOCK_BootToFeeMode(

mcg_oscsel_t oscsel, uint8_t frdiv, mcg_dmx32_t dmx32, mcg_drs_t drs, void (*fllStableDelay)(void))

CLOCK_SetInternalRefClkConfig(g_defaultClockConfigRun.mcgConfig.irclkEnableMode,

g_defaultClockConfigRun.mcgConfig.ircs, g_defaultClockConfigRun.mcgConfig.fcrdiv);

CLOCK_SetSimConfig(&g_defaultClockConfigRun.simConfig);

SystemCoreClock = g_defaultClockConfigRun.coreClock;

}

Hope it can help you

BR

xiangjun Rong