- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- processor expert bug - FlexBus ALE is taking more than one clock

processor expert bug - FlexBus ALE is taking more than one clock

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

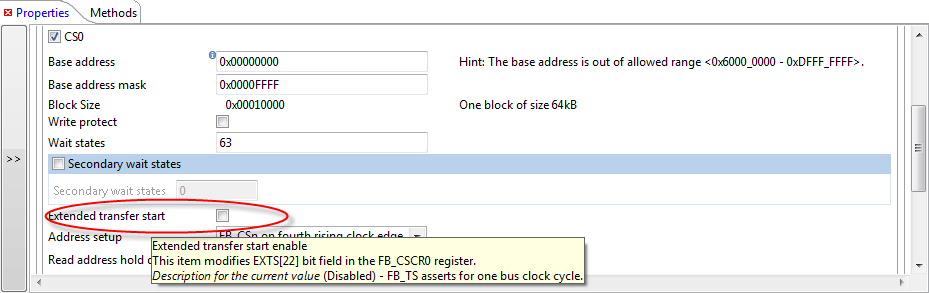

I am trying to setup Flexbus using processor expert and I the ALE size is multiple clocks.

the device I am using is mk20fx512vmd12

and I am using Kinetis Design Studio Version: 2.0.0 Eclipse Version: Kepler (4.3.2)

Here is my flexbus init from cpu.c

/* SIM_SCGC7: FLEXBUS=1 */

SIM_SCGC7 |= SIM_SCGC7_FLEXBUS_MASK;

/* Initialization of the ExternalBus module */

/* SIM_SOPT2: FBSL=0 */

SIM_SOPT2 &= (uint32_t)~(uint32_t)(SIM_SOPT2_FBSL(0x03));

/* FB_CSAR0: BA=0xA000,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

FB_CSAR0 = FB_CSAR_BA(0xA000);

/* FB_CSCR0: SWS=0,??=0,??=0,SWSEN=0,EXTS=1,ASET=0,RDAH=0,WRAH=0,WS=0,BLS=1,AA=1,PS=1,BEM=0,BSTR=0,BSTW=0,??=0,??=0,??=0 */

FB_CSCR0 = FB_CSCR_SWS(0x00) |

FB_CSCR_EXTS_MASK |

FB_CSCR_ASET(0x00) |

FB_CSCR_RDAH(0x00) |

FB_CSCR_WRAH(0x00) |

FB_CSCR_WS(0x00) |

FB_CSCR_BLS_MASK |

FB_CSCR_AA_MASK |

FB_CSCR_PS(0x01);

/* FB_CSMR0: BAM=0x0F,??=0,??=0,??=0,??=0,??=0,??=0,??=0,WP=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,V=1 */

FB_CSMR0 = (FB_CSMR_BAM(0x0F) | FB_CSMR_V_MASK);

/* FB_CSMR1: V=0 */

FB_CSMR1 &= (uint32_t)~(uint32_t)(FB_CSMR_V_MASK);

/* FB_CSMR2: V=0 */

FB_CSMR2 &= (uint32_t)~(uint32_t)(FB_CSMR_V_MASK);

/* FB_CSMR3: V=0 */

FB_CSMR3 &= (uint32_t)~(uint32_t)(FB_CSMR_V_MASK);

/* FB_CSMR4: V=0 */

FB_CSMR4 &= (uint32_t)~(uint32_t)(FB_CSMR_V_MASK);

/* FB_CSMR5: V=0 */

FB_CSMR5 &= (uint32_t)~(uint32_t)(FB_CSMR_V_MASK);

Please advise,

Best regards,

Zohar

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

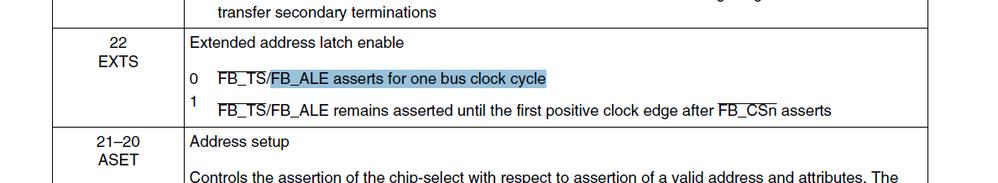

Hi Zohar golan,

I noticed you set EXTS=1, so that might be the root cause, you have to set it as zero to let FB_ALE just asserts for one bus clock cycle, please refer to the following for details.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Zohar golan,

I noticed you set EXTS=1, so that might be the root cause, you have to set it as zero to let FB_ALE just asserts for one bus clock cycle, please refer to the following for details.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------