- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: XRDC code example

XRDC code example

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am working on a communication driver for Rayleigh and have to implement a safety feature using the Extended Resource Domain Controller (XRDC). As the Reference Manual is ambiguous in this regard (and the web isn't much more helpful), I was wondering if anyone has any code example using XRDC to share. It would be very helpful for understanding the way it is intended to work.

Thanks,

Bogdan

NXP Romania

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bogdan,

I got manual of the Rayleigh device.

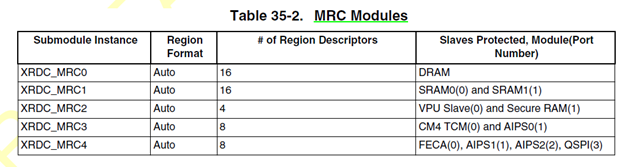

Here is Memory Region Controller assignment to protected slaves.

Provided you don't configure access to XRDC prior it is enabled then access will not be granted.

In order to allow access to XRDC (placed @ AIPS-0, slots 28-to-31), I think you should do these steps:

==

1. Program XRDC_MRC3 (XRDC_MRGD_Wx_48) to allow access into AIPS0 address range for given domainID

2. Program XRDC_PAC0 (XRDC_PDAC_Wx_028 - XRDC_PDAC_Wx_031) to allow access to all four XRDC peripheral slots for given domainID

3. Some registers, for example XRDC_CR requires core master to use Secure Privileged access attribute to be able to read it or modify and therefore you might need to setup also respective XRDC_PID for generating secure access attribute { PID[5] = 1 }.

Unfortunately, I cannot try practically on board this setting and therefore my advice is pure theoretical based on understanding XRDC block IP.

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bogdan,

I don't have software example but more recently spent some time to understand it so hopefully will be able to help.

Do you have any specific question?

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

Thanks for the reply.

After reading the manual multiple times, I came up with a simple test case, just to make sure it works the way I think it does: I assigned all of the bus masters to the same domain, then gave everyone full access rights on the whole memory and all the peripherals. This is what I did (in the exact order):

1. assigned domain id 1 to all bus masters and set the validity bits

- wrote 0x80000001 to all XRDC_MDA_W0_n registers

2. gave every domain full access rights to all the peripherals and set the validity bits

- wrote 0x00FFFFFF to all XRDC_PDAC_W0_n registers

- wrote 0x80000000 to all XRDC_PDAC_W1_n registers

3. configured a memory region containing the whole range of memory addresses, set full access rights for all domains and set the validity bit

- wrote 0x00000000 to XRDC_MRGD_W0_0 (start address)

- wrote 0xFFFFFFFF to XRDC_MRGD_W1_0 (end address)

- wrote 0x00FFFFFF to XRDC_MRGD_W2_0 (access policy)

- wrote 0x80000000 to XRDC_MRGD_W3_0 (validity bit)

4. set the global enable bit in the control register

- wrote 0x00000001 to XRDC_CR

It all seemed to go well until the global enable, at which point I got denied any access to the memory or memory-mapped I/O. I used a Lauterbach T32 debugger to run my application step-by-step and test memory availability. I must have missed some step, or wrote the registers in the wrong order. I'd be grateful if you could point out the mistake.

Thanks for your time.

Best regards,

Bogdan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bogdan,

my xRDC knowledge is pure theoretical in this stage. Nevertheless, please refer to my comments for given steps in your code:

1. write 0x80000001 to XRDC_MDA_W0_0 register

This shall be enough to assign Master0 to DomainID=1; If you need to assign the same Master to more domains you need perform writes to other registers

2. Shall be OK.

3. I believe you need to setup more MRGDs. Memory Region Controller can have up to 16 MRGDs for each MRC to protect some memory resource, for example XRDC_MRC0 can be for protecting access to Flash and XRCD_MRC1 for protecting access to RAM. Can you please point me to the Rayleigh part number so I can look at XRDC setup on this particular part?

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

Thanks for your input. I tried to assign a domain just to the CM4 core (MDAC0/MDAC1 on Rayleigh) but I still have some trouble with memory region descriptors. I found that MRC1 seems to be responsible for SRAM, but it doesn't actually matter if I configure any descriptors. After I enable XRDC I'm always able to access just the SRAM and nothing else - not even XRDC (trying to disable it generates a bus error). This struck me as rather odd.

I tried to find some clear setup instructions or code for Rayleigh (or similar e.g. I.MX6) but with no luck so far. The part number you requested is 0N98K P63242 and the ID is PAC58R5XXK1YMX6.

Best regards,

Bogdan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bogdan,

I got manual of the Rayleigh device.

Here is Memory Region Controller assignment to protected slaves.

Provided you don't configure access to XRDC prior it is enabled then access will not be granted.

In order to allow access to XRDC (placed @ AIPS-0, slots 28-to-31), I think you should do these steps:

==

1. Program XRDC_MRC3 (XRDC_MRGD_Wx_48) to allow access into AIPS0 address range for given domainID

2. Program XRDC_PAC0 (XRDC_PDAC_Wx_028 - XRDC_PDAC_Wx_031) to allow access to all four XRDC peripheral slots for given domainID

3. Some registers, for example XRDC_CR requires core master to use Secure Privileged access attribute to be able to read it or modify and therefore you might need to setup also respective XRDC_PID for generating secure access attribute { PID[5] = 1 }.

Unfortunately, I cannot try practically on board this setting and therefore my advice is pure theoretical based on understanding XRDC block IP.

Kind regards,

Martin M.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

Thank you for your input. This seems to do the trick. I had previously tried it with all region descriptors enabled and it didn't work, so it most certainly was the PID register. Thanks again.

Best regards,

Bogdan