- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: SDRAM problems when flash is read-protected

SDRAM problems when flash is read-protected

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi guys!

I'm using a Tower with Kinetis K65, and I managed some time ago to configure SDRAM and use it with not too much problems, but today I faced a very very strange issue.

Everything works fine when FTFE_FSEC is 0xFE, but when I change SEC bits to != 0b10, the device doesn't boots up.

Of course, under this circumstance I can't debug, as on-board flash is read-protected. After several tests, I found that when I disable the SDRAM initialization, the device works fine.

Anyone has seen something similar before? Can you give any indication of what can be wrong?

I have tested several combinations of FTFE_FSEC[SEC] bits. No positive results when flash external read is disbled.

This is my latest setting (in startup_MK65F18.S) :

/* Flash Configuration */

.section .FlashConfig, "a"

.long 0xFFFFFFFF

.long 0xFFFFFFFF

.long 0xFFFFFFFF

.long 0xFFFFFFBF

I'm using KDS with MQX. SDRAM configuration is done with ProcessorExpert (and it works fine when FTFE_FSEC[SEC] == 0b10)

Thank you in advance :smileyhappy:

EDIT: Device is able to boot (although SDRAM is not working) when I comment this two lines in SDRAM_Init.c

/* Write to an appropriate SDRAM address generates the pall command to the SDRAM block */

//*((uint8_t *)CS0_SDRAM_BASE_ADDRESS) = 0x00U;

and

/* Write access to the SDRAM address space generates the MRS command to that SDRAM */

//*((uint32_t *)CS0_MRS_COMMAND_ADDRESS) = 0x00000000U;

It seems that this two lines are attempting to write to SDRAM address, and I suspect that this is causing any kind of CPU fault.

It's very strange... when I set FTFE_FSEC[SEC] to 0b10 everything works just fine...

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carlos,

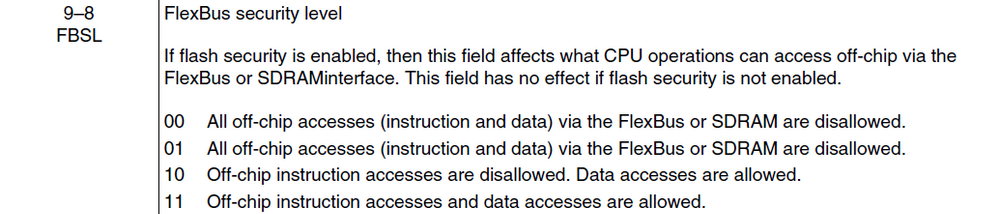

This is related to the security level on Kinetis. Please see following description from K65 RM.

9.3.1 Security interactions with FlexBus and SDRAM controller

When flash security is enabled, SIM_SOPT2[FBSL] enables/disables off-chip accesses

through the FlexBus and the SDRAM interfaces. The FBSL bitfield also has an option to

allow opcode and operand accesses or only operand accesses.

Default configuration for FBSL disallow Flexbus or SDRAM access. So you need to program FBSL to appropriate configuration.

Hao

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have tested SDRAM example posted in Re: can't read data back from SDRAM , and the same issue happens.

I have modified it a little, to print a message on console when SDRAM tests are performed -> it works fine when flash is not protected and fails when flash is protected.

Please, could anyone tell me if faced the same problem and if could resolve it?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carlos,

This is related to the security level on Kinetis. Please see following description from K65 RM.

9.3.1 Security interactions with FlexBus and SDRAM controller

When flash security is enabled, SIM_SOPT2[FBSL] enables/disables off-chip accesses

through the FlexBus and the SDRAM interfaces. The FBSL bitfield also has an option to

allow opcode and operand accesses or only operand accesses.

Default configuration for FBSL disallow Flexbus or SDRAM access. So you need to program FBSL to appropriate configuration.

Hao

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

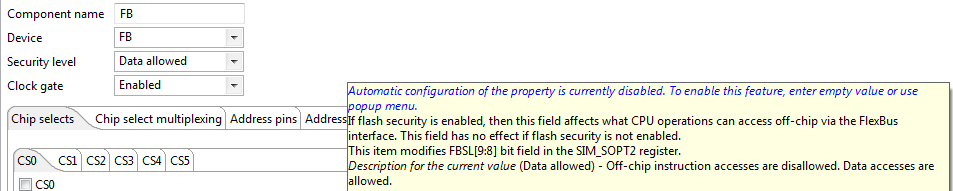

Thank you, Hao, for your answer!

I found the place to configure this setting in ProcessorExpert (in FB component)

Configuring FBSL to the desired value solves the issue. Now I'm able to access SDRAM data with internal flash protection.

Thank you for your precise answer :smileyhappy: