- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- K64 ADC Sample and Conversion Time

K64 ADC Sample and Conversion Time

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

K64 ADC Sample and Conversion Time

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am trying to understand the Sample Time and Conversion Time for the K64 ADC as described in 35.4.4.5 Sample time and total conversion time.

Consider a simple example case:

CFG1[ADLPC] = 0 (normal power configuration)

CFG1[ADIV] = 00 (divide ratio is 1, ADCK rate is the Bus Clock rate)

CFG1[ADLSMP] = 0 (short sample time)

CFG1[MODE] = 10 (16bit)

CFG1[ADICLK] = 00 (Bus Clock)

CFG2[ADHSC] = 0 (normal conversion sequence)

SC1n[DIFF] = 0 (single-ended)

SC3[AVGE] = 0 (AverageNum = 1)

In this case, I expect the sample time to be 6 ADCK cycles on a first or single conversion, and 4 ADCK cycles on subsequent conversion.

The total conversion time is given by: SFCAdder + AverageNum*(BCT + LSDAdder +HSCAdder).

conversion time = (5 ADCK cycles + 5 bus clock cycles) + 1*(25 ADCK cycles + 0 + 0)

conversion time = 35/f_BUS

My question is, is the expression for conversion time the total time between samples? If so, where is the sample time reflected in the total conversion time? The SFCAdder from Table 35-3 (5 ADCK cycles + 5 bus clock cycles) is not the same as the Sample time listed in the sample time table (6 or 4 ADCK cycles):

Alternatively, can the total time between samples be expressed as a sum of t_sample and t_conversion? Is there a timing diagram available anywhere that shows the sampling and conversion phases?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @aberger ,

Thanks for your post and sorry for the delay.

Is there a timing diagram available anywhere that shows the sampling and conversion phases?

---> I'm sorry. I can't find such a timing diagram in any of the documents.

Alternatively, can the total time between samples be expressed as a sum of t_sample and t_conversion?

---> Actually, that's not the way it works. The total conversion time refers to the overall duration, which already includes the sampling time.

Is the expression for conversion time the total time between samples? If so, where is the sample time reflected in the total conversion time?

---> Based on the description in the reference manual, I believe that the expression for the conversion time includes the sample time.

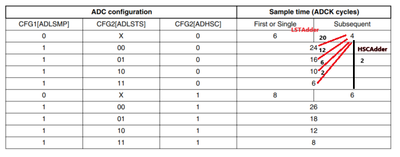

According to the RM, the sample time is determined by the ADC configuration. There is a concept of base sample time, which is four ADCK cycles.

For the first conversion, there is a 2-cycle adder on top of the base sample time of four ADCK cycles. And for high-speed conversions, there is an additional 2-cycle adder for any conversion.

Please refer to the following two screenshots. After removing the base sample time of 4 ADCK from the sample time in Figure 1, you'll find that the Long Sample Time Adder (LSTAdder) and the High-Speed Conversion Time Adder (HSCAdder) are consistent with those in Figure 2. These two adders are already reflected in the formula for the total conversion time.

As for the base sample time, I guess it should be included in the Base conversion time(BCT). So it's within the parentheses of the formula and needs to be multiplied by AverageNum.

The SFCAdder from Table 35-3 (5 ADCK cycles + 5 bus clock cycles) is not the same as the Sample time listed in the sample time table (6 or 4 ADCK cycles).

---> SFCAdder (Single or first continuous time adder) is not the same concept as the sample time. SFCAdder includes the time for the ADC to start up and get ready, and it is only counted once during a continuous conversion process. It is not the sample time. Therefore, it is normal that it is different from the sample time (6 or 4 ADCK cycles) listed in the sample time table.

Hope it can help you. If you have any further questions or need more information, please let me know.

BRs,

Celeste

--------------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the "ACCEPT AS SOLUTION" button. Thank you!

--------------------------------------------------------------------------------------------------------------------------