- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- K32 L Series Microcontrollers

- :

- Re: Device Boot Mode sequence for K32L2B31VFM0A

Device Boot Mode sequence for K32L2B31VFM0A

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Device Boot Mode sequence for K32L2B31VFM0A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Can you provide a Boot Mode sequence timing diagram? if not possible then please suggest how much time we have to put a logic low level on reset and boot config[NMI] pin.

Thanks

Nikunj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nikunj,

Reset has two type, POR reset and other reset source reset, include reset pin reset.

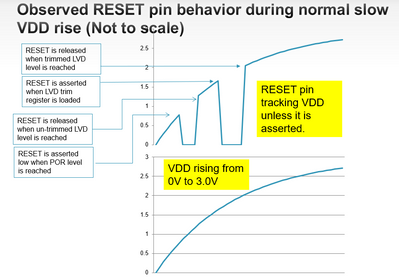

If it's a POR reset, you'd better keep reset pin low till VDD arrive at 1.8V, 1.54v at least. After that LVD will hold reset signal till 1.8V. After a POR event, amount of time from the point VDD reaches 1.8 V to execution of the first instruction is 300us.

If it's a reset pin reset, reset pin should be hold over 1 bus clock. Reset pin can use filter. Please see 6.2.2.1.1 in reference manual.

To make system stable, you should pull-up reset pin with a 4.7k~10k resistor. And don't connect capacitor to NMI pin.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

we are using 9600 baudrate for UART. There is no application firmware inside the device,we observe that if firmware loading is stopped due to some issue we have to always erase the device using j link flash. Then after we receive a valid ping response and the firmware loading is complete inside the device.

Please suggest how to resume firmware load in the device if in boot mode using host((nRF52840) the first time.

Thanks

-Nikunj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

can you provide a low-level time period for the BootCFG[NMI] pin?