- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- CodeWarrior for MCU

- :

- ADC Scan Control Register problem on MC56F84789

ADC Scan Control Register problem on MC56F84789

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC Scan Control Register problem on MC56F84789

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

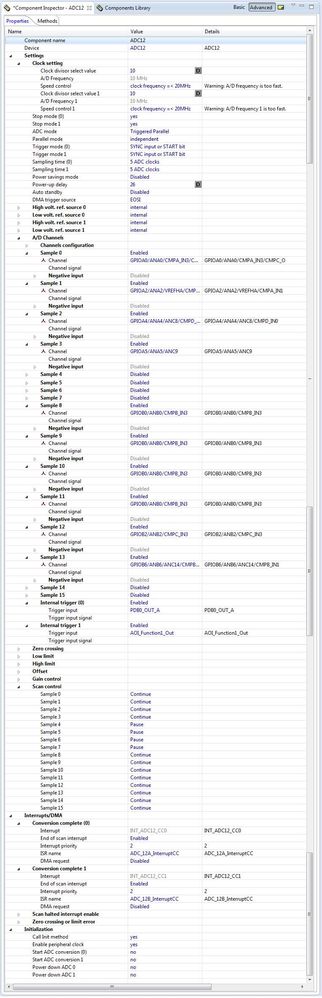

We're using ADC12 in independet parallel triggerd mode.

We want to acquire 6 samples on ADCB triggered via PDB1 (4 sync) syncing with ADC12_SCTRL in one PWM 8Khz cycle. At the end of ADC scan we want to have ADC ISR

Sample 0 -> ANB0

Sample 1 -> ANB0

Sample 2 -> ANB0

Sample 3 -> ANB0

Sample 4 -> ANB2

Sample 5 -> ANB6

PWM period 125us

PDB1 sync at 1us, 20us, 40us and 80us

ADC12_SCTRL = 0x00F0

Reading the reference manual we understand that :

ADC acquires the sample 0 and then it halts the scan

ADC acquires the sample 1 and then it halts the scan

ADC acquires the sample 2 and then it halts the scan

ADC acquires the samples 3-4-5 in continuous mode.

After this triggered the ADC end of scan event ISR.

In our case instead at every sync pulse the ADC acquires always the sample and halted. The samples 3-4-5 are not acquired in one sync. We have the ISR trigger every 6 sync, verfied with the oscilloscope.

We tried to change ADC12_SCTRL but nothing changed.

We note that when you set the "scan control" bit for sample 0 "as pause", the remaining scan control bit are not managed. Basically, in any way, we can't to group multiple samples in a single sync pulse.

We use the AN4608 and the AN4583 as reference. The difference in the application note AN4608 is that it 's used the scan control but in simultaneous parallel triggred mode.

Thanx for any help!

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

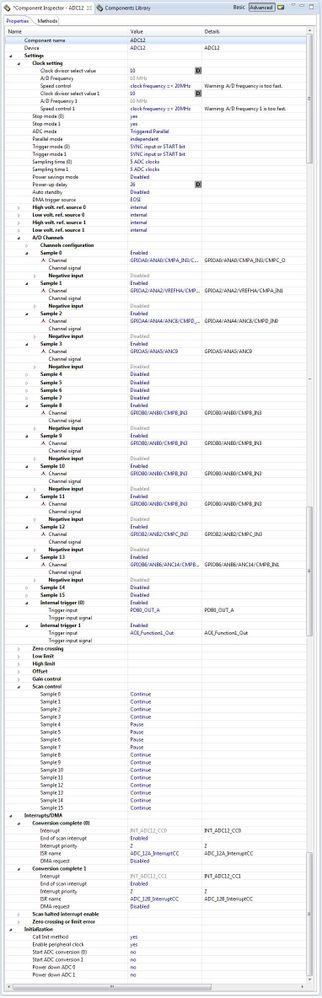

I changed from independent mode to simultaneous mode and it works correctly!!!

As we desired the last three samples are acquired together at the last sync of PDB1?

We believe that the problem is present only if the independent mode is set.

Can you perform some checks?

Thanx for any help!

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Marco

According to your PE configurations, the samples 8~11 are got from ANB0.

Sample 8 -> ANB0

Sample 9 -> ANB0

Sample 10 -> ANB0

Sample 11 -> ANB0

Sample 12 -> ANB2

Sample 13 -> ANB6

Your intention is like below:

PDB1 at 1us ==> Sample 8 -> ANB0 ==> Halt

PDB1 at 20us ==> Sample 9 -> ANB0 ==>Halt

PDB1 at 40us ==>Sample 10 -> ANB0 ==>Halt

PDB1 at 80us ==> Sample 11 -> ANB0/ Sample 12 -> ANB2 / Sample 13 -> ANB6 ==>End

And you set the ADC work in independent triggered parallel mode. In your source code, you have configured ADC12_SCTRL as 0x00F0, the ADCB should work as below:

SC4 = 1 : Sample 8 ==> Halt

SC5 = 1 : Sample 9 ==> Halt

SC6 =1 : Sample 10 ==> Halt

SC7 =1 : Sample 11 ==> Halt

Best Regards

Fiona Kuang

Technical Information & Commercial Support

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Fiona

I wanted to add an additional test to show that something is not working!

We configured ADC12_SCTRL as 0xFFEF, the ADCB should word as below:

SC4 = 0 : Sample 8 ==> Continue

SC5 = 1 : Sample 9 ==> Halt

SC6 = 1 : Sample 10 ==> Halt

SC7 = 1 : Sample 11 ==> Halt

SC12 = 1 : Sample 12 ==> Halt

SC13 = 1 : Sample 13 ==> Halt

SC14 = 1 : Sample 14 ==> Halt

SC15 = 1 : Sample 15 ==> Halt

We set the remaining bits of ADCA to one although not necessary.

We would expect that except the first acquires of ADCB, the others are separated by a pause.

Instead, it happens that every PDB1 synchronism the ADCB acquired all samples and than the event end of ACD scan triggered.

I think we are doing something wrong or there may be an error at microcontroller level!

Thanx for any help!

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

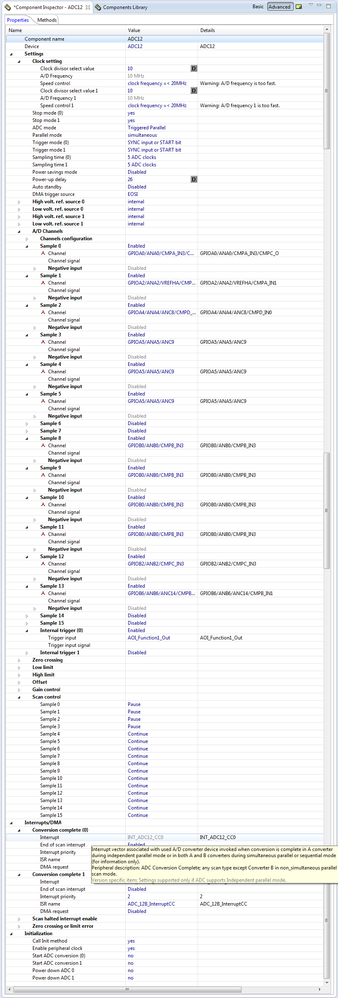

Hello Fiona

thanks for your reply!

I confirm that the samples are those ranging from 8 to 13. In my description I wrote from 0 to 5 referring to the independent group ANB.

You have correctly interpreted our needs. But unfortunately the last step does not work:

We want that:

PDB1 at 80us ==> Sample 11 -> ANB0 / Sample 12 -> ANB2 / Sample 13 -> ANB6 ==> End

We configured ADC12_SCTRL as 0x00F0, the ADCB should word as below:

SC4 = 1 : Sample 8 ==> Halt

SC5 = 1 : Sample 9 ==> Halt

SC6 = 1 : Sample 10 ==> Halt

SC7 = 1 : Sample 11 ==> Halt

SC12 = 0 : Sample 12 ==> Continue

SC13 = 0 : Sample 13 ==> Continue

SC14 = 0 : Sample 14 ==> Continue

SC15 = 0 : Sample 15 ==> Continue

Than, we tried to configured ADC12_SCTRL as 0x0070, the ADCB should word as below:

SC4 = 1 : Sample 8 ==> Halt

SC5 = 1 : Sample 9 ==> Halt

SC6 = 1 : Sample 10 ==> Halt

SC7 = 0 : Sample 11 ==> Continue

SC12 = 0 : Sample 12 ==> Continue

SC13 = 0 : Sample 13 ==> Continue

SC14 = 0 : Sample 14 ==> Continue

SC15 = 0 : Sample 15 ==> Continue

Than, we tried to configured ADC12_SCTRL as 0x2070, the ADCB should word as below:

SC4 = 1 : Sample 8 ==> Halt

SC5 = 1 : Sample 9 ==> Halt

SC6 = 1 : Sample 10 ==> Halt

SC7 = 0 : Sample 11 ==> Continue

SC12 = 0 : Sample 12 ==> Continue

SC13 = 1 : Sample 13 ==> Halt

SC14 = 0 : Sample 14 ==> Continue

SC15 = 0 : Sample 15 ==> Continue

In all three cases not operating as desired!

The event end of ACD scan triggered every six synchronization hits of module PDB1 (monitored with oscilloscope). Then, the samples 11, 12, 13 are not acquired together as desired close to 80us

What is the correct configuretation of ADC12_SCTRL to acquire the three samples together?

Thanx for any help!

Marco