- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: IMXRT1170-EVK Debugging started failing with the message: "Target connection failed"

IMXRT1170-EVK Debugging started failing with the message: "Target connection failed"

IMXRT1170-EVK Debugging started failing with the message: "Target connection failed"

Hi,

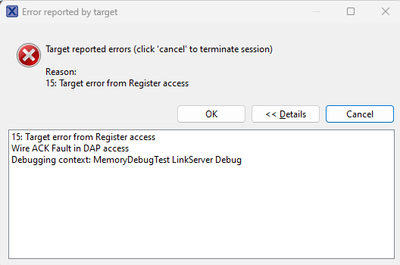

In MCUXPressoIDE while debugging my project, I am getting the following errors as shared in the below images. Please let me know what are configuration settings I am missing here. It was working correct when I am running the hello world program but while I run my project it giving me the errors.

I have shared the images of the errors I am encountering in both XIP mode and SDP mode. please check.

Thanks in advance.

Hi @Naveed,

Please follow the steps described on the following blog post, specifically the "Recovery" and or the "Boot Utility to the Rescue!" sections) and let me know if this resolves your issue: https://mcuoneclipse.com/2019/01/02/regaining-debug-access-of-nxp-i-mx-rt1064-evk-executing-wfi/

Hi EdwinHZ,

I have checked and observed that in my iMXRT1170-EVK, I am able to debug all the SDK example projects and getting the output as expected. But when I tried to run my project which I have created using MCUXpresso with all my pins and configuration I am getting this error.

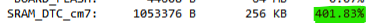

In this console shown SRAM_DTC_cm7 is used to 401.83%.(SRAM_DTC_cm7 overflowed).

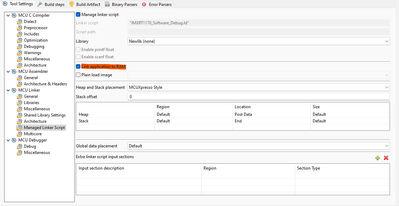

To resolve this issue we have changed the memory settings to BOARD_SDRAM as below.

Also,

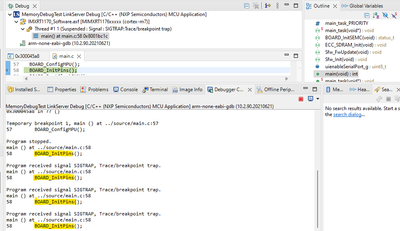

After making these changes I am to build my code with zero errors. And tried to debug my code but encountered with the below error.

This error is the topic of my ticket to be resolve for which I have attached the images of the errors before also. Please let me know what am I missing when I created my project? Do I need to configure anything with respect to the memory configuration? How to solve this issue?

This is my preprocessor settings.

Thanks in advance.

Hi @Naveed,

It's difficult to say since this is most likely an issue from your code. I believe your code might be causing the MCU to enter a state where it is no longer accessible by the debugger. Could you please clarify:

- Do you see these error before or after flashing the MCU with your code? Perhaps the first time you program the MCU with your code there is not issue, but the consecutive times there is a problem?

- Are you able to program the MCU with any SDK example code after it was programmed with your code?

- Does your code send the MCU to a low power state?

- Are you able to program the MCU with your code after following the recovery process I shared with your earlier?

Thanks for your clarifications,

Edwin.

Hi Edwin,

Thanks for your reply.

- Do you see these error before or after flashing the MCU with your code? Perhaps the first time you program the MCU with your code there is not issue, but the consecutive times there is a problem?

I am getting these errors before flashing my code. When I run my code I am getting these issue not with the SDK examples.

- Are you able to program the MCU with any SDK example code after it was programmed with your code?

No, After I tried to debug my code I am not able to program any example code on the board. But by changing the mode from XIP to SDP and running helloworld program and changing the mode back to XIP I am able to run the SDK example code successfully on the board.

- Does your code send the MCU to a low power state?

No. There are no any configuration I have done here for it specifically.

- Are you able to program the MCU with your code after following the recovery process I shared with your earlier?

No. I am not able to run my code, but by changing the mode from XIP to SDP and running helloworld program and changing the mode back to XIP I am able to run the SDK example code successfully on the board.

____________________________________________________________________________

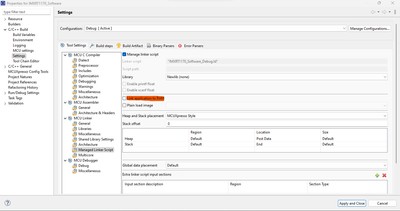

I have created a new project to run my code on XIP+SDRAM memory. But my code only uses SDRAM memory not the BOARD_FLASH as shown.

I have check here as I clicked to: link application to RAM so, it is using only SDRAM as attached.

With this I am able to debug bot not able use the step-in and step-over options while debug. If I clicked on step-over/step-in it is stuck on the same line.

I want my code to be run with XIP+SDRAM as in previous case it is only using SDRAM memory. So I have untick the option of : Link application to RAM as shown.

After building with this setting my code is utilizes both XIP and SDRAM as expected.

But when I tried to debug this code, I am again getting this error.

Please let me know where am I missing any configuration, how to configure this memory to work it properly? your inputs will be appreciated.

I have also shared ld files here for your reference.

IMXRT1170_Software_Debug_library.ld

GROUP (

"libgcc.a"

"libc.a"

"libm.a"

"libcr_newlib_none.a"

)

IMXRT1170_Software_Debug_memory.ld

MEMORY

{

/* Define each memory region */

BOARD_FLASH (rx) : ORIGIN = 0x30000000, LENGTH = 0x4000000 /* 64M bytes (alias Flash) */

BOARD_SDRAM (rwx) : ORIGIN = 0x80000000, LENGTH = 0x3000000 /* 48M bytes (alias RAM) */

NCACHE_REGION (rwx) : ORIGIN = 0x83000000, LENGTH = 0x1000000 /* 16M bytes (alias RAM2) */

SRAM_DTC_cm7 (rwx) : ORIGIN = 0x20000000, LENGTH = 0x40000 /* 256K bytes (alias RAM3) */

SRAM_ITC_cm7 (rwx) : ORIGIN = 0x0, LENGTH = 0x40000 /* 256K bytes (alias RAM4) */

SRAM_OC1 (rwx) : ORIGIN = 0x20240000, LENGTH = 0x80000 /* 512K bytes (alias RAM5) */

SRAM_OC2 (rwx) : ORIGIN = 0x202c0000, LENGTH = 0x80000 /* 512K bytes (alias RAM6) */

SRAM_OC_ECC1 (rwx) : ORIGIN = 0x20340000, LENGTH = 0x10000 /* 64K bytes (alias RAM7) */

SRAM_OC_ECC2 (rwx) : ORIGIN = 0x20350000, LENGTH = 0x10000 /* 64K bytes (alias RAM8) */

SRAM_OC_cm7 (rwx) : ORIGIN = 0x20360000, LENGTH = 0x20000 /* 128K bytes (alias RAM9) */

}

/* Define a symbol for the top of each memory region */

__base_BOARD_FLASH = 0x30000000 ; /* BOARD_FLASH */

__base_Flash = 0x30000000 ; /* Flash */

__top_BOARD_FLASH = 0x30000000 + 0x4000000 ; /* 64M bytes */

__top_Flash = 0x30000000 + 0x4000000 ; /* 64M bytes */

__base_BOARD_SDRAM = 0x80000000 ; /* BOARD_SDRAM */

__base_RAM = 0x80000000 ; /* RAM */

__top_BOARD_SDRAM = 0x80000000 + 0x3000000 ; /* 48M bytes */

__top_RAM = 0x80000000 + 0x3000000 ; /* 48M bytes */

__base_NCACHE_REGION = 0x83000000 ; /* NCACHE_REGION */

__base_RAM2 = 0x83000000 ; /* RAM2 */

__top_NCACHE_REGION = 0x83000000 + 0x1000000 ; /* 16M bytes */

__top_RAM2 = 0x83000000 + 0x1000000 ; /* 16M bytes */

__base_SRAM_DTC_cm7 = 0x20000000 ; /* SRAM_DTC_cm7 */

__base_RAM3 = 0x20000000 ; /* RAM3 */

__top_SRAM_DTC_cm7 = 0x20000000 + 0x40000 ; /* 256K bytes */

__top_RAM3 = 0x20000000 + 0x40000 ; /* 256K bytes */

__base_SRAM_ITC_cm7 = 0x0 ; /* SRAM_ITC_cm7 */

__base_RAM4 = 0x0 ; /* RAM4 */

__top_SRAM_ITC_cm7 = 0x0 + 0x40000 ; /* 256K bytes */

__top_RAM4 = 0x0 + 0x40000 ; /* 256K bytes */

__base_SRAM_OC1 = 0x20240000 ; /* SRAM_OC1 */

__base_RAM5 = 0x20240000 ; /* RAM5 */

__top_SRAM_OC1 = 0x20240000 + 0x80000 ; /* 512K bytes */

__top_RAM5 = 0x20240000 + 0x80000 ; /* 512K bytes */

__base_SRAM_OC2 = 0x202c0000 ; /* SRAM_OC2 */

__base_RAM6 = 0x202c0000 ; /* RAM6 */

__top_SRAM_OC2 = 0x202c0000 + 0x80000 ; /* 512K bytes */

__top_RAM6 = 0x202c0000 + 0x80000 ; /* 512K bytes */

__base_SRAM_OC_ECC1 = 0x20340000 ; /* SRAM_OC_ECC1 */

__base_RAM7 = 0x20340000 ; /* RAM7 */

__top_SRAM_OC_ECC1 = 0x20340000 + 0x10000 ; /* 64K bytes */

__top_RAM7 = 0x20340000 + 0x10000 ; /* 64K bytes */

__base_SRAM_OC_ECC2 = 0x20350000 ; /* SRAM_OC_ECC2 */

__base_RAM8 = 0x20350000 ; /* RAM8 */

__top_SRAM_OC_ECC2 = 0x20350000 + 0x10000 ; /* 64K bytes */

__top_RAM8 = 0x20350000 + 0x10000 ; /* 64K bytes */

__base_SRAM_OC_cm7 = 0x20360000 ; /* SRAM_OC_cm7 */

__base_RAM9 = 0x20360000 ; /* RAM9 */

__top_SRAM_OC_cm7 = 0x20360000 + 0x20000 ; /* 128K bytes */

__top_RAM9 = 0x20360000 + 0x20000 ; /* 128K bytes */

IMXRT1170_Software_Debug.ld

INCLUDE "IMXRT1170_Software_Debug_library.ld"

INCLUDE "IMXRT1170_Software_Debug_memory.ld"

ENTRY(ResetISR)

SECTIONS

{

/* MAIN TEXT SECTION */

.text : ALIGN(4)

{

FILL(0xff)

__vectors_start__ = ABSOLUTE(.) ;

KEEP(*(.isr_vector))

/* Global Section Table */

. = ALIGN(4) ;

__section_table_start = .;

__data_section_table = .;

LONG(LOADADDR(.data));

LONG( ADDR(.data));

LONG( SIZEOF(.data));

LONG(LOADADDR(.data_RAM2));

LONG( ADDR(.data_RAM2));

LONG( SIZEOF(.data_RAM2));

LONG(LOADADDR(.data_RAM3));

LONG( ADDR(.data_RAM3));

LONG( SIZEOF(.data_RAM3));

LONG(LOADADDR(.data_RAM4));

LONG( ADDR(.data_RAM4));

LONG( SIZEOF(.data_RAM4));

LONG(LOADADDR(.data_RAM5));

LONG( ADDR(.data_RAM5));

LONG( SIZEOF(.data_RAM5));

LONG(LOADADDR(.data_RAM6));

LONG( ADDR(.data_RAM6));

LONG( SIZEOF(.data_RAM6));

LONG(LOADADDR(.data_RAM7));

LONG( ADDR(.data_RAM7));

LONG( SIZEOF(.data_RAM7));

LONG(LOADADDR(.data_RAM8));

LONG( ADDR(.data_RAM8));

LONG( SIZEOF(.data_RAM8));

LONG(LOADADDR(.data_RAM9));

LONG( ADDR(.data_RAM9));

LONG( SIZEOF(.data_RAM9));

__data_section_table_end = .;

__bss_section_table = .;

LONG( ADDR(.bss));

LONG( SIZEOF(.bss));

LONG( ADDR(.bss_RAM2));

LONG( SIZEOF(.bss_RAM2));

LONG( ADDR(.bss_RAM3));

LONG( SIZEOF(.bss_RAM3));

LONG( ADDR(.bss_RAM4));

LONG( SIZEOF(.bss_RAM4));

LONG( ADDR(.bss_RAM5));

LONG( SIZEOF(.bss_RAM5));

LONG( ADDR(.bss_RAM6));

LONG( SIZEOF(.bss_RAM6));

LONG( ADDR(.bss_RAM7));

LONG( SIZEOF(.bss_RAM7));

LONG( ADDR(.bss_RAM8));

LONG( SIZEOF(.bss_RAM8));

LONG( ADDR(.bss_RAM9));

LONG( SIZEOF(.bss_RAM9));

__bss_section_table_end = .;

__section_table_end = . ;

/* End of Global Section Table */

*(.after_vectors*)

*(.text*)

KEEP(*freertos*/tasks.o(.rodata*)) /* FreeRTOS Debug Config */

*(.rodata .rodata.* .constdata .constdata.*)

. = ALIGN(4);

} > BOARD_SDRAM

_etext = .;

/* DATA section for NCACHE_REGION */

.data_RAM2 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM2 = .) ;

PROVIDE(__start_data_NCACHE_REGION = .) ;

*(.ramfunc.$RAM2)

*(.ramfunc.$NCACHE_REGION)

*(.data.$RAM2)

*(.data.$NCACHE_REGION)

*(.data.$RAM2.*)

*(.data.$NCACHE_REGION.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM2 = .) ;

PROVIDE(__end_data_NCACHE_REGION = .) ;

} > NCACHE_REGION AT>BOARD_SDRAM

/* DATA section for SRAM_DTC_cm7 */

.data_RAM3 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM3 = .) ;

PROVIDE(__start_data_SRAM_DTC_cm7 = .) ;

*(.ramfunc.$RAM3)

*(.ramfunc.$SRAM_DTC_cm7)

*(.data.$RAM3)

*(.data.$SRAM_DTC_cm7)

*(.data.$RAM3.*)

*(.data.$SRAM_DTC_cm7.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM3 = .) ;

PROVIDE(__end_data_SRAM_DTC_cm7 = .) ;

} > SRAM_DTC_cm7 AT>BOARD_SDRAM

/* DATA section for SRAM_ITC_cm7 */

.data_RAM4 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM4 = .) ;

PROVIDE(__start_data_SRAM_ITC_cm7 = .) ;

*(.ramfunc.$RAM4)

*(.ramfunc.$SRAM_ITC_cm7)

*(.data.$RAM4)

*(.data.$SRAM_ITC_cm7)

*(.data.$RAM4.*)

*(.data.$SRAM_ITC_cm7.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM4 = .) ;

PROVIDE(__end_data_SRAM_ITC_cm7 = .) ;

} > SRAM_ITC_cm7 AT>BOARD_SDRAM

/* DATA section for SRAM_OC1 */

.data_RAM5 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM5 = .) ;

PROVIDE(__start_data_SRAM_OC1 = .) ;

*(.ramfunc.$RAM5)

*(.ramfunc.$SRAM_OC1)

*(.data.$RAM5)

*(.data.$SRAM_OC1)

*(.data.$RAM5.*)

*(.data.$SRAM_OC1.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM5 = .) ;

PROVIDE(__end_data_SRAM_OC1 = .) ;

} > SRAM_OC1 AT>BOARD_SDRAM

/* DATA section for SRAM_OC2 */

.data_RAM6 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM6 = .) ;

PROVIDE(__start_data_SRAM_OC2 = .) ;

*(.ramfunc.$RAM6)

*(.ramfunc.$SRAM_OC2)

*(.data.$RAM6)

*(.data.$SRAM_OC2)

*(.data.$RAM6.*)

*(.data.$SRAM_OC2.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM6 = .) ;

PROVIDE(__end_data_SRAM_OC2 = .) ;

} > SRAM_OC2 AT>BOARD_SDRAM

/* DATA section for SRAM_OC_ECC1 */

.data_RAM7 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM7 = .) ;

PROVIDE(__start_data_SRAM_OC_ECC1 = .) ;

*(.ramfunc.$RAM7)

*(.ramfunc.$SRAM_OC_ECC1)

*(.data.$RAM7)

*(.data.$SRAM_OC_ECC1)

*(.data.$RAM7.*)

*(.data.$SRAM_OC_ECC1.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM7 = .) ;

PROVIDE(__end_data_SRAM_OC_ECC1 = .) ;

} > SRAM_OC_ECC1 AT>BOARD_SDRAM

/* DATA section for SRAM_OC_ECC2 */

.data_RAM8 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM8 = .) ;

PROVIDE(__start_data_SRAM_OC_ECC2 = .) ;

*(.ramfunc.$RAM8)

*(.ramfunc.$SRAM_OC_ECC2)

*(.data.$RAM8)

*(.data.$SRAM_OC_ECC2)

*(.data.$RAM8.*)

*(.data.$SRAM_OC_ECC2.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM8 = .) ;

PROVIDE(__end_data_SRAM_OC_ECC2 = .) ;

} > SRAM_OC_ECC2 AT>BOARD_SDRAM

/* DATA section for SRAM_OC_cm7 */

.data_RAM9 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM9 = .) ;

PROVIDE(__start_data_SRAM_OC_cm7 = .) ;

*(.ramfunc.$RAM9)

*(.ramfunc.$SRAM_OC_cm7)

*(.data.$RAM9)

*(.data.$SRAM_OC_cm7)

*(.data.$RAM9.*)

*(.data.$SRAM_OC_cm7.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM9 = .) ;

PROVIDE(__end_data_SRAM_OC_cm7 = .) ;

} > SRAM_OC_cm7 AT>BOARD_SDRAM

/* MAIN DATA SECTION */

.uninit_RESERVED (NOLOAD) : ALIGN(4)

{

_start_uninit_RESERVED = .;

KEEP(*(.bss.$RESERVED*))

. = ALIGN(4) ;

_end_uninit_RESERVED = .;

} > BOARD_SDRAM AT> BOARD_SDRAM

/* Main DATA section (BOARD_SDRAM) */

.data : ALIGN(4)

{

FILL(0xff)

_data = . ;

PROVIDE(__start_data_RAM = .) ;

PROVIDE(__start_data_BOARD_SDRAM = .) ;

*(vtable)

*(.ramfunc*)

KEEP(*(CodeQuickAccess))

KEEP(*(DataQuickAccess))

*(RamFunction)

*(.data*)

. = ALIGN(4) ;

_edata = . ;

PROVIDE(__end_data_RAM = .) ;

PROVIDE(__end_data_BOARD_SDRAM = .) ;

} > BOARD_SDRAM AT>BOARD_SDRAM

/* BSS section for NCACHE_REGION */

.bss_RAM2 : ALIGN(4)

{

PROVIDE(__start_bss_RAM2 = .) ;

PROVIDE(__start_bss_NCACHE_REGION = .) ;

*(.bss.$RAM2)

*(.bss.$NCACHE_REGION)

*(.bss.$RAM2.*)

*(.bss.$NCACHE_REGION.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM2 = .) ;

PROVIDE(__end_bss_NCACHE_REGION = .) ;

} > NCACHE_REGION AT> NCACHE_REGION

/* BSS section for SRAM_DTC_cm7 */

.bss_RAM3 : ALIGN(4)

{

PROVIDE(__start_bss_RAM3 = .) ;

PROVIDE(__start_bss_SRAM_DTC_cm7 = .) ;

*(.bss.$RAM3)

*(.bss.$SRAM_DTC_cm7)

*(.bss.$RAM3.*)

*(.bss.$SRAM_DTC_cm7.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM3 = .) ;

PROVIDE(__end_bss_SRAM_DTC_cm7 = .) ;

} > SRAM_DTC_cm7 AT> SRAM_DTC_cm7

/* BSS section for SRAM_ITC_cm7 */

.bss_RAM4 : ALIGN(4)

{

PROVIDE(__start_bss_RAM4 = .) ;

PROVIDE(__start_bss_SRAM_ITC_cm7 = .) ;

*(.bss.$RAM4)

*(.bss.$SRAM_ITC_cm7)

*(.bss.$RAM4.*)

*(.bss.$SRAM_ITC_cm7.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM4 = .) ;

PROVIDE(__end_bss_SRAM_ITC_cm7 = .) ;

} > SRAM_ITC_cm7 AT> SRAM_ITC_cm7

/* BSS section for SRAM_OC1 */

.bss_RAM5 : ALIGN(4)

{

PROVIDE(__start_bss_RAM5 = .) ;

PROVIDE(__start_bss_SRAM_OC1 = .) ;

*(.bss.$RAM5)

*(.bss.$SRAM_OC1)

*(.bss.$RAM5.*)

*(.bss.$SRAM_OC1.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM5 = .) ;

PROVIDE(__end_bss_SRAM_OC1 = .) ;

} > SRAM_OC1 AT> SRAM_OC1

/* BSS section for SRAM_OC2 */

.bss_RAM6 : ALIGN(4)

{

PROVIDE(__start_bss_RAM6 = .) ;

PROVIDE(__start_bss_SRAM_OC2 = .) ;

*(.bss.$RAM6)

*(.bss.$SRAM_OC2)

*(.bss.$RAM6.*)

*(.bss.$SRAM_OC2.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM6 = .) ;

PROVIDE(__end_bss_SRAM_OC2 = .) ;

} > SRAM_OC2 AT> SRAM_OC2

/* BSS section for SRAM_OC_ECC1 */

.bss_RAM7 : ALIGN(4)

{

PROVIDE(__start_bss_RAM7 = .) ;

PROVIDE(__start_bss_SRAM_OC_ECC1 = .) ;

*(.bss.$RAM7)

*(.bss.$SRAM_OC_ECC1)

*(.bss.$RAM7.*)

*(.bss.$SRAM_OC_ECC1.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM7 = .) ;

PROVIDE(__end_bss_SRAM_OC_ECC1 = .) ;

} > SRAM_OC_ECC1 AT> SRAM_OC_ECC1

/* BSS section for SRAM_OC_ECC2 */

.bss_RAM8 : ALIGN(4)

{

PROVIDE(__start_bss_RAM8 = .) ;

PROVIDE(__start_bss_SRAM_OC_ECC2 = .) ;

*(.bss.$RAM8)

*(.bss.$SRAM_OC_ECC2)

*(.bss.$RAM8.*)

*(.bss.$SRAM_OC_ECC2.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM8 = .) ;

PROVIDE(__end_bss_SRAM_OC_ECC2 = .) ;

} > SRAM_OC_ECC2 AT> SRAM_OC_ECC2

/* BSS section for SRAM_OC_cm7 */

.bss_RAM9 : ALIGN(4)

{

PROVIDE(__start_bss_RAM9 = .) ;

PROVIDE(__start_bss_SRAM_OC_cm7 = .) ;

*(.bss.$RAM9)

*(.bss.$SRAM_OC_cm7)

*(.bss.$RAM9.*)

*(.bss.$SRAM_OC_cm7.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM9 = .) ;

PROVIDE(__end_bss_SRAM_OC_cm7 = .) ;

} > SRAM_OC_cm7 AT> SRAM_OC_cm7

/* MAIN BSS SECTION */

.bss : ALIGN(4)

{

_bss = .;

PROVIDE(__start_bss_RAM = .) ;

PROVIDE(__start_bss_BOARD_SDRAM = .) ;

*(.bss*)

*(COMMON)

. = ALIGN(4) ;

_ebss = .;

PROVIDE(__end_bss_RAM = .) ;

PROVIDE(__end_bss_BOARD_SDRAM = .) ;

PROVIDE(end = .);

} > BOARD_SDRAM AT> BOARD_SDRAM

/* NOINIT section for NCACHE_REGION */

.noinit_RAM2 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM2 = .) ;

PROVIDE(__start_noinit_NCACHE_REGION = .) ;

*(.noinit.$RAM2)

*(.noinit.$NCACHE_REGION)

*(.noinit.$RAM2.*)

*(.noinit.$NCACHE_REGION.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM2 = .) ;

PROVIDE(__end_noinit_NCACHE_REGION = .) ;

} > NCACHE_REGION AT> NCACHE_REGION

/* NOINIT section for SRAM_DTC_cm7 */

.noinit_RAM3 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM3 = .) ;

PROVIDE(__start_noinit_SRAM_DTC_cm7 = .) ;

*(.noinit.$RAM3)

*(.noinit.$SRAM_DTC_cm7)

*(.noinit.$RAM3.*)

*(.noinit.$SRAM_DTC_cm7.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM3 = .) ;

PROVIDE(__end_noinit_SRAM_DTC_cm7 = .) ;

} > SRAM_DTC_cm7 AT> SRAM_DTC_cm7

/* NOINIT section for SRAM_ITC_cm7 */

.noinit_RAM4 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM4 = .) ;

PROVIDE(__start_noinit_SRAM_ITC_cm7 = .) ;

*(.noinit.$RAM4)

*(.noinit.$SRAM_ITC_cm7)

*(.noinit.$RAM4.*)

*(.noinit.$SRAM_ITC_cm7.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM4 = .) ;

PROVIDE(__end_noinit_SRAM_ITC_cm7 = .) ;

} > SRAM_ITC_cm7 AT> SRAM_ITC_cm7

/* NOINIT section for SRAM_OC1 */

.noinit_RAM5 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM5 = .) ;

PROVIDE(__start_noinit_SRAM_OC1 = .) ;

*(.noinit.$RAM5)

*(.noinit.$SRAM_OC1)

*(.noinit.$RAM5.*)

*(.noinit.$SRAM_OC1.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM5 = .) ;

PROVIDE(__end_noinit_SRAM_OC1 = .) ;

} > SRAM_OC1 AT> SRAM_OC1

/* NOINIT section for SRAM_OC2 */

.noinit_RAM6 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM6 = .) ;

PROVIDE(__start_noinit_SRAM_OC2 = .) ;

*(.noinit.$RAM6)

*(.noinit.$SRAM_OC2)

*(.noinit.$RAM6.*)

*(.noinit.$SRAM_OC2.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM6 = .) ;

PROVIDE(__end_noinit_SRAM_OC2 = .) ;

} > SRAM_OC2 AT> SRAM_OC2

/* NOINIT section for SRAM_OC_ECC1 */

.noinit_RAM7 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM7 = .) ;

PROVIDE(__start_noinit_SRAM_OC_ECC1 = .) ;

*(.noinit.$RAM7)

*(.noinit.$SRAM_OC_ECC1)

*(.noinit.$RAM7.*)

*(.noinit.$SRAM_OC_ECC1.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM7 = .) ;

PROVIDE(__end_noinit_SRAM_OC_ECC1 = .) ;

} > SRAM_OC_ECC1 AT> SRAM_OC_ECC1

/* NOINIT section for SRAM_OC_ECC2 */

.noinit_RAM8 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM8 = .) ;

PROVIDE(__start_noinit_SRAM_OC_ECC2 = .) ;

*(.noinit.$RAM8)

*(.noinit.$SRAM_OC_ECC2)

*(.noinit.$RAM8.*)

*(.noinit.$SRAM_OC_ECC2.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM8 = .) ;

PROVIDE(__end_noinit_SRAM_OC_ECC2 = .) ;

} > SRAM_OC_ECC2 AT> SRAM_OC_ECC2

/* NOINIT section for SRAM_OC_cm7 */

.noinit_RAM9 (NOLOAD) : ALIGN(4)

{

PROVIDE(__start_noinit_RAM9 = .) ;

PROVIDE(__start_noinit_SRAM_OC_cm7 = .) ;

*(.noinit.$RAM9)

*(.noinit.$SRAM_OC_cm7)

*(.noinit.$RAM9.*)

*(.noinit.$SRAM_OC_cm7.*)

. = ALIGN(4) ;

PROVIDE(__end_noinit_RAM9 = .) ;

PROVIDE(__end_noinit_SRAM_OC_cm7 = .) ;

} > SRAM_OC_cm7 AT> SRAM_OC_cm7

/* DEFAULT NOINIT SECTION */

.noinit (NOLOAD): ALIGN(4)

{

_noinit = .;

PROVIDE(__start_noinit_RAM = .) ;

PROVIDE(__start_noinit_BOARD_SDRAM = .) ;

*(.noinit*)

. = ALIGN(4) ;

_end_noinit = .;

PROVIDE(__end_noinit_RAM = .) ;

PROVIDE(__end_noinit_BOARD_SDRAM = .) ;

} > BOARD_SDRAM AT> BOARD_SDRAM

/*

* for exception handling/unwind - some Newlib functions (in common

* with C++ and STDC++) use this.

*/

.ARM.extab : ALIGN(4)

{

*(.ARM.extab* .gnu.linkonce.armextab.*)

} > BOARD_SDRAM

.ARM.exidx : ALIGN(4)

{

__exidx_start = .;

*(.ARM.exidx* .gnu.linkonce.armexidx.*)

__exidx_end = .;

} > BOARD_SDRAM

/* Reserve and place Heap within memory map */

_HeapSize = 0x1000;

.heap : ALIGN(4)

{

_pvHeapStart = .;

. += _HeapSize;

. = ALIGN(4);

_pvHeapLimit = .;

} > BOARD_SDRAM

_StackSize = 0x1000;

/* Reserve space in memory for Stack */

.heap2stackfill :

{

. += _StackSize;

} > BOARD_SDRAM

/* Locate actual Stack in memory map */

.stack ORIGIN(BOARD_SDRAM) + LENGTH(BOARD_SDRAM) - _StackSize - 0: ALIGN(4)

{

_vStackBase = .;

. = ALIGN(4);

_vStackTop = . + _StackSize;

} > BOARD_SDRAM

/* Provide basic symbols giving location and size of main text

* block, including initial values of RW data sections. Note that

* these will need extending to give a complete picture with

* complex images (e.g multiple Flash banks).

*/

_image_start = LOADADDR(.text);

_image_end = LOADADDR(.data) + SIZEOF(.data);

_image_size = _image_end - _image_start;

/* Provide symbols for MIMXRT1170 parts for boot header generation code

* to set image to be plain load image or XIP.

* Config : Plain load image = false

*/

_boot_loadaddr = ORIGIN(BOARD_SDRAM);

_boot_size = LENGTH(BOARD_SDRAM);

}

I hope these details will be helpful you to understand the problem.

____________________________________________________________________

Also can you please share me the evkmimxrt1170_lwip_dhcp_usb_freertos example project which uses XIP(BOARD_FLASH)+SDRAM. I want to merge my code to this project which requires more memory.

In SDK examples: evkmimxrt1170_lwip_dhcp_usb_freertos uses,

SRAM_DTC_cm7 is not enough to merge my code into it. If I tried to add my code to the it is overflowing.

Thanks in advance.

Hi Edwin,

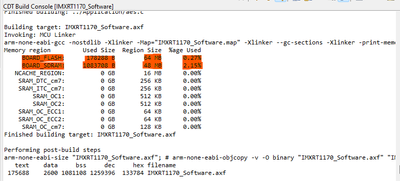

I found this SDK example evkmimxrt1170_lwip_ping_freertos_cm7 which uses the memory of BOARD_FLASH+SDRAM. After build,

And I am able to debug this on EVK, will be getting some output.

But when I try to merge the example code code of with lwip_dhcp_usb_freertos driver files and build it I am able to build it successfully by configuring the lwipopts.h file.

The build memory use is as below,

here NCACHE_REGION is also used. SDRAM is not utilized.

When debug this, I encountered with the same error again here,

It is not working this way, Can you tell me how to debug this issue? what causes this error?

Thanks in advance.

Hi @Naveed,

I understand, have you looked into the following community article describing the usage of SDRAM as storage for code? https://community.nxp.com/t5/i-MX-RT-Knowledge-Base/I-MX-RT-How-to-booting-to-SDRAM/ta-p/1125054

I believe it will prove very useful for your inquiry.

Hi Edwin,

Thanks for your reply.

I have followed the steps given in the shared link. I am getting this errors after adding the script to .ld file and building the code.

Error:

Please let me know how to resolve these errors.

Thanks in advance.