- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- Identification and Security

- i.MX Processors

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- CodeWarrior

- Wireless Connectivity

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: IMXRT1050 Flex IO MCU LCD 8080, WR resting low

IMXRT1050 Flex IO MCU LCD 8080, WR resting low

IMXRT1050 Flex IO MCU LCD 8080, WR resting low

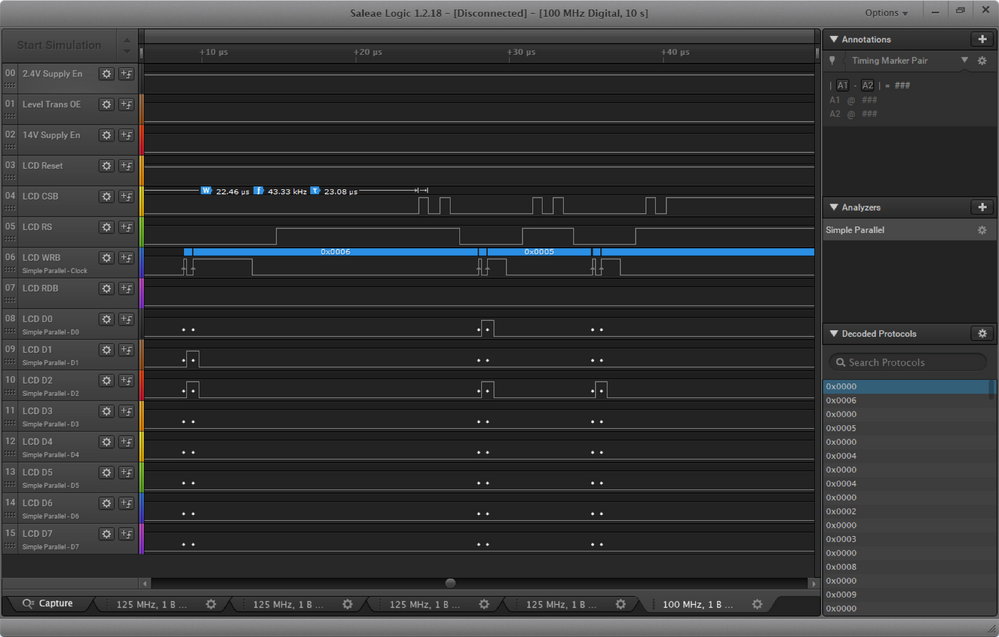

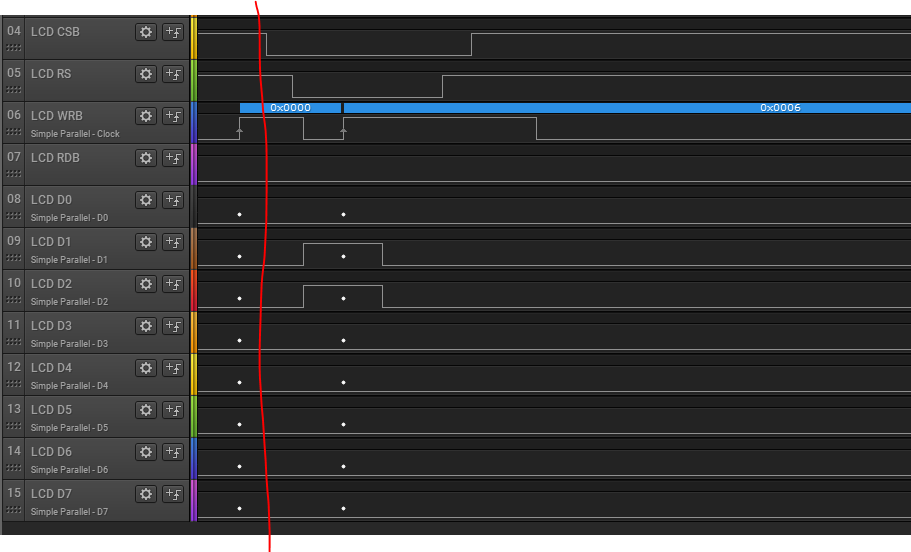

I'm trying to get an 8080 MCU LCD working on the FlexIO interface on an IMXRT1050. It looks like data is clocking out correctly for the most part however I'm having trouble with the WR and RD pins. They are resting low, then rising just before clocking out data. So I'm getting extra zeros in my data stream. Any ideas?

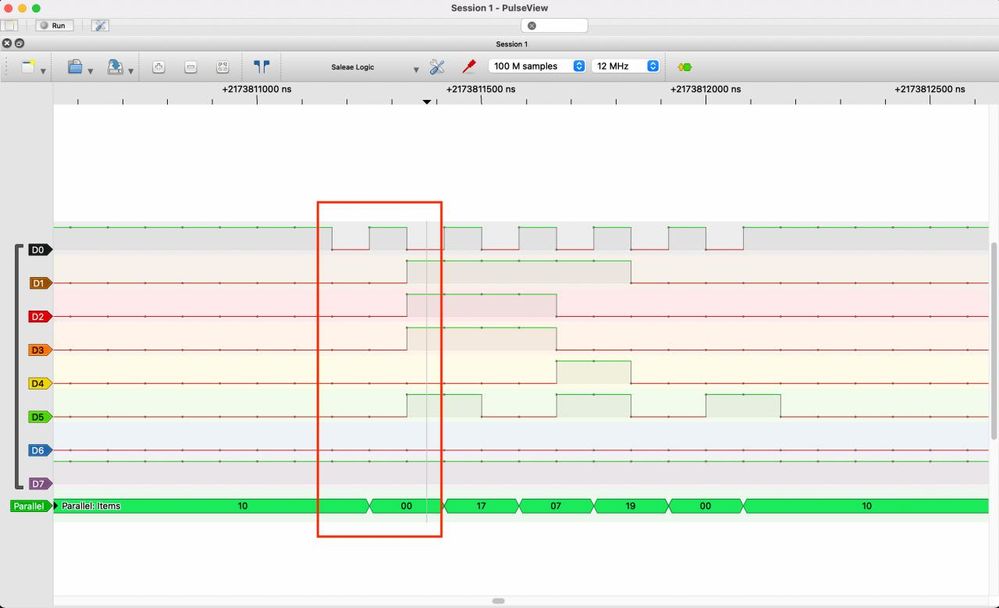

I seem to be facing the exact same issue on a Teensy Micromod using an RT1062 - this is an Arduino friendly rt1062 by PJRC/SparkFun.

Although I am not using the official NXP demo code, I have based the configuration of the FlexIO module, shifter and timer in an identical manner to the HX8357 NXP example for the KL28/RT1050 (AN5313/AN12822), and I am also getting an early pulse on the WR as soon as the shifter is loaded on a single beat transmit

My code looks like so:

Shifter/timer setup:

void singleBeatWrite(uint8_t const * buffer, uint32_t const length){

p->CTRL &= ~FLEXIO_CTRL_FLEXEN;

//p->CTRL |= FLEXIO_CTRL_SWRST; //Software reset FlexIO registers enable

//p->CTRL &= ~FLEXIO_CTRL_SWRST; //Software reset FlexIO registers disable

/* Configure the shifters */

p->SHIFTCFG[0] =

FLEXIO_SHIFTCFG_INSRC /* Shifter input */

| FLEXIO_SHIFTCFG_SSTOP(0U) /* Shifter stop bit disabled */

| FLEXIO_SHIFTCFG_SSTART(0U) /* Shifter start bit disabled and loading data on enabled */

| FLEXIO_SHIFTCFG_PWIDTH(8U-1U); /* Bus width */

p->SHIFTCTL[0] =

FLEXIO_SHIFTCTL_TIMSEL(0U) /* Shifter's assigned timer index */

| (0<<23) //FLEXIO_SHIFTCTL_TIMPOL(0U) /* Shift on posedge of shift clock */

| FLEXIO_SHIFTCTL_PINCFG(3U) /* Shifter's pin configured as output */

| FLEXIO_SHIFTCTL_PINSEL(4U) /* Shifter's pin start index */

| (0<<7) //((uint32_t)(1<<7)) /* Shifter's pin active high */

| FLEXIO_SHIFTCTL_SMOD(2U); /* Shifter mode as transmit */

/* Configure the timer for shift clock */

p->TIMCMP[0] =

((1U * 2U - 1) <<

I then call this function from my main loop ever 500ms by calling singleBeatWrite and passing the data

uint8_t bufferData[4] = {0x17, 0x07, 0x19, 0x90};

...

singleBeatWrite(bufferData,4);

Hi Luke,

This looks like a very custom approach. It will totally depend on your FlexIO configuration. I highly recommend you to check the below community document. Even though the document is for KL43 devices, the FlexIO modules works the same in RT devices.

https://community.nxp.com/docs/DOC-105640

Hope it helps!

Best regards,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

So what is causing my issue is that the value on my RW pin is changing when FLEXIO_MCULCD_SetSingleBeatWriteConfig(base) is called and then dropping again when FLEXIO_MCULCD_ClearSingleBeatWriteConfig(base) is called.

One option I've tried is to refactor FLEXIO_MCULCD_WriteCommandBlocking to set the config first, the pin rises, then call FLEXIO_MCULCD_StartTransfer(base) so my CS pin gets set. Then do the opposite at the end of the function. This way my lcd driver should ignore those extra transitions on the WR line.

I would also need to do similar refactoring for the other read/write functions.

Although I should mention that I am measuring these signals straight out of the MCU and one of my coworkers mentioned that the LCD Driver may hold these lines up anyway and this whole issue will be moot.

Hi Luke,

There is some material that I can recommend you to take as reference. You can find driver and demo project in the SDK package of a board supports the demo, such as FRDM-K28F. Unfortunately, we do not have this example for RT1050 devices but you can take it as reference.

In addition, I suggest you to check this application note that explains how to use the FlexIO module to emulate 8080 bus interface. Also this link mentions the typical usage of FlexIO LCD APIs.

I hope this information helps you.

Best regards,

Felipe