- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- ARM Microcontrollers

- :

- Kinetisマイクロコントローラ・ナレッジ・ベース

- :

- Understanding FlexIO

Understanding FlexIO

- RSS フィードを購読する

- 新着としてマーク

- 既読としてマーク

- ブックマーク

- 購読

- 印刷用ページ

- 不適切なコンテンツを報告

Understanding FlexIO

Understanding FlexIO

The FlexIO module was first introduced in the Freescale Kinetis KL43 family. It is capable of emulating various serial communication protocols including: UART, SPI and I2C. The FlexIO module is very flexible and you can configure it according to your communication needs. The main components of the FlexIO module are the shifters, timers, and pins. Data is loaded onto a shifter and a timer is assigned to generate the shifter clock and use a pin to output the data from the shifter.

The KL43 FlexIO module has 4 32-bit shifters, 4 16-bit timers and 8 bidirectional I/O pins. Each shifter and timer has its own configuration registers. The most important registers that configure the whole FlexIO behavior are the SHIFTCFG, SHIFTCTL, TIMCFG, TIMCTL and TIMCMP registers. There are other registers that contain status flags, interrupt enabling bits and the buffers for the shifters.

Shifters have a timer assigned to them to generate the shift clock and it can be configured to shift data in or out. When the shifter is configured to transmit mode, the data from the SHIFTBUF register will be loaded to the shifter and the shifter status flag will be set meaning that the shifter is ready to start the transmission. In receive mode, the shifter status flag is set when SHIFTBUF has been loaded with the data from the shifter, and the status flag is cleared when the SHITBUF register is read.

The timers are highly configurable, they can use external or internal triggers to generate certain conditions to reset, enable and disable the timer. The triggers can be a timer output, shifter status flag, pin input or an external trigger input. They can be configured to enable in response to a trigger, pin or shifter condition.

Each shifter or timer can be configured to use any FlexIO pin with either polarity. The pins can be used as an input or output. A pin configured as an input for a timer can be used to receive a clock and use it as the shifter clock that is assigned to this timer.

Once everything is configured you need to read/write the shifter buffers and the shifter and timer status flags to start a transmission or to read the contents of the shifter buffer when receiving data.

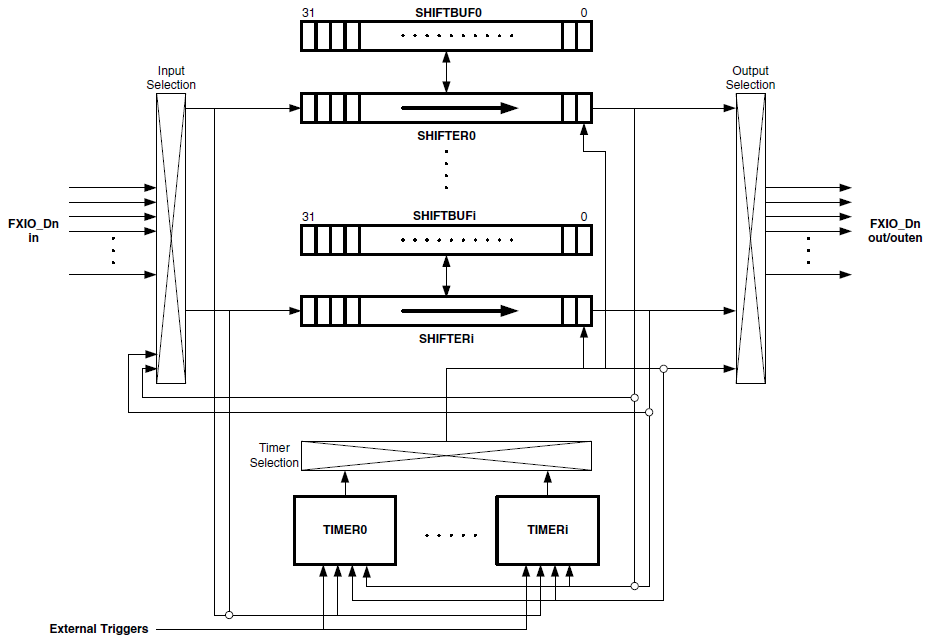

The following diagram gives a high-level overview of the configuration of FlexIO timers and shifters.

Figure 1. FlexIO block diagram

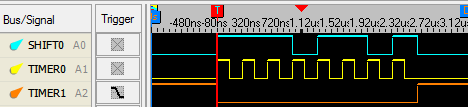

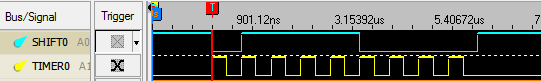

In the following example configuration, the FlexIO module will be configured as a transmitter. It will use one shifter, two timers, and three pins. The pins will be used for the outputs of the shifter and the two timers. One timer will be used as the shifter clock and the other timer will be used as a chip select to show when a transmission is being made. The FlexIO will be configured to have a baud rate of FlexIO clock/4 and will do an 8-bit transmission.

Figure 2. Example transmission

Timer 0

Timer Configuration 0 Register (FLEXIO_TIMCFG0) = 0x00002200

TIMOUT = 0 Timer output is logic one when enabled and is not affected by timer reset.

TIMDEC = 0 Decrement counter on FlexIO clock, Shift clock equals Timer output.

TIMRST = 0 Timer never reset.

TIMDIS = 2 Timer disabled on Timer compare.

TIMENA = 2 Timer enabled on Trigger high.

TSTOP = 0 Stop bit is disabled.

TSTART = 0 Start bit disabled.

Timer Control 0 Register (FLEXIO_TIMCTL0) = 0x01C30101

TRGSEL = 1 Trigger select. Shifter 0 status flag.

TRGPOL = 1 Trigger active low.

TRGSRC = 1 Internal trigger selected.

PINCFG = 3 Timer pin output.

PINSEL = 1 Timer pin 1 select.

PINPOL = 0 Pin is active high.

TIMOD = 1 Dual 8-bit counters baud/bit mode.

Timer Compare 0 Register (FLEXIO_TIMCMP0) = 0x00000F01

TIMCMP = 0x00000F01

Configure 8-bit transfer with a baud rate of FlexIO clock/4. Set TIMCMP[15:8] = (number of bits x 2) - 1. Set TIMCMP[7:0] = (baud rate divider / 2) - 1.

In our case we want an 8-bit transfer so TIMCMP[15:8] = 0xF and a baud rate divider of 4 so TIMCMP[7:0] = 0x1.

Timer 1

Timer Configuration 1 Register (FLEXIO_TIMCFG1) = 0x00001100

TIMOUT = 0 Timer output is logic one when enabled and is not affected by timer reset.

TIMDEC = 0 Decrement counter on FlexIO clock, Shift clock equals Timer output.

TIMRST = 0 Timer never reset.

TIMDIS = 1 Timer disabled on Timer N-1 disable.

TIMENA = 1 Timer enabled on Timer N-1 enable.

TSTOP = 0 Stop bit is disabled.

TSTART = 0 Start bit disabled.

Timer Control 1 Register (FLEXIO_TIMCTL1) = 0x00030283

TRGSEL = 0 Trigger select. Doesn’t matter because we won’t use a trigger.

TRGPOL = 0 Trigger active high.

TRGSRC = 0 External trigger selected.

PINCFG = 3 Timer pin output.

PINSEL = 2 Timer pin 2 select.

PINPOL = 1 Pin is active low.

TIMOD = 3 Single 16-bit counter mode.

Timer Compare 1 Register (FLEXIO_TIMCMP1) = 0x0000FFFF

TIMCMP = 0x0000FFFF Never compare.

Shifter 0

Shifter Control 0 Register (FLEXIO_SHIFTCTL0)

TIMSEL = 0 Timer 0 select.

TIMPOL = 0 Shift on posedge of Shift clock.

PINCFG = 3 Shifter pin output.

PINSEL = 0 Shifter pin 0 select.

PINPOL = 0 Pin is active high.

SMOD = 2 Transmit mode. Load SHIFTBUF contents into the Shifter on expiration of the Timer.

Shifter Configuration 0 Register (FLEXIO_SHIFTCFG0)

INSRC = 0 The input source of the shifter is from a pin. In our cause this doesn’t matter because our shifter is set as transmit mode.

SSTOP = 0 Stop bit disabled.

SSTART = 0 Start bit disabled.

Once all the FlexIO components are configured you have to enable the FlexIO instance by setting the FLEXEN bit in the FLEX_CTRL register. Initially, the shifter status flag is set and is cleared each time the SHIFTBUF register is written. This flag is set each time the SHIFTBUF data has been transferred to the Shifter (SHIFTBUF is empty). The shifter status flag 0 is configured to be the trigger of the timer 0, so as soon as the status flag is cleared, the timer 0 will be enabled because TIMENA = 2 (Timer enabled on Trigger high)and TRGPOL = 1 (Trigger active low). The shifter will begin to shift out the data on the positive edge of the clock (TIMPOL = 0) until the timer is disabled. The timer will disable when the timer counter reaches 0 (TIMDIS = 2).

The timer 1 is configured to be active (low) when the timer 0 is enabled. This is because TIMDIS = 1 and TIMENA = 1. The compare register is configured to 16-bit counter and set to 0xFFFF. With this value the timer will never compare and always be active when the timer is enabled.

To send data, you have to make sure that the previous transaction was completed and you can check this by reading the TIMSTAT flag. This flag sets each time the timer counter reaches 0. Once the TIMSTAT flag is set, you clear it and write your new data to the SHITBUF register to start the transaction.

The KSDK 1.2.0 has drivers and a HAL to facilitate the configuration of the FlexIO module. Some of the important functions are:

FLEXIO_DRV_Init(uint32_t instance, const flexio_user_config_t *userConfigPtr);

Use this function to initialize the FlexIO module before using it. In this configuration you can change the settings in the FLEXIO_CTRL register such as: Doze Enable, Debug Enable, Fast Access and software reset.

FLEXIO_HAL_ConfigureTimer(FLEXIO_Type * base, uint32_t timerIdx, const flexio_timer_config_t *timerConfigPtr);

Use this function to configure a timer in the FlexIO. This function uses a configuration structure that can change the TIMCFG, TIMCTL and TIMCPM registers.

FLEXIO_HAL_ConfigureShifter(FLEXIO_Type * base, uint32_t shifterIdx, const flexio_shifter_config_t *shifterConfigPtr);

Use this function to configure a shifter in the FlexIO. This function uses a configuration structure that can change the SHIFTCFG and SHIFTCTL registers.

FLEXIO_HAL_SetShifterBuffer(FLEXIO_Type * base, uint32_t shifterIdx, uint32_t value);

Use this function to start a transmission. When writing to the SHIFTBUF register, the Shifter Status Flag is cleared.

FLEXIO_DRV_Start(uint32_t instance);

Use this function to enable the FlexIO module by setting the FLEXEN bit in the FLEX_CTRL register.

FLEXIO_HAL_GetTimerStatusFlags(FLEXIO_Type * base);

This function returns the contents of the TIMSTAT register. You can use this function to check when a transmission is finished.

FLEXIO_HAL_ClearTimerStatusFlags(FLEXIO_Type * base, uint32_t mask);

This function clears a specific Timer Status Flag. You can use this function to clear a flag after you read that the flag was set.

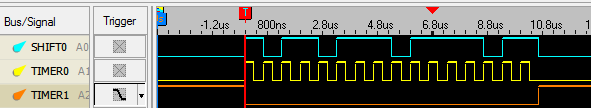

To change the frequency of the transmission you have to change the value of the TIMCMP register. In dual 8-bit counters baud/bit mode, the lower 8-bits configures the baud rate divider equal to (CMP[7:0] + 1) * 2 and the upper 8-bits configure the number of bits in each word equal to (CMP[15:8] + 1) / 2.

In our example the baud rate divider is set to 4, this means CMP[7:0] has the value 1. The number of bits transmitted is set to 8, this means CMP[15:8] has the value 0xF.

Let’s change the baud rate divider to 32. To obtain the CMP[7:0] value, we will have to solve the simple equation:

32 = (CMP[7:0]+1)*2

CMP[7:0] = 15=0xF

Now let’s change the number of bits to 16. The CMP[15:8] value is defined by:

16 = ((CMP[15:8]+1))/2

CMP[15:8] = 31=0x1F

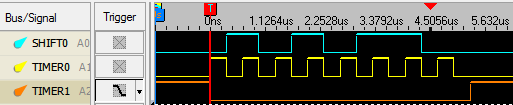

The value for the TIMCMP for the timer 0 has to be 0x00001F0F to get a baud rate divider of 32 and a word length of 16 bits. The waveform will look as follows.

Figure 3. 16-bit transmission

By default the shifter in the FlexIO transmits the LSB first. To change the transmission order, you have to write to the SHIFTBUFBIS (Bit swapped) register instead of the SHIFTBUF register. There are also other buffer registers: SHIFTBUFBYS and SHIFTBUFBBS. The first register swaps the bytes and the second register swaps the bytes and bits at the same time. When using one of these registers you have to be careful to consider that the length of the SHIFTBUF registers is of 32 bits, so if you choose to use the SHIFTBUFBIS for a transmission and your transmission length is not of 32 bits, you have to start writing your data starting from the most significant bit.

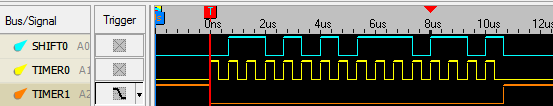

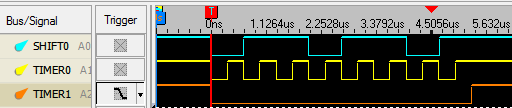

The following image shows a MSB transmission. The value 0x6AED0000 was written to the SHIFTBUFBIS register.

Figure 4. MSB 16-bit transmission

The FlexIO module supports automatic start and stop bit handling. All you have to do is change the SHIFTCFG and the TIMCFG configuration bits. In the SHIFTCFG register set SSTOP to 11 if you want the stop bit to have the value 1, and set the SSTART to 10 if you want the stop bit to have the value 0. In the TIMCFG register set the TSART to 1 and the TSOP to 10.

The transmission will look as the following image. Data transmitted 0x0F.

Figure 5. Transmission with start and stop bit

Changing the phase of the clock is very easy, you just have to set the TIMPOL bit to 1 in the SHIFTCTL register.

Figure 6. Shift on negedge of Shift clock

The conditions to disable and enable the timers can be configured by changing the TIMENA and TIMDIS values in the TIMCFG register. In our example the timer is enabled by the trigger high. The trigger can be set to be an external pin, a shifter status flag, or a timer output. In our case the trigger was set to the shifter status flag, but you can change this configuration to your communication needs. The timer can also be enabled when the previous timer is enabled, on a certain pin edge, or with a combination of pins and triggers.

The timer in the example above disables on the timer compare. This means that when the timer counter reaches zero, the timer will disable automatically. The timer counter is loaded with the timer compare value every time it reaches zero or when it is first enabled. The timer can also be disabled by other conditions such as: when the previous timer is disabled, on a trigger falling edge, on a pin edge, or on a combination of these.

Each pin can be configured to be active high or low. When a pin polarity is changed it only affects the output of the pin, for example, if a timer is set to be the shifter clock and you change the pin polarity, the shifter clock will not change its polarity, only the output to the pin from the timer will change.

The configuration for the polarity of the pins is located in the TIMCTL and SHIFTCTL. When the PINPOL value is changed to 1, the pin is active low. In the following image the polarity of the timer pin and the shifter pin was changed to 1, so they are active low.

Figure 7. Timer and Shifter active low

The FlexIO module can generate an interrupt from 3 sources: Shifter error, Shifter status flag and Timer status flag. To enable the interrupts you need to set the bits in the SHIFTSIEN,SHIFTEIEN and TIMIEN.

If you are using KSDK you can enable the interrupt in NVIC by setting true .useInt in the FlexIO user config that the function FLEXIO_DRV_Init utilizes. The default handler for the interruption is named UART2_FLEXIO_IRQHandler.

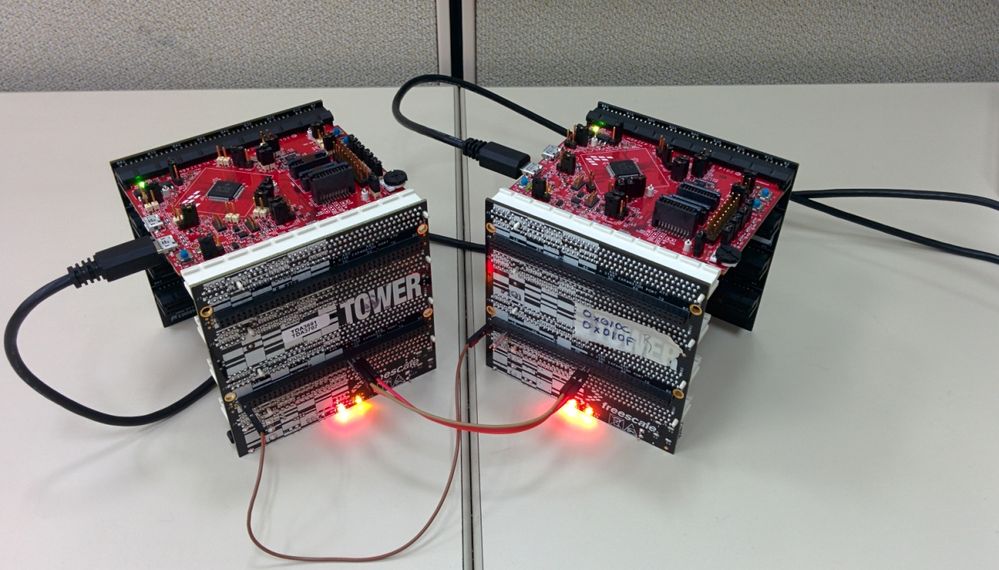

The following example configuration will configure the FlexIO module as a receiver. This configuration works with the first example configuration shown. Both tower boards (TWR-KL43Z48M) have to be connected as shown further below in the Table 1 Hardware connnections. The FlexIO module will use one Shifter, one timer, and three pins. The pins will be used for the input of the shifter, the input clock for the timer and the trigger for the timer. The timer will use pin 1 as an input and its output will be the same as the input clock. The trigger for the timer will be the transmitter chip select pin and it will be used to enable or disable the timer. The FlexIO will be configured to do an 8-bit transmission.

Shifter 0

Shifter Control 0 Register (FLEXIO_SHIFTCTL0) = 0x00800001

TIMSEL = 0 Timer 0 select.

TIMPOL = 1 Shift on negedge of Shift clock.

PINCFG = 0 Shifter pin output disabled.

PINSEL = 0 Shifter pin 0 select.

PINPOL = 0 Pin is active high.

SMOD = 1 Receive mode. Captures the current Shifter content into the SHIFTBUF on expiration of the Timer.

Shifter Configuration 0 Register (FLEXIO_SHIFTCFG0) = 0x00000000

INSRC = 0 The input source of the shifter is from a pin. In our cause this doesn’t matter because our shifter is set as transmit mode.

SSTOP = 0 Stop bit disabled.

SSTART = 0 Start bit disabled.

Timer 0

Timer Configuration 0 Register (FLEXIO_TIMCFG0) = 0x01206602

TIMOUT = 1 Timer output is logic zero when enabled and is not affected by timer reset.

TIMDEC = 2 Decrement counter on Pin input (both edges), Shift clock equals Pin input.

TIMRST = 0 Timer never reset.

TIMDIS = 6 Timer disabled on Trigger rising edge.

TIMENA = 6 Timer enabled on Trigger falling edge.

TSTOP = 0 Stop bit is disabled.

TSTART = 1 Start bit enabled.

Timer Control 0 Register (FLEXIO_TIMCTL0) = 0x04C00103

TRGSEL = 4 Trigger select. Pin 2 input.

TRGPOL = 1 Trigger active low.

TRGSRC = 1 Internal trigger selected.

PINCFG = 0 Timer pin output disabled.

PINSEL = 1 Timer pin 1 select.

PINPOL = 0 Pin is active high.

TIMOD = 3 Single 16-bit counter mode.

Timer Compare 0 Register (FLEXIO_TIMCMP0) = 0x0000000F

TIMCMP = 0x0000000F Configure 8-bit transfer. Set TIMCMP = (number of bits x 2) - 1.

The shifter status flag is set every time the SHIFTBUF register has been loaded with data from the shifter. This occurs every time that the transmitter sends 8 bits of data. You can read the shifter status flag by polling or by enabling an interrupt based on your needs. This flag clears automatically when you read the SHITBUF register.

During the transmission, the first thing that happens is that timer from the receiver will be enabled because the chip select signal from the transmitter is configured as a trigger. Once the timer is enabled, the timer will begin to decrement on the pin input, this means that the shifter clock of the receiver will be equal to the pin input. The transmitter shifter is configured to shift data out on the positive edge of the clock and the receiver shifter is configured to shift data in on the negative edge of the clock. After 8 bits have been transmitted, the compare register from the receiver will reach 0 and this generates an event to store the data from the shifter to the SHITBUF register and the Shifter Status Flag will be set. Finally the timer will be disabled by the chip select signal and keep waiting for another transaction.

The hardware connections are shown in the following table.

Signal name | TWR-KL43Z48M transmitter | TWR-KL43Z48M receiver | ||

Pin name | Board Location | Pin name | Board Location | |

Serial Data | PTD0/FXIO0_D0 | B46 | PTD0/FXIO0_D0 | B46 |

Clock | PTD1/FXIO0_D1 | B48 | PTD1/FXIO0_D1 | B48 |

Chip Select | PTD2/FXIO0_D2 | B45 | PTD2/FXIO0_D2 | B45 |

GND | GND | B2 | GND | B2 |

Table 1. Hardware connections

Figure 8. Hardware connections

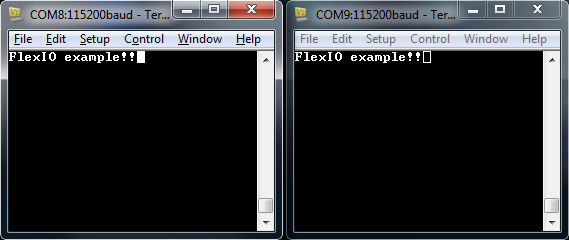

The example projects for the FlexIO transmitter and receiver are developed in KDS 3.0.0 with KSDK 1.2.0. The application lets the user communicate with the transmitter via a serial terminal and the transmitter sends each character to the receiver via FlexIO and the receiver displays the received character on another serial terminal.

To be able to compile the project, first you need to compile the library located in C:\Freescale\KSDK_1.2.0\lib\ksdk_platform_lib\kds\KL43Z4.

Once the two TWR-KL43Z48M are connected as described above, import both projects into KDS, compile the platform library, and both projects. Open two serial terminals configured to 115200 bauds and run each project on a different tower.

On the transmitter terminal you can write anything and it will be displayed and transmitted to the receiver tower via FlexIO and will be shown on the other terminal.

Figure 9. FlexIO example application. Transmitter (left terminal). Receiver (Right terminal).

The FlexIO module is also capable of generating a PWM signal by configuring one of its timers to the Dual 8-bit counters PWM mode. This mode is configured by writing 01 to TIMOD in the TIMCTL register. In this mode, the lower 8-bits of the counter and compare register are used to configure the high period of the timer output and the upper 8-bits are used to configure the low period of the timer output. The shifter bit count is configured using another timer or external signal.

To calculate the frequency of the PWM signal you have to add the lower 8-bits of the counter and the upper 8-bits and divide it by the FlexIO clock*2 (Only if the timer is configured to decrement on the FlexIO clock.)

The frequency of the PWM signal is given by:

f = (FlexIO clock)/(TIMCMP[15:8]+TIMCPM[7:0]+2)

To calculate the TIMCMP values to get a certain frequency you can solve the equation for TIMCMP

TIMCMP[15:8]+TIMCPM[7:0] = (FlexIO clock)/f-2

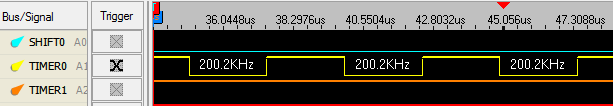

For example, let’s say we want a 200kHz PWM signal, by using the formula above and using the FlexIO clock of 48MHz, we get that the sum of the TIMCMP values must be 238. If we want a 50% duty cycle we need to write the value 238/2 to the lower and upper 8 bits of the TIMCMP register.

The waveform generated by these settings is shown in the figure below.

Figure 10. 200kHz 50% duty cycle PWM signal

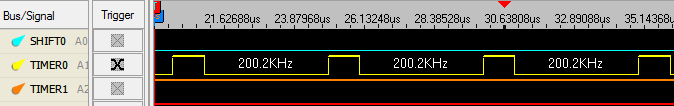

To change the duty cycle you need to change the values of TIMCPM[15:8] and TIMCPM[7:0] but without changing the sum of both values, otherwise the frequency will also be altered. For example, if we need a 20% duty cycle we multiply 0.20*238 and 0.8*238. We round up the results and get TIMCPM[7:0] = 48 and TIMCPM[15:8] = 190. The waveform generated will look as shown in the figure below.

Figure 11. 200kHz 20% duty cycle PWM signal

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

FlexIO register viewing on “EmbSys Register” window

I can’t read FlexIO registers in debugging mode using "EnbSys Register" view.

I’m using KDS 3.2 & KSDK v2 and P&M SDA to evaluate FlexIO on FRDM-KL43Z board.

MCGIRCLK used as Timer source clock to generate PWM.

This clock is divided by two dividers MCG_MC[LIRC_Div2] and MCG_SC[FCRDIV] .

MCG->MC |= MCG_MC_LIRC_DIV2(7); // MCGIRCLK = IRC8M divide by 128

MCG->SC |= MCG_SC_FCRDIV(7) ; // MCGIRCLK = IRC8M divide by 128

Doesn’t matter how you initialize those two registers I have a problem with the initialization value for those two dividers.

128 x 128 combination (for DIV2 and FRCDIV respectively), reading FlexIO registers returns zero.

Only for combinations 128 x 1, 64 x 2 or 64 x 4 reading FlexIO registers is O.K

To summarize, is if there are any limitations or restriction on those clock dividers?

BR

Shaul

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shaul,

I saw that Alice Yang was helping you with this issue on the post https://community.nxp.com/thread/437224 and suggested using JLink debug firmware. Are you still having this problem?

Gerardo

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks

It's O.K with Alice help

Shaul

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Can you, please, add more info about pin behavior in some edge cases for both Shifter driven pins and Timer driven pins.

As far as I understand, PINCFG=0, switch pin into input mode ( no questions here ),

For PINCFG=3 it's also very clear, Direction is set to output and Value is controlled by timer/shifter state.

Now, what is not very clear is when it's configured with PINCFG=1 (control direction based on the state) or PINCFG=2 ( control value based on the state )

If you have two units driving the pin, that's fine, but what if you have only one unit? Where second piece of information is coming from?

In particular, if I have a timer with PINCFG=1, it will switch direction back and forth, but what is outputs value ( during output state phase )?

In my application I need a pin to be configured as Open Sink, so toggling direction will switch between HighZ and Vdd. So I would like to set output value as logical one and just let FlexIO to play with direction.

However. Seems like on KL27 it doesn't respect PDOR, so where is it stored?

So far, I've managed to achieve required behavior by allocating some other unit of FlexIO to drive pin's value (pincfg=2) and drive it to logical 1 constantly. But this is such a waste. Is there any ways around?

Thanks,

Vlad

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Are you able to use this FlexIO similar to MSC to connect to a TLE8718 for example?

I know there's a forum post about connecting an MPC to the TLE8718 using CSI (https://community.nxp.com/thread/439772 ), but I was curious if it's possible with this FlexIO on the S32K1xx for example.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I would like to know what is the maximum speed supported by FlexIO.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

@gerardo_rodriguez Thank you for your amazing write up. It has been invaluable in developing my project.

I would like to know how quickly the FlexIO timer can detect a pin input and trigger the transmitter shifter to shift data out. The best I have achieved so far is 28ns between the falling edge of a pin input that triggers the timer enable, which enables the shifter in transmit mode. I would like to bring this down to between 1 - 14 ns because the communication interface I am modelling requires that. The communication interface I am developing is modelled after the FT2232H chip's FT245 Style Asynchronous FIFO Interface which is a parallel 8 bit interface. I am tryin to send out 1 byte at a time.

The FlexIO clock is derived from the 400MHz RC oscillator on the RT1176 chip, scaled down to 100MHZ. The FlexIO module has an upper limit of 120MHz. This is my configuration:

This is the screenshot of the logic analyzer capture. I want the