- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

There's no sound output after DAP enabled. We set audio route as: I2S_IN -> DAP -> DAC -> LINEOUT/HP_OUT

snd_soc_write(codec, SGTL5000_DAP_CTRL, 0x0001);

snd_soc_write(codec, SGTL5000_CHIP_SSS_CTRL, 0x70);

snd_soc_write(codec, SGTL5000_DAP_PEQ, 0x0002);

snd_soc_write(codec, SGTL5000_DAP_AUDIO_EQ, 0x0001);

Any ideas or suggestions?

已解决! 转到解答。

Hello Qingwei,

I consulted SGTL5000 datasheet on how to program DAP, and found your steps are not complete.

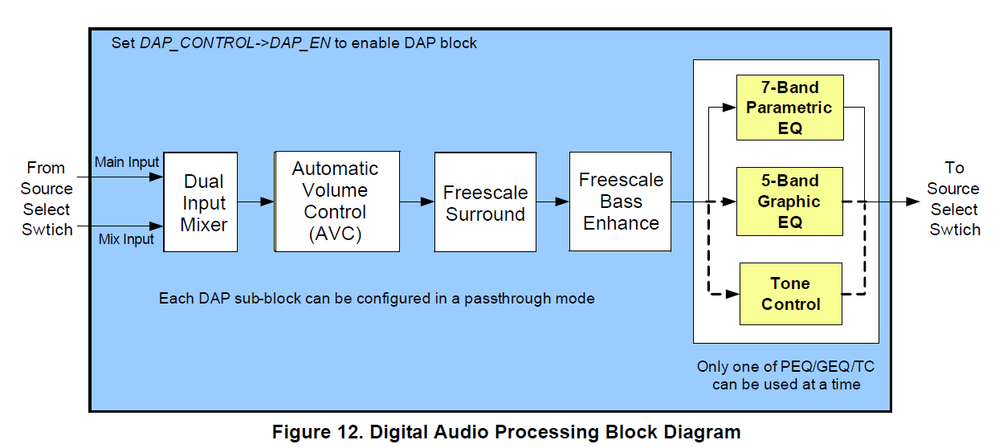

1. See DAP diagram

We should pay attention to notes about PEQ/GEQ/TC: Only one of them can work simultaneously, so you can only use one, but not more.

2. See example code of DAP

You had better carefully read these example code and understand them, see page27, let me paste parts of them here:

--Input/Output Routing( input / output of DAP )

To avoid any pops/clicks, the outputs should be muted during these chip configuration steps. Refer to Volume Control for volume and mute control.

A few example routes are shown below:

// Example 1: I2S_IN -> DAP -> DAC -> LINEOUT, HP_OUT

// Route I2S_IN to DAP

Modify CHIP_SSS_CTRL->DAP_SELECT 0x0001 // bits 7:6

// Route DAP to DAC

Modify CHIP_SSS_CTRL->DAC_SELECT 0x0003 // bits 5:4

// Select DAC as the input to HP_OUT

Modify CHIP_ANA_CTRL->SELECT_HP 0x0000 // bit 6

// Example 2: MIC_IN -> ADC -> I2S_OUT

// Set ADC input to MIC_IN

Modify CHIP_ANA_CTRL->SELECT_ADC 0x0000 // bit 2

// Route ADC to I2S_OUT

Modify CHIP_SSS_CTRL->I2S_SELECT 0x0000 // bits 1:0

// Example 3: LINEIN -> HP_OUT

// Select LINEIN as the input to HP_OUT

Modify CHIP_ANA_CTRL->SELECT_HP 0x0001 // bit 6

***DIGITAL AUDIO PROCESSOR CONFIGURATION

To avoid any pops/clicks, the outputs should be muted during these chip configuration steps. Refer to Volume Control for volume and mute control.

// Enable DAP block

// NOTE: DAP will be in a pass-through mode if none of DAP

// sub-blocks are enabled.

Modify DAP_CONTROL->DAP_EN 0x0001 // bit 0

----Dual Input Mixer

These programming steps are needed only if dual input mixer feature is used.

// Enable Dual Input Mixer

Modify DAP_CONTROL->MIX_EN 0x0001 // bit 4

// NOTE: This example assumes mix level of main and mix

// channels as 100% and 50% respectively

// Configure main channel volume to 100% (No change from input

// level)

Write DAP_MAIN_CHAN 0x4000

// Configure mix channel volume to 50% (attenuate the mix

// input level by half)

Write DAP_MIX_CHAN 0x4000

----Freescale Surround

The Freescale Surround on/off function is typically controlled by the end-user. End-user driven programming steps are shown in End-user Driven Chip Configuration.

The default WIDTH_CONTROL of 4 should be appropriate for most applications. This optional programming step shows how to configure a different width value.

// Configure the surround width

// (0x0 = Least width, 0x7 = Most width). This example shows

// a width setting of 5

Modify DAP_SGTL_SURROUND->WIDTH_CONTROL 0x0005

// bits 6:4

----7-Band Parametric EQ / 5-Band Graphic EQ / Tone Control

Only one audio EQ block can be used at a given time. The pseudocode in this section shows how to select each block.

Some parameters of the audio EQ are typically controlled by the end-user. End-user driven programming steps are shown in End-user Driven Chip Configuration.

// 7-Band PEQ Mode

// Select 7-Band PEQ mode and enable 7 PEQ filters

Write DAP_AUDIO_EQ 0x0001

Write DAP_PEQ 0x0007

// Tone Control mode

Write DAP_AUDIO_EQ 0x0002

// 5-Band GEQ Mode

Write DAP_AUDIO_EQ 0x0003

----Automatic Volume Control (AVC)

The AVC on/off function is typically controlled by the end-user. End-user driven programming steps are shown in End-user Driven Chip Configuration.

The default configuration of the AVC should work for most applications. However, the following example shows how to change the configuration if needed.

// Configure threshold to -18dB

Write DAP_AVC_THRESHOLD 0x0A40

// Configure attack rate to 16dB/s

Write DAP_AVC_ATTACK 0x0014

// Configure decay rate to 2dB/s

Write DAP_AVC_DECAY 0x0028

From example code, except setting DAP_EN, each sub-block of DAP should also be configured, so please read them and re-debug your codec.

Best Regards,

Weidong

Hi Weidong,

Thanks for your help. I just posted a fragment of DAP config.

Each DAP sub-block should work in pass through mode by default, so sound should always output from line-out when audio route switched to I2S_IN -> DAP -> DAC -> LINEOUT from I2S_IN -> DAC -> LINEOUT

We only need PEQ/GEQ function, and other sub-blocks work in pass through mode.

Could you give me a simple sample (regardless of any parameter value)?

Our complete configs:

snd_soc_write(codec, SGTL5000_DAP_CTRL, 0x0001);

snd_soc_write(codec, SGTL5000_CHIP_SSS_CTRL, 0x70);

snd_soc_write(codec, SGTL5000_DAP_PEQ, 0x0002);

snd_soc_write(codec, SGTL5000_DAP_AUDIO_EQ, 0x0001);

/* PEQ0 */

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B0_MSB, 0x5E6AA>> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B0_LSB, 0x5E6AA & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B1_MSB, 0xCC6A1 >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B1_LSB, 0xCC6A1 & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B2_MSB, 0xF958E >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B2_LSB, 0xF958E & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A1_MSB, 0x33960 >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A1_LSB, 0x33960 & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A2_MSB, 0xE83CA >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A2_LSB, 0xE83CA & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_FLT_COEF_ACCESS, (1 << 8 | 0));

/* PEQ1 */

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B0_MSB, 0x402B7 >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B0_LSB, 0x402B7 & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B1_MSB, 0x80D5D >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B1_LSB, 0x80D5D & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B2_MSB, 0x3F021 >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_B2_LSB, 0x3F021 & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A1_MSB, 0x7F2A4 >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A1_LSB, 0x7F2A4 & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A2_MSB, 0xC0D29 >> 4);

snd_soc_write(codec, SGTL5000_DAP_COEF_WR_A2_LSB, 0xC0D29 & 0x000f);

snd_soc_write(codec, SGTL5000_DAP_FLT_COEF_ACCESS, (1 << 8 | 1));