- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- imx8mm mini TMU need more accurate temperature calculation using calibration values

imx8mm mini TMU need more accurate temperature calculation using calibration values

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I need more accurate temperature reporting for the imx8mm processor. Empirical data taken using the linux source code currently does NOT use the factory calibration values for the TMU.

The driver source code is located here:

https://github.com/nxp-imx/linux-imx/blob/lf-6.1.y/drivers/thermal/imx8mm_thermal.c

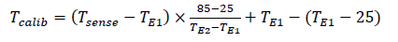

5.4.5 Temperature Sensor Error Correction Method.

, where Tsense=readl_relaxed(tmu->base + TRITSR) & TRITSR_TEMP0_VAL_MASK;

0x3035_04F0[15:8] TSENSOR_VALUE_HT[7:0] (high temp)

ERR051272: TMU: Bit 31 of registers TMU_TSCR/TMU_TRITSR/TMU_TRATSR invalid Description: Bit 31 of registers TMU_TSCR/TMU_TRITSR/TMU_TRATSR might be set as invalid value when the temperature varies in range.

Workaround: Do not use Bit 31 of registers TMU_TSCR/TMU_TRITSR/TMU_TRATSR. Suggest to read TMU value and use 1 point calibration to justify if the temperature is in range.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For Q1: No, default driver from NXP doesn't implement the following formula

For Q2, These are correct locations about TE1/TE2 from internal case.

0x3035_04F0[7:0] TSENSOR_VALUE_RT[7:0] (room temp)

0x3035_04F0[15:8] TSENSOR_VALUE_HT[7:0] (high temp)

For Q3:

For Q4, these references in i.MX8MM RM are not correct. These bits are in i.MX8MQ RM.

ALPF--> TMU_TER [ALPF]

ME-->MU_TER [EN]

MSITE-->ignore this bit in i.MX8MM. There are three monitor sites in i.MX8MQ TMU. But for i.MX8MM, there is only one site. You can find that with address offset.

For Q5, i can't find more description about ERR051272 from internal material. Please refer the workaround, Do not use Bit 31 of registers TMU_TSCR/TMU_TRITSR/TMU_TRATSR.

For example, The temperature is reported with an "invalid value" but is high AND still within bounds of VER1_TEMP_LOW_LIMIT and VER1_TEMP_HIGH_LIMIT.

--> This is correct explanation. That's why NXP not use V bit in the current driver.

Best Regards

Zhiming

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Checking to see if anyone can help with this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For Q1: No, default driver from NXP doesn't implement the following formula

For Q2, These are correct locations about TE1/TE2 from internal case.

0x3035_04F0[7:0] TSENSOR_VALUE_RT[7:0] (room temp)

0x3035_04F0[15:8] TSENSOR_VALUE_HT[7:0] (high temp)

For Q3:

For Q4, these references in i.MX8MM RM are not correct. These bits are in i.MX8MQ RM.

ALPF--> TMU_TER [ALPF]

ME-->MU_TER [EN]

MSITE-->ignore this bit in i.MX8MM. There are three monitor sites in i.MX8MQ TMU. But for i.MX8MM, there is only one site. You can find that with address offset.

For Q5, i can't find more description about ERR051272 from internal material. Please refer the workaround, Do not use Bit 31 of registers TMU_TSCR/TMU_TRITSR/TMU_TRATSR.

For example, The temperature is reported with an "invalid value" but is high AND still within bounds of VER1_TEMP_LOW_LIMIT and VER1_TEMP_HIGH_LIMIT.

--> This is correct explanation. That's why NXP not use V bit in the current driver.

Best Regards

Zhiming

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Follow up to

5.4.5 Temperature Sensor Error Correction Method.

, where Tsense=readl_relaxed(tmu->base + TRITSR) & TRITSR_TEMP0_VAL_MASK;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1.L6.6.y BSP will contain the patches you mentioned in future release.

2.Technical support doesn't have more document about SECRET UNDOCUMENTED TMU REGISTERS. So we can't give you more information.

3.For last question, need time to confirm.