- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hello,

I am trying to figure out how to update my u-boot to support 2GB of memory. Right now I can't even figure out what documentation to look through to find this. I have read through all the documentation on the documentation provided for the bsp as well as about a dozen related threads on this community. The following is what I have tried

First I am using fsl-yocto-L4.9.123_2.3.0 as that seems to be the latest build that the evk supports and it appears to work. https://www.nxp.com/docs/en/supporting-information/fsl-yocto-L4.9.123_2.3.0_mx8mm.zip

Per this thread https://community.nxp.com/t5/Layerscape/DDR-shows-1GB-instead-of-4GB-ls1021a/m-p/986048

it looks like I need to change PHYS_SDRAM_SIZE from 1gb to 2 gb. The first question. The relevant file is in two locations

./tmp/work/x86_64-linux/qemu-native/2.10.0-r0/qemu-2.10.0/roms/u-boot/include/configs/mx7ulp_evk.h

./tmp/work/imx7ulpevk-poky-linux-gnueabi/u-boot-imx/2017.03-r0/git/include/configs/mx7ulp_evk.h

Does it need to be changed in both locations? How do I determine what is the correct one? Besides changing SZ_1G to SZ_2G are there any other config changes on the evk board?

Next if I change source code in the tmp directory I know that "-c compile -f" is supposed to pick it up, but it doesn't, no new image is generated. in fact -c cleanall won't clean anything, my changes are still there. In all of these cases it just reports that nearly nothing needed to be rebuilt. Any ideas on how I can pick up changes in the tmp/work directory until I am ready to make a patch?

How can I determine what layer/package/recipe the mx7ulp_evk.h comes from so I can try to write a patch? I can't seem to find detailed documentation on the BSP?

Also I see that there are some u-boot config files https://source.codeaurora.org/external/imx/uboot-imx/tree/board/freescale/mx7ulp_evk?h=imx_v2018.03_... that seem to be part of what needs to be changed to update the dram settings I see from this thread here https://community.nxp.com/t5/i-MX-Processors-Knowledge-Base/i-MX7ULP-Register-Programming-Aids/ta-p/... that there are ddr register programming aids, but I am not sure how to integrate those settings into my linux bsp?

I know this is a lot but any help on any of these would be extremely helpful

已解决! 转到解答。

ok so are you confirming that this chip cannot support 2GB of ddr address space? page 590 section 22.5.4.2.2 of the pdf you referenced says

"If the DDR memory space allocation is 2 Gbytes, there are three options for configuringthe chip select partition:MDASP[CS0_END] to 001_1111 (1 Gbyte),MDASP[CS0_END] to 011_1111 (2 Gbytes), and MDASP[CS0_END] to 101_1111(3 Gbytes)."

If so I will assume the section I found is incorrect/typo and will mark this as solved.

Thank you for the reply. This will take me a bit to go through in detail and try out. on a side note for other people in the future, in order to patch the u-boot-imx the normal dev tool instructions don't work sense there is some other logic going on. I will paste what I did here just to help others

devtool modify u-boot-imx

#this creates the source you can modify in build/workspace/sources/u-boot-imx. you can't test it out before making the patch because the logic is broken. so then you need to commit the changes (it is a git repo under the hood) from the recipe directory

cd build/workspace/sources/u-boot-imx

git commit .

Then you need to create your own layer to save the patch in with at least one active recipe. for me it was sources/meta-mychanges/mychange. Not including here how to do that. Next you need to create the patch:

devtool update-recipe -a <layerpath> <recipename>

or

devtool update-recipe -a sources/meta-mychanges u-boot-imx

you should see the new files in your "mychange" recipe. then you need to clear the working directory of your modified u boot and finish

devtool reset u-boot-imx

now you need to clean the source of your bitbake target for it to work. For me it required a lot of falgs before it started working

bitbake -c cleanall -f -c compile -f -c fetchall -f -C compile fsl-image-validation-imx

now you can finally run

bitbake fsl-image-validation-imx

and if you look in your tmp/work directory the source should have the changes, and you should also be able to find your patch file too. You can now easily go into your own layer and deactivate it and it will return to normal

Hi meb99

except change PHYS_SDRAM_SIZE in u-boot/include/configs/mx7ulp_evk.h

for new ddr recommended to use RPA tool and run ddr test :

then update uboot dcd header with new ddr calibration settings found from ddr test

Build steps can be found in Yocto Guide from below link

also it shows in column "Supported Platforms" latest supported linux release for each processor.

Best regards

igor

ok I have gone through all of this in great detail to make it work. currently when I try to boot it just freezes at DRAM

U-Boot 2017.03-imx_v2017.03_4.9.88_2.0.0_ga+gb76bb1bf9f (Dec 18 2020 - 19:53:16 -0800)

CPU: Freescale i.MX7ULP rev2.0 at 500 MHz

Reset cause: POR

Boot mode: Dual boot

Model: NXP i.MX7ULP EVK

DRAM:

when I did the stress test calibration I got values that were fairly close to default

Read calibration

MPRDDLCTL PHY0 (0x40ab0848) = 0x383A343A

Write calibration

MPWRDLCTL PHY0 (0x40ab0850) = 0x32323432

The total things i changed to the u-boot-img recipe were:

mx7ulp_evk.h

#define PHYS_SDRAM_SIZE SZ_2G

and in imximage.cfg the following register values were updated

40AB0800 : A1310000 -> A1390003

40AB085C : 0D3900A0 -> 1B39009F

40AB0890 : 00400000 -> 00480000

40AB0848 : 40404040 -> 383A343A

40AB0850 : 40404040 -> 32323432

40AB0004 : 00020052 -> 00020012

40AB0010 : 00100A22 -> B6AD0B22

40AB0038 : 00120556 -> 00130556

40AB083C : 20000000 -> A0000000

40AB0404 : 00011006 -> 00010106

These were based on the Register programming aid (and the two that were from the calibrations)

There were no other changes I could see that needed to be done based on the four links you provided. That being said I could not get the stress test to run, it just sat there at the first frequency.

DDR Stress Test Iteration 1

DDR Freq: 297 MHz

t0.1: data is addr test

I left it there for 6 hour one time just to be sure. But the calibration worked fine, and I am using the eval board so I knew the MHZ were at 320.

Also every time I download any script to the stress test tool it always starts saying

" DDR configuration

DDR type is LPDDR3 in 1-channel mode.

Data width: 32, bank num: 8

Row size: 14, col size: 10

Both chip select CSD0 and CSD1 are used

Density per chip select: 512MB

Density per channel: 1024MB "

no matter what the drop down menu settings are.

Any help is greatly appreciated.

>That being said I could not get the stress test to run, it just sat there at the first frequency.

so seems custom board can not pass ddr test, that means memory is not working.

Reason may be hardware and software (configuration).

Hardware may be checked with Hardware Development Guide for the i.MX 7ULP Applications Processor

What ddr part used in the case LPDDR2 or LPDDR3, is it the same as on i.MX7ULP EVK.

Also please clarify what board used in the case : custom or EVK ?

Best regards

igor

This IS the EVK demo board (imx7ulpevk). I was trying to run the stress test on that. (This is also the board I am trying to configure for 2GB of memory, sense the memory chip that comes on the board is 8GB.

The memory should be fine, I have compiled and ran many different images on it, and everything seems to work great. The calibration seems to work fine when I set it to the 320MHZ it is supposed to run at.

I assumed there would be some documentation for how to reconfigure the demo board for 2GB.

if this is NXP i.MX7ULP EVK reference board, it has only 1GB LPDDR3 memory as described

in documentation, for example p.8 schematic spf-29163

MCIMX7ULP-EVK Design Files

Best regards

igor

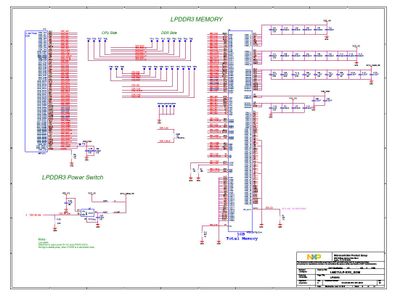

That schematic has that you shared has "NT6CL256T32CQ-H1" which is a 4GB LDDR3 module. I attached the datasheet for it. Not only that if you look at the bottom right it has the "AC11" -> DDR_ZQ1 for "2GB LDDR3". I might be missing something, but as far as i can tell this should have all the wiring to configure it for 2GB.

On a side note every single Application Board here has only 1GB of memory.

I know that section 22.5.4.2.2 of the application processor reference manual goes through configuration settings for 2GB of memory with 1 GB per chip select which the included memory module has. I admittedly have not gone through that as I was hoping the the Aide you referenced would provide those.

Any detail on why what exactly there is a 1GB limitation on the board would be helpful! thank you

>Any detail on why what exactly there is a 1GB limitation on the board would be helpful

Table 19-1. System memory map Reference Manual describes "DDR (1024 MB)" as available capacity.

i.MX7ULPRMB2: i.MX 7ULP Applications Processor Reference Manual for Silicon Revision B2

Best regards

igor

ok so are you confirming that this chip cannot support 2GB of ddr address space? page 590 section 22.5.4.2.2 of the pdf you referenced says

"If the DDR memory space allocation is 2 Gbytes, there are three options for configuringthe chip select partition:MDASP[CS0_END] to 001_1111 (1 Gbyte),MDASP[CS0_END] to 011_1111 (2 Gbytes), and MDASP[CS0_END] to 101_1111(3 Gbytes)."

If so I will assume the section I found is incorrect/typo and will mark this as solved.