- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- failed during ddr calibration

failed during ddr calibration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

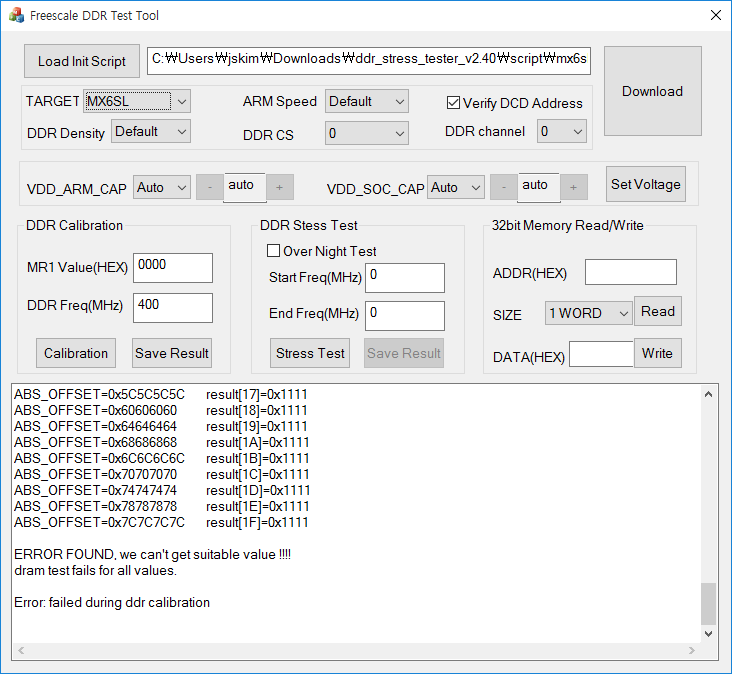

Hi all.

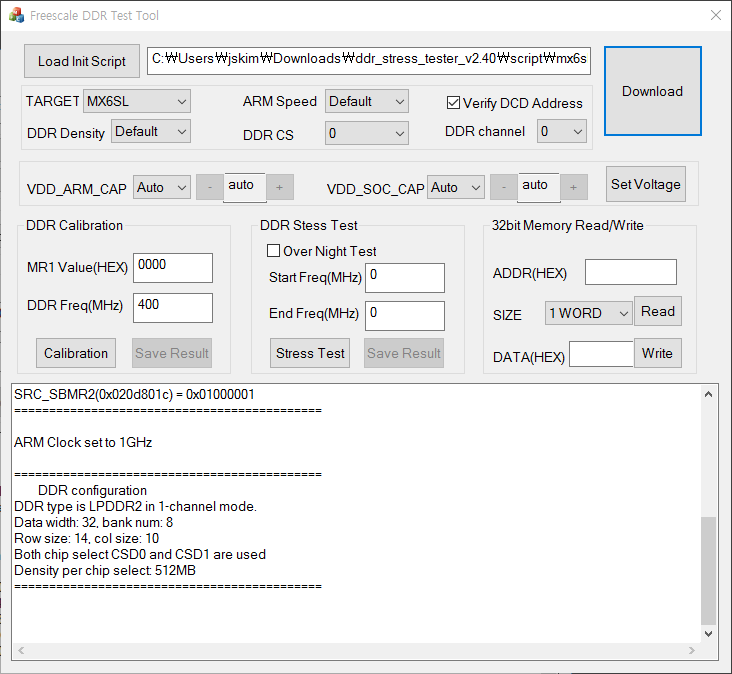

I am using IMX6 solo lite our custom board based on the MCIMX6SLEVK Board.

Our board structure was used same MCU and LPDDR2 part of reference board.

- our LPDDR2 part : MT42L256M32D2

Now I am having some problems on testing the DDR.

I have been trying to test calibration DDR2 on a DDR Test Tool with attached reference script file.

- tool : ddr_stress_tester_v2.40

- script : MX6SL_EVK_LPDDR2_512MB_32bit_v0.9.inc

But when I run DDR calibration, failed during ddr calibration on pc program.

Problem are as the below.

Message is "Error: failed during ddr calibration"

| 헤더 1 |

|---|

============================================ DDR Stress Test (2.4.0) Build: Dec 11 2015, 11:13:44 Freescale Semiconductor, Inc. ============================================

============================================ Chip ID CHIP ID = i.MX6 SoloLite (0x60) Internal Revision = TO1.2 ============================================

============================================ Boot Configuration SRC_SBMR1(0x020d8004) = 0x00002c40 SRC_SBMR2(0x020d801c) = 0x01000001 ============================================

ARM Clock set to 1GHz

============================================ DDR configuration DDR type is LPDDR2 in 1-channel mode. Data width: 32, bank num: 8 Row size: 14, col size: 10 Both chip select CSD0 and CSD1 are used Density per chip select: 512MB ============================================

Current Tempareture: 46 ============================================

DDR Freq: 396 MHz

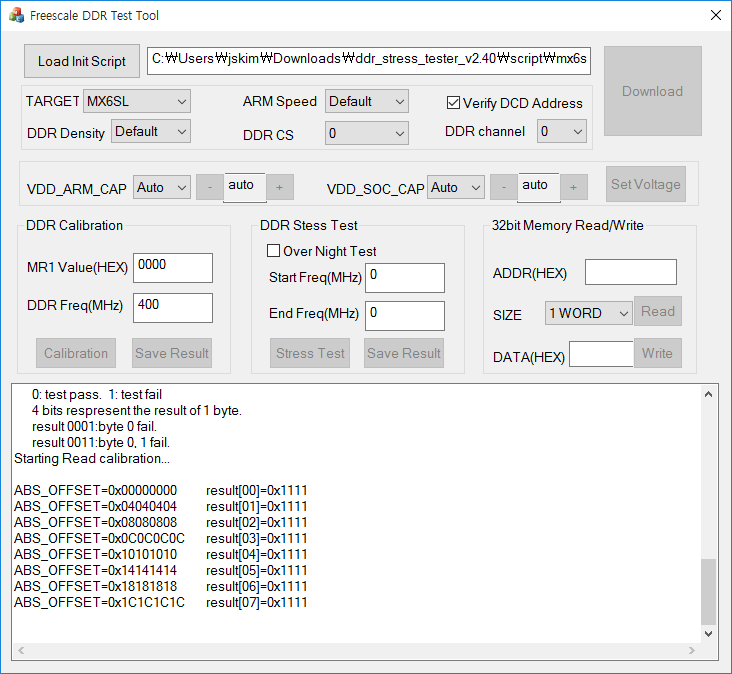

Note: Array result[] holds the DRAM test result of each byte. 0: test pass. 1: test fail 4 bits respresent the result of 1 byte. result 0001:byte 0 fail. result 0011:byte 0, 1 fail.

Starting Read calibration...

ABS_OFFSET=0x00000000 result[00]=0x1111 ABS_OFFSET=0x04040404 result[01]=0x1111 ABS_OFFSET=0x08080808 result[02]=0x1111 ABS_OFFSET=0x0C0C0C0C result[03]=0x1111 ABS_OFFSET=0x10101010 result[04]=0x1111 ABS_OFFSET=0x14141414 result[05]=0x1111 ABS_OFFSET=0x18181818 result[06]=0x1111 ABS_OFFSET=0x1C1C1C1C result[07]=0x1111 ABS_OFFSET=0x20202020 result[08]=0x1111 ABS_OFFSET=0x24242424 result[09]=0x1111 ABS_OFFSET=0x28282828 result[0A]=0x1111 ABS_OFFSET=0x2C2C2C2C result[0B]=0x1111 ABS_OFFSET=0x30303030 result[0C]=0x1111 ABS_OFFSET=0x34343434 result[0D]=0x1111 ABS_OFFSET=0x38383838 result[0E]=0x1111 ABS_OFFSET=0x3C3C3C3C result[0F]=0x1111 ABS_OFFSET=0x40404040 result[10]=0x1111 ABS_OFFSET=0x44444444 result[11]=0x1111 ABS_OFFSET=0x48484848 result[12]=0x1111 ABS_OFFSET=0x4C4C4C4C result[13]=0x1111 ABS_OFFSET=0x50505050 result[14]=0x1111 ABS_OFFSET=0x54545454 result[15]=0x1111 ABS_OFFSET=0x58585858 result[16]=0x1111 ABS_OFFSET=0x5C5C5C5C result[17]=0x1111 ABS_OFFSET=0x60606060 result[18]=0x1111 ABS_OFFSET=0x64646464 result[19]=0x1111 ABS_OFFSET=0x68686868 result[1A]=0x1111 ABS_OFFSET=0x6C6C6C6C result[1B]=0x1111 ABS_OFFSET=0x70707070 result[1C]=0x1111 ABS_OFFSET=0x74747474 result[1D]=0x1111 ABS_OFFSET=0x78787878 result[1E]=0x1111 ABS_OFFSET=0x7C7C7C7C result[1F]=0x1111

ERROR FOUND, we can't get suitable value !!!! dram test fails for all values.

Error: failed during ddr calibration |

We don't know what's the problem.

Please, give us some checking point.

And another question is

1. We use MT42L256M32D2 for DDR2. But I'm doubtful that part. Is MT42L256M32D2 is a same part, such as reference SDRAM on an evaluation board? (i.MX6 solo lite)

2. If the same part, What part or point do I need to check next?

Any pointers would be of great help.

Original Attachment has been moved to: MX6SL_EVK_LPDDR2_512MB_32bit_v0.9.inc.zip

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Junsil

one can try to enter "MR1" value in GUI, one can find it

from MX6SL_EVK_LPDDR2_512MB_32bit_v0.9.inc.zip:

| //============================================================================= | ||

| // LPDDR2 Mode Register Writes |

//=============================================================================

setmem /32 0x021b001c =0x82018030 // MRW: BA=0 CS=0 MR_ADDR=1 MR_OP=see Register Configuration

MR1=0x82

Also it makes sense to test with 1.03 version of ddr test

https://community.freescale.com/docs/DOC-96412

1. it is the same part

2. please recheck ddr connections, testing signals with oscillosope

It makes sense to attach jtag and try read/write on single address.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Junsil

one can try to enter "MR1" value in GUI, one can find it

from MX6SL_EVK_LPDDR2_512MB_32bit_v0.9.inc.zip:

| //============================================================================= | ||

| // LPDDR2 Mode Register Writes |

//=============================================================================

setmem /32 0x021b001c =0x82018030 // MRW: BA=0 CS=0 MR_ADDR=1 MR_OP=see Register Configuration

MR1=0x82

Also it makes sense to test with 1.03 version of ddr test

https://community.freescale.com/docs/DOC-96412

1. it is the same part

2. please recheck ddr connections, testing signals with oscillosope

It makes sense to attach jtag and try read/write on single address.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

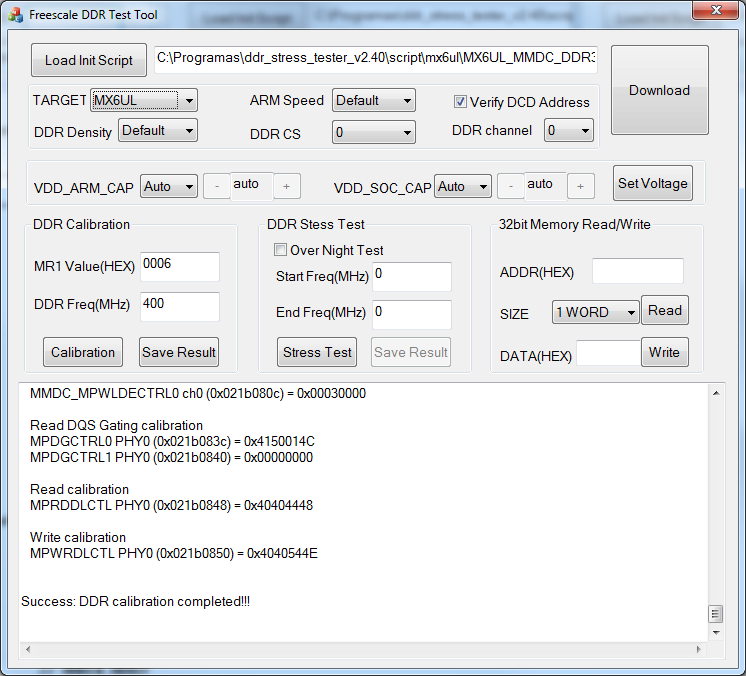

Hi Igor,

We are also having a hard time making a DDR test with DDR test tool.

In our case we have a MCIMX6UL-EVK and a customized board.

I have some doubts. As i see in the correct answer of this post, the issue was solved making MR1=0x82 that is the correct value in the .INC file.

I have tried with the EVK and with a different value of which should be in MR1 gap. I put MR1=0006 and it should be 0004. The calibration completed successfully.

What is this parameter for? is it really matters?

Now we are trying with our board with no succsses.

I have to say that the MFGTool does not achieve to jump to OS image so i guess we are not able to do anything with this tool, right?

Thanks and best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alberto

MR1 register is described in ddr datasheet. For custom

board suggest to check UG Ch.2 i.MX 6UltraLite design checklist

http://cache.freescale.com/files/32bit/doc/user_guide/IMX6ULHDG.pdf

then connect jtag and read/write patterns to memory, checking ddr signals

with oscilloscope.

>I have to say that the MFGTool does not achieve to jump to OS image so i guess we

>are not able to do anything with this tool, right?

right

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear igor,

Hi, I always appreciate your great help.

Thanks. Have a good day.

Best regards

Junsil