- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- ddr3 calibration error with IMX6UL custom board

ddr3 calibration error with IMX6UL custom board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ddr3 calibration error with IMX6UL custom board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,All

We made some custom board with IMX6UL chip and MT41K64M16-125 SDRAM,and encountered problems while doing ddr calibration on board by ddr_stress_tester_v3.00. There are calibration log as follow:

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00000870

SRC_SBMR2(0x020d801c) = 0x02000001

============================================

ARM Clock set to 528MHz

============================================

DDR configuration

DDR type is DDR3

Data width: 16, bank num: 8

Row size: 13, col size: 10

Chip select CSD0 is used

Density per chip select: 128MB

============================================

Current Temperature: 32

============================================

DDR Freq: 396 MHz

ddr_mr1=0x00000000

Start write leveling calibration...

running Write level HW calibration

MPWLHWERR register read out for factory diagnostics:

MPWLHWERR PHY0 = 0x00000087HW WL cal status: no suitable delay value found for byte 1

Write leveling calibration completed but failed, the following results were found:

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x001F0000

Write DQS delay result:

Write DQS0 delay: 0/256 CK

Write DQS1 delay: 31/256 CK

Error: failed during write leveling calibration

The script I used can make calibration success on official board IMX6ULEVK.

Hope you can give me some advice about what happen to my board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,all.

The problem solved after I replace the ddr3 density from 128 to 256 MB.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I measured some pin with oscilloscope showed as follow:

DRAM_SDCKE0= 0V

DRAM_SDCKE1= 0V,when doing calibration it came to 1.37V for about 16ms.

DRAM_VREF= 0.68V

DRAM_1V35= 1.37V

DRAM_RESET_B= 0V

XTALI= 22.5MHz

RTCXTALI= 33.3kHz

DRAM_RESET_B was always be 0V when downloading script or doing calibration.

If I am not misunderstanding,according to Hardware Development Guide for the i.MX 6UltraLite Applications Processor ,

DRAM_RESET_B should go High when board getting calibration.

I'll keep finding how the bug comes up.

If someone know how to deal with it,leave some comment,please.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one can try to write/read to memory with jtag checking signals with

osciloscope. Use jesd79 jedec ddr3 specificaton for signal description.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor.

Thanks for your reply.

I just retest DRAM_RESET_B and foud it goes High when the script downloaded in board.

I ran Memory Read/Write function and it worked,logs showed as below:

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x80000000: 0xE75BEBF7 0xD3FEEBBF 0xAD779B7C 0xAF66D3EE

0x80000010: 0x40A34A96 0xF55ECBC2 0xE6FCEFD4

0x80000020: 0xFDB055AE 0x176FBCBB 0x9BF3377F 0x9BD32ABD

0x80000030: 0xA4B5E7A5 0x658BE9EF 0x5ABB639E 0x1F9FDFF6

0x80000040: 0xFC799FBF 0xDFE55F2B 0xEEAC9DB9 0xB8FE8912

0x80000050: 0xB7FEC9CC 0xBDDEAAFF 0xE8BFDF6E 0xD7BB75FD

0x80000060: 0xB4819552 0x87FE8117 0xC7DFF563 0xA57A84FD

0x80000070: 0x773619BA 0xFF2F6778 0x7FFFFFFD 0xBD35FFB7

memory read is done

addr=0x80000000,data=0xE75BEBF8Success to write address 0x80000000

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x80000000: 0xE75BEBF8 0xD3FEEBBF 0xF6BE6DB5

0x80000020: 0xFDB055AE 0x176FBCBB 0x9BF3377F 0x9BD32ABD

0x80000030: 0xA4B5E7A5 0x658BE9EF 0x5ABB639E 0x1F9FDFF6

0x80000040: 0xFC799FBF 0xDFE55F2B 0xEEAC9DB9 0xB8FE8912

0x80000050: 0xB7FEC9CC 0xBDDEAAFF 0xE8BFDF6E 0xD7BB75FD

0x80000060: 0xB4819552 0x87FE8117 0xC7DFF563 0xA57A84FD

0x80000070: 0x773619BA 0xFF2F6778 0x7FFFFFFD 0xBD35FFB7

memory read is done

Memory read and write is work,but ddr calibration still failed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor

Thank for your response.

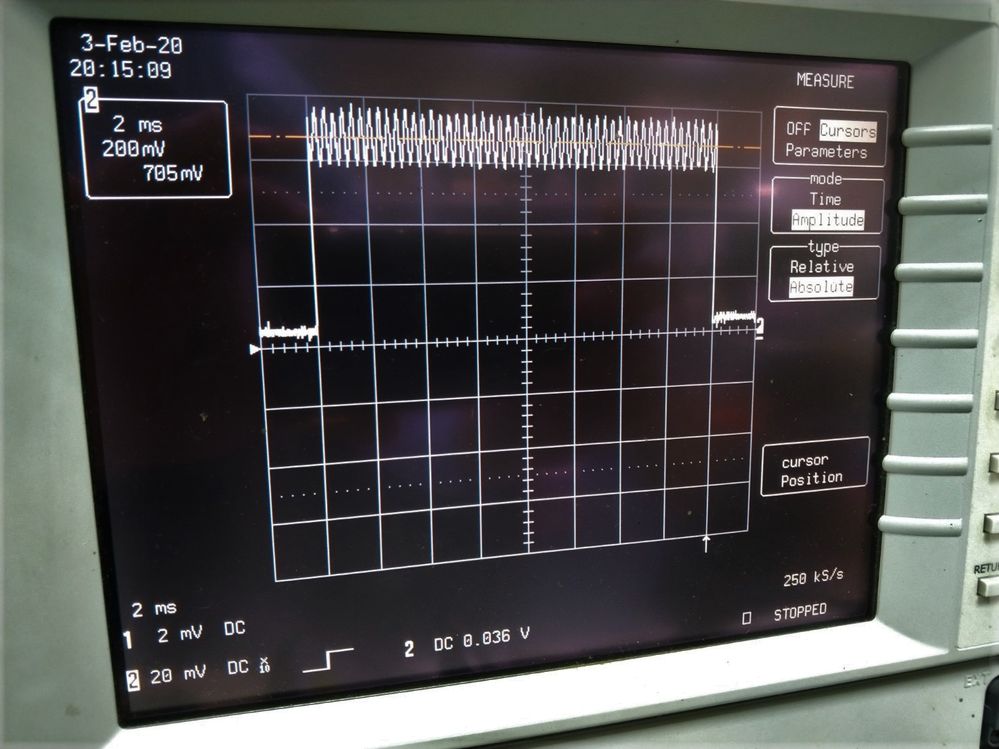

I captured a signal showed as followed when ddr test tool doing calibration.

The signal from DRAM SD_CLK0P:

The signal from SDQS0P and SDQS1P:

I think calibration failed because delay time of SDQS1 as log showed before.

Is there any possible way to fix delay time of SDQS1?

Thanks and best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi west

this may be caused by hardware, suggest to check it with oscilloscope using

Hardware Development Guide for the i.MX 6UltraLite Applications Processor

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor.

Thanks for your support.

I found some detail about this issue.

I hope you can look at this.

Thanks.