- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Why is LPSPI1 missing on v5.4 BSP for iMX8QXP?

Why is LPSPI1 missing on v5.4 BSP for iMX8QXP?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

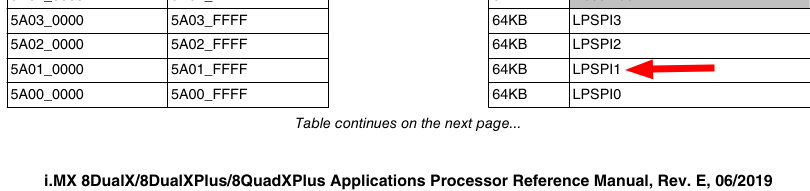

The HRM of the iMX8QXP shows there are four LPSPI buses:

The device tree however only lists three of them. LPSPI1 is missing and thus not available:

What's the issue here with LPSPI1?

Thank you,

Héctor Palacios

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hector

I asked internally, below answer

-------------------

Indeed, the lpspi1 node definition is missing from the dts, most likely because it can't be tested on the mek board.

But the definitions for the pinmux options for the lpspi1 external signals are already available in include/dt-bindings/pinctrl/pads-imx8qxp.h

As an addition to what you already provided in the public thread, you can also add the property necessary to be able to use the dma.

lpspi1: spi@5a010000 {

compatible = "fsl,imx7ulp-spi";

reg = <0x5a010000 0x10000>;

#address-cells = <1>;

#size-cells = <0>;

interrupts = <GIC_SPI 217 IRQ_TYPE_LEVEL_HIGH>;

interrupt-parent = <&gic>;

clocks = <&spi1_lpcg 0>,

<&spi1_lpcg 1>;

clock-names = "per", "ipg";

assigned-clocks = <&clk IMX_SC_R_SPI_1 IMX_SC_PM_CLK_PER>;

assigned-clock-rates = <20000000>;

power-domains = <&pd IMX_SC_R_SPI_1>;

dma-names = "tx","rx";

dmas = <&edma2 3 0 0>, <&edma2 2 0 1>;

status = "disabled";

};

This is for release 5.4.24.

-------------------

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @igorpadykov but the fact that LPSPI1 is not suitable for the MEK doesn't justify that the bus itself is not defined at all on the imx8-ss-dma.dtsi DTSI include file.

Besides, IMX8QXP_SPI1_xxx defines are missing from include/dt-bindings/pinctrl/pads-imx8qxp.h and thus not used either on drivers/pinctrl/freescale/pinctrl-imx8qxp.c

Do you have values for those? Because it looks like this bus and pads are completely missing from the BSP. That's why it looks like intentionally left out stuff.

Regards,

Hector

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hector

I asked internally, below answer

-------------------

Indeed, the lpspi1 node definition is missing from the dts, most likely because it can't be tested on the mek board.

But the definitions for the pinmux options for the lpspi1 external signals are already available in include/dt-bindings/pinctrl/pads-imx8qxp.h

As an addition to what you already provided in the public thread, you can also add the property necessary to be able to use the dma.

lpspi1: spi@5a010000 {

compatible = "fsl,imx7ulp-spi";

reg = <0x5a010000 0x10000>;

#address-cells = <1>;

#size-cells = <0>;

interrupts = <GIC_SPI 217 IRQ_TYPE_LEVEL_HIGH>;

interrupt-parent = <&gic>;

clocks = <&spi1_lpcg 0>,

<&spi1_lpcg 1>;

clock-names = "per", "ipg";

assigned-clocks = <&clk IMX_SC_R_SPI_1 IMX_SC_PM_CLK_PER>;

assigned-clock-rates = <20000000>;

power-domains = <&pd IMX_SC_R_SPI_1>;

dma-names = "tx","rx";

dmas = <&edma2 3 0 0>, <&edma2 2 0 1>;

status = "disabled";

};

This is for release 5.4.24.

-------------------

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Héctor

there is no issue here with LPSPI1, on MEK board suitable pads are used for

other peripherals, muxing options can be found in sect.9.1.External Signals and Pin Assignments

i.MX 8DualXPlus/8QuadXPlus Applications Processor Reference Manual

As example one can try below:

Fsl-imx8dx.dtsi :

lpspi1: lpspi@5a010000 {

compatible = "fsl,imx7ulp-spi";

reg = <0x0 0x5a010000 0x0 0x10000>;

interrupts = <GIC_SPI 217 IRQ_TYPE_LEVEL_HIGH>;

interrupt-parent = <&gic>;

clocks = <&clk IMX8QXP_SPI1_CLK>,

<&clk IMX8QXP_SPI1_IPG_CLK>;

clock-names = "per", "ipg";

assigned-clocks = <&clk IMX8QXP_SPI1_CLK>;

assigned-clock-rates = <20000000>;

power-domains = <&pd_dma_lpspi1>;

status = "disabled";

};

Fsl-imx8qxp-mek.dts:

pinctrl_lpspi1: lpspi1grp {

fsl,pins = <

SC_P_SAI0_TXFS_ADMA_SPI1_SCK 0xD600004c

SC_P_SAI0_TXD_ADMA_SPI1_SDO 0xD600004c

SC_P_SAI0_TXC_ADMA_SPI1_SDI 0xD600004c

>;

};

pinctrl_lpspi1_cs: lpspi1cs {

fsl,pins = <

SC_P_SAI0_RXD_LSIO_GPIO0_IO27 0xE0000021

>;

};

&lpspi1 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lpspi1 &pinctrl_lpspi1_cs>;

cs-gpios = <&gpio0 27 GPIO_ACTIVE_LOW>;

status = "okay";

spidev@0 {

compatible = "rohm,dh2228fv";

status = "okay";

spi-max-frequency = <1000000>;

reg = <0>;

};

};

driver clk-imx8qxp.c

clks[IMX8QXP_SPI1_CLK] = imx_clk_gate_scu("spi1_clk", "spi1_div", SC_R_SPI_1, SC_PM_CLK_PER, (void __iomem *)(LPSPI_1_LPCG), 0, 0);

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

-removed-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

-removed-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

-removed-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

-removed-