- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

What should be the address byte in QSPI for accessing 64 Mega Bytes of flash ?

Hello,

We are using 64 MegaBytes of flash.

I have a few questions regarding the accessibility to this flash.

1. What should be the address byte in QSPI for accessing 64 MegaBytes of flash?

2. Can we use 3 bytes address to access the complete 64 Megabytes of flash?

3. What happens if we use 3 bytes address to access the complete 64 Megabytes of flash?

4. Do we need to update LUT with commands for 4 bytes read and write if it is a 4-byte address?

5. If we are doing a quad page program of 256byte what should be the value of the number of write bytes?

Example: For 128 bytes it is 0x80 then for 256bytes it should be?

6. If we are reading 256byte of data what should be the value of the number of read bytes? Example: For 128 bytes it is 0x80 then for 256bytes it should be?

First of all, as question, which i.MX you are using? i.MX6SX, i.MX8M? etc ...

Second, which version of BSP from NXP you are using?

But technically, it is not a question of i.MX Processors community.

QSPI nor flash using simulation of linear address as parallel nor flash.

Read QSPI nor like read a parallel nor flash. Linux layer, you will find it is using mtd driver as parallel nor does.

QSPI nor uses quit different way to access. The QSPI controller has register to map the address.

Of course, if really want to separate it. You need to know which mode of QSPI, Individual Flash Mode? Parallel Flash Mode?

The QSPI nor flash connect to the QSPI controller(here is imx QSPI interface) is a flash supports QSPI mode. not a spi nor flash. this kind of flash need to configure the settings to use it.

3B, 4B address is for spi nor.

If you read the linux source, you will find it will switch the address mode 3B/4B by nor flash size.

Have you ever read the linux source code?

The code is linux code not i.MX flexspi/qspi/spi controllor code.

Because you questions are very confusing. could not tell what you want to ask? about a QSPI nor or spi nor? questions are contradictory to each other.

rel_imx_4.14.98_2.0.0_ga

linux-imx/drivers/mtd/spi-nor/spi-nor.c

linux-imx/drivers/mtd/spi-nor/spi-nor.c

int spi_nor_scan(struct spi_nor *nor, const char *name,

2709 const struct spi_nor_hwcaps *hwcaps)

2865 nor->addr_width = info->addr_width;

2866 } else if (mtd->size > 0x1000000) {

2867 /* enable 4-byte addressing if the device exceeds 16MiB */

2868 nor->addr_width = 4;

2869 if (JEDEC_MFR(info) == SNOR_MFR_SPANSION ||

2870 info->flags & SPI_NOR_4B_OPCODES)

2871 spi_nor_set_4byte_opcodes(nor, info);

2872 else

2873 set_4byte(nor, info, 1);

2874 } else {

Hello @BiyongSUN,

Thank you for your reply.

I am using imx6ul.

I am not using Linux bsp.

I am using a bare-metal code prepared using SDK_2.2_MCIM6UL.

I am using QSPI-NOR.

I am using Micron flash MT25QL512ABB.

In the datasheet of MT25QL512ABB, I came across the line "The 3-byte address mode can only access 128Mb of memory". And then I got this question whether we can use 3B for accessing 64MB or 1GB flash or not.

As per your reply, I understood that the 3B and 4B are used based upon the flash size and are applicable only in the case of SPI-NOR Flash.

The 3B and 4B are not applicable in the case of QSPI-NOR Flash. That means I can use 3B and do read, write, program, operations for 64MB/512MB/1GB, or 2GB sized NOR Flash.

Please correct me if my understanding is wrong.

If the spi nor flash > 16MB(128Mb), it certainly has command to switch to 4B mode.

But QSPI can connect to 4 spi nor flash working together. That is to say, you can use up to 64MB under 3B address mode(actually, no such concept under qspi mode).

the data sheet says "The 3-byte address mode can only access 128Mb of memory"

128Mb, the b is lowercase. it is bit not Byte. it is 16MB.

If you can find 4G spi nor, you can use the 4B address to access it as a standard spi nor.

But the Soc, here is i.MX6UL, has design to map the 256MB QSPI linear address.

That is to say is you have a spi nor 512MB, you can use the whole device as a standard spi nor flash. But only can use 256MB(half) for QSPI for this device.

Because QSPI needs linear address. QSPI simulates as parallel nor, as sdram-like device.

If you have a SOC, can map 4G for QSPI in the memory map design, you can use the 4G QSPI by this kind of SOC.

It supports the dual/quad io protocol for QSPI nor.

3B/4B is for spi nor.

Have you carefully read my previous reply?

MT25QL512ABB datasheet shows it supports QSPI (dual/quad) mode.

As the previous reply, you need to configure it.

• Supported protocols in both STR and DTR

– Extended I/O protocol

– Dual I/O protocol

– Quad I/O protocol

The address region for QSPI is still 3B/4B spi nor region, If you read the protocol spec.

The protocol spec is the common, not only for the i.MX.

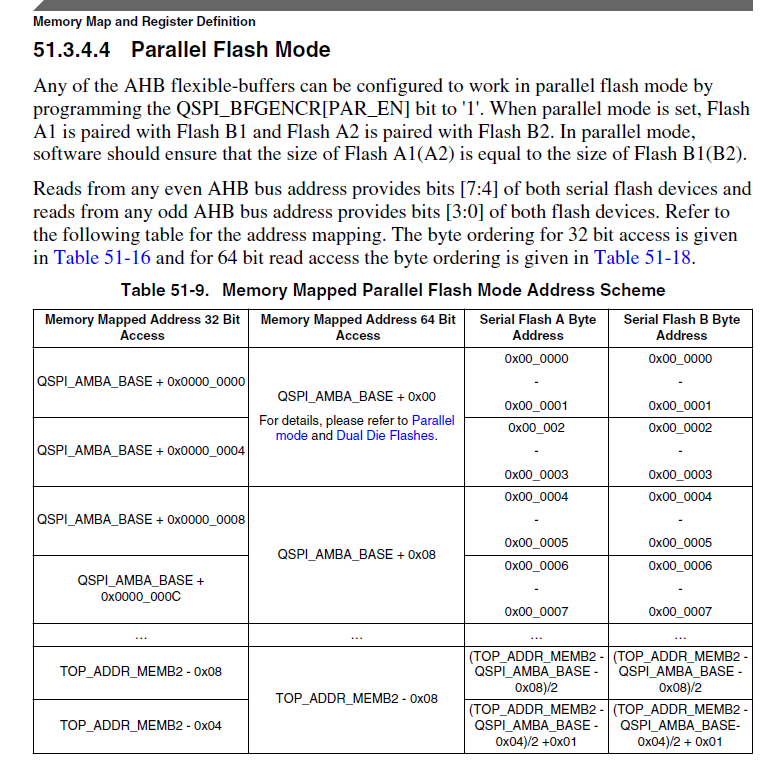

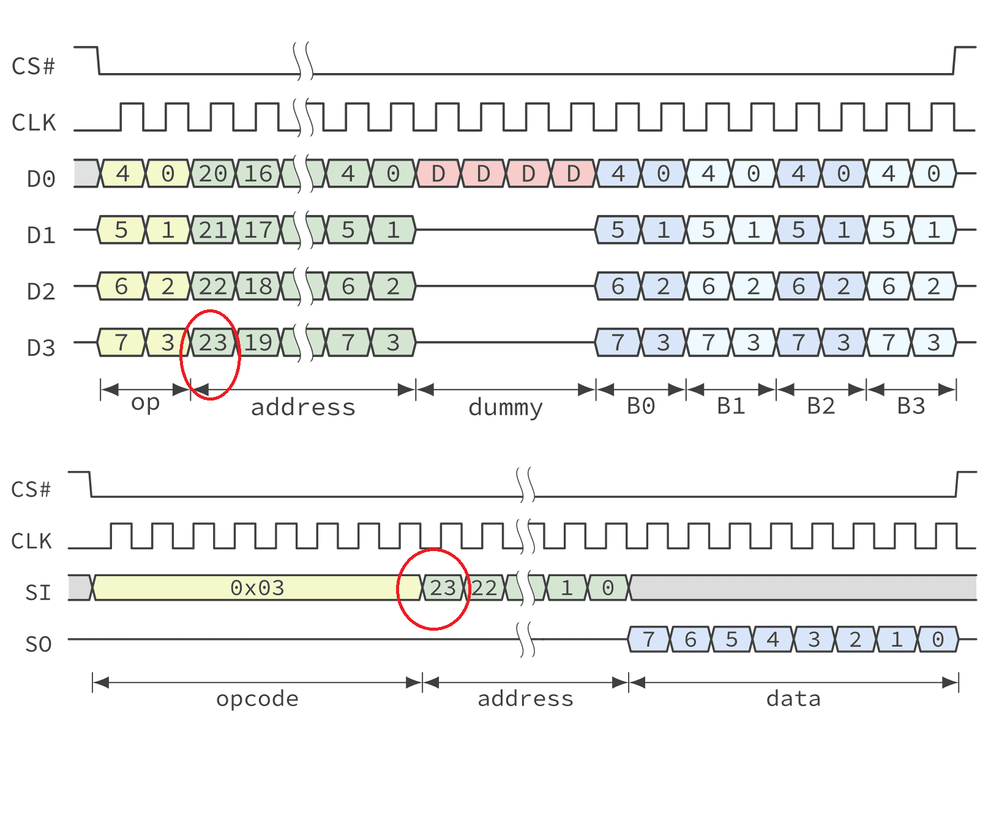

The figure shows the 24bit address.

Thank you very much for your help.

Now, I have understood it.

I also asked in my question if I can write/read 256 Byte in one go.

And if I can write or read 256 bytes in one go, what will be the data size value I need to send while doing the read/write operation?

As per the datasheet, If I have to read/write 128 bytes then I should use 0x80 as data size which is actually the hex representation of decimal 128.

But, what will be the value for writing or reading 256 Byte?

Will it be 0x100 for 256 Byte?