- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Simple GPIO Example - quandry

Simple GPIO Example - quandry

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Simple GPIO Example - quandry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to build a simple GPIO Toggle Example on the IMX6UL UltraLite Board.

I have had no success yet.

I have created a simple HelloWorld project.

But, I can not expand it to include GPIO Access.

I can Not figure out how to include files such as gpio.h

But all of these fail: <gpio.h> <Linux/gpio.h> "Linux/gpio.h" etc..

#include <stdio.h>

#include <gpio.h>

typedef unsigned long U32;

typedef unsigned short U16;

typedef unsigned char U8;

#define MX6SL_PAD_EPDC_SDCLK__GPIO1_IO23 0x110 0x400 0x000 0x5 0x0

// IOMUXC_SW_MUX_CTL_PAD_GPIO_1_23 = 20E_0000h base + 0x010

#define GPIO_1_23_MUX_CTL ( 0x2000000 + 0x0110 )

// IOMUXC_SW_PAD_CTL_PAD_GPIO_1_23 = 20E_0000h base + 0x000

#define GPIO_1_23_PAD_CTL ( 0x2000000 + 0x0400 )

// IOMUXC_SW_PAD_INPUT_GPIO_1_23 = 20E_0000h base + 0x0000

#define GPIO_1_23_INPUT ( 0x2000000 + 0x0000 )

// IOMUXC_SW_MUX_DATA_GPIO_1_23 = 0x05

#define GPIO_1_23_MUX_DATA ( 0x05 )

// IOMUXC_SW_CTL_DATA_GPIO_1_23 = 1 << 0x00

#define GPIO_1_23_CTL_DATA ( 0x01 << 0x00 )

#define MX6SL_PAD_EPDC_SDLE__GPIO1_IO24 0x114 0x404 0x000 0x5 0x0

#define MX6SL_PAD_EPDC_SDOE__GPIO1_IO25 0x118 0x408 0x000 0x5 0x0

#define MX6SL_PAD_EPDC_SDSHR__GPIO1_IO26 0x11c 0x40c 0x000 0x5 0x0

int _t_;

#define msleep(n) for(_t_=1; _t_<10000; _t_++){_t_=_t_;}

#define true 1

//#define IMX_GPIO_NR(port, index) ((((port)-1)*32)+((index)&31))

#define IMX_GPIO_NR(b,p) ( ((b - 1) * 32) + p )

int main(int argc, char **argv)

{

printf("Hello World!\n");

gpio_request(IMX_GPIO_NR(3, 11), "external_gpio_0");

gpio_export(IMX_GPIO_NR(3, 11), true);

gpio_request(IMX_GPIO_NR(3, 27), "external_gpio_1");

gpio_export(IMX_GPIO_NR(3, 27), true);

gpio_direction_output( IMX_GPIO_NR(1,0) , 1 );

msleep(300);

gpio_direction_output( IMX_GPIO_NR(2,18) , 1 );

msleep(300);

gpio_direction_output( IMX_GPIO_NR(2,19) , 1 );

msleep(300);

gpio_direction_output( IMX_GPIO_NR(1,20) , 0 );

gpio_direction_output( UART2_TX_DATA , 0 );

gpio_direction_output( IMX_GPIO_NR(1,21) , 0 );

gpio_direction_output( UART2_RX_DATA , 0 );

gpio_set_value(IMX_GPIO_NR(1, 0) , 1);

gpio_set_value(IMX_GPIO_NR(2, 18) , 1);

gpio_set_value(IMX_GPIO_NR(2, 19) , 1);

gpio_direction_output( IMX_GPIO_NR(1,23) , 1 );

gpio_set_value(IMX_GPIO_NR(1, 23) , 1);

msleep(1000);

gpio_set_value(IMX_GPIO_NR(1, 23) , 0);

msleep(1000);

gpio_set_value(IMX_GPIO_NR(1, 23) , 1);

msleep(1000);

gpio_export(IMX_GPIO_NR(1, 23), true);

gpio_direction_output( IMX_GPIO_NR(1,23) , 1 );

gpio_set_value(IMX_GPIO_NR(1, 23) , 1);

return 0;

}

I have also tried direct register access, but just got segment faults:

#include <stdio.h>

int main(int argc, char **argv)

{

printf("Hello World!\n");

//printf("\nset MUX\n");

// *((long*)0x0209C000??) = (5); // -set MUX

printf("\nset DIR\n");

*((long*)0x0209C004) = (1 << 23); // -set GPIO_1_23.Dir = 1

printf("\nset DATA 23\n");

*((long*)0x0209C000) = (1 << 23); // -set GPIO_1_23.Dat = 1

return 0;

}

Also this segmentation fault :

#include <stdio.h>

#define AIPS1_ARB_BASE_ADDR 0x02000000

#define AIPS1_ARB_END_ADDR 0x020FFFFF

#define AIPS2_ARB_BASE_ADDR 0x02100000

#define AIPS2_ARB_END_ADDR 0x021FFFFF

#define AIPS_TZ1_BASE_ADDR AIPS1_ARB_BASE_ADDR

#define AIPS_TZ2_BASE_ADDR AIPS2_ARB_BASE_ADDR

#define AIPS1_ON_BASE_ADDR (AIPS_TZ1_BASE_ADDR+0x7C000)

#define AIPS1_OFF_BASE_ADDR (AIPS_TZ1_BASE_ADDR+0x80000)

#define GPIO1_BASE_ADDR (AIPS1_OFF_BASE_ADDR+0x1C000)

#define IOMUXC_BASE_ADDR (AIPS1_OFF_BASE_ADDR+0x60000)

#define CCM_BASE_ADDR (AIPS1_OFF_BASE_ADDR+0x44000)

#define reg_32_CSU_SA (*(volatile U32*)(0x021C0218))

#define NSA_CP15 1

#define R32 (volatile unsigned long *)

#define R16 (volatile unsigned short *)

#define R8 (volatile unsigned char *)

typedef unsigned long U32;

typedef unsigned short U16;

typedef unsigned char U8;

int _t_;

#define msleep(n) for(_t_=1; _t_<10000; _t_++){_t_=_t_;}

#define true 1

int main(int argc, char **argv)

{

printf("Hello World!\n");

//Write to DIR register [DIR]

*R32(GPIO1_BASE_ADDR+4) = 0x00000004; // 1 : GPIO 1_2 - output

*R32 (GPIO1_BASE_ADDR) = 0x00000004; // 1 --> GPIO 1_2

*R32 ( GPIO1_BASE_ADDR) = 0 ; // 0 --> GPIO 1_2

return 0;

}

//

I also tried adding these lines below in the conf/bblayers.conf file, but still with No Results :

FILESPATH_append = "~/yocto_3.14.38-6UL/build/tmp/work/cortexa7hf-vfp-neon-poky-linux-gnueabi/linux-libc-headers/3.14-r0/linux-3.14/include/linux:"

FILESPATH_append = "~/yocto_3.14.38-6UL/build/tmp/work/cortexa7hf-vfp-neon-poky-linux-gnueabi/linux-libc-headers/3.14-r0/linux-3.14/include:"

FILESEXTRAPATHS_prepend := "${THISDIR}/files:"

FILESEXTRAPATHS_append = "~/yocto_3.14.38-6UL/build/tmp/work/cortexa7hf-vfp-neon-poky-linux-gnueabi/linux-libc-headers/3.14-r0/linux-3.14/include/linux:"

FILESEXTRAPATHS_append = "~/yocto_3.14.38-6UL/build/tmp/work/cortexa7hf-vfp-neon-poky-linux-gnueabi/linux-libc-headers/3.14-r0/linux-3.14/include:"

SRC_URI += "~/yocto_3.14.38-6UL/build/tmp/work/cortexa7hf-vfp-neon-poky-linux-gnueabi/linux-libc-headers/3.14-r0/linux-3.14/include/linux/gpio.h"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Christopher,

I tried the gpiotoggle.sh but with no pin level changes.

I even wrote a script to cover All Gpios - but with No changes on the Pin Voltages.

vi setGpioAllOut.sh

#!/bin/sh

for i in {1..255}

do

echo $i > /sys/class/gpio/export

echo "out" > /sys/class/gpio/gpio$i/direction

echo "1" > /sys/class/gpio/gpio$i/value

# cat /sys/class/gpio/gpio$i/value

done

chmod 777 setGpioAllOut.sh

./setGpioAllOut.sh

I can not compile GpioMod.c :

Log data follows:

| DEBUG: Executing shell function do_compile

| helloworld4.c:171:72: fatal error: linux/module.h: No such file or directory

| #include <linux/module.h> // dynamic loading of modules into the kernel

| compilation terminated.

| WARNING: exit code 1 from a shell command.

I have not been able to figure out how to add the extra include paths for <linux/..>.

Note: I am using the Ultralite board.

I am running the Minimal compile Image.

I am logged in as Root.

There must be something missing on Gpio config or enables. (But I have changed nothing)

What is left ?

John.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

something wrong with your reference voltage?

are you measuring against GND or 3,3/1,8V??

i do compile GpioMod.c on target with the makefile in the examples directory. just add the target name in line #1.

using yocto you have to ad following to your local.conf:

IMAGE_FEATURES_append = " tools-sdk dev pkgs "

IMAGE_INSTALL_append = " kernel-dev "

after boot:

- log in

- call: cd /usr/src/kernel

make silentoldconfig scripts

- run your makefile

i dont know if you have to add your GPIOS to the device tree.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Appended to local.conf :

IMAGE_FEATURES_append = " tools-sdk dev pkgs "

IMAGE_INSTALL_append = " kernel-dev "

ERROR: Nothing PROVIDES 'core-image-minimal'

ERROR: core-image-minimal was skipped: 'pkgs' in IMAGE_FEATURES (added via EXTRA_IMAGE_FEATURES) is not a valid image feature. Valid features: allow-empty-password dbg-pkgs debug-tweaks dev-pkgs doc doc-pkgs eclipse-debug empty-root-password hwcodecs nfs-server package-management post-install-logging ptest-pkgs qt4-pkgs qtcreator-debug read-only-rootfs splash ssh-server-dropbear ssh-server-openssh staticdev-pkgs tools-debug tools-profile tools-sdk tools-testapps x11 x11-base x11-sato

Summary: There was 1 ERROR message shown, returning a non-zero exit code.

Voltages should be correct.

I am reading 5V and 3.3V on the source pins.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

oops! sorry! should be dev-pkgs!

can you check your devicetree?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please check your IOMUX in devicee tree.

If you don't want to modify the code, you can use the memtool to set the IOMUX for GPIO.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Biyong,

I am really interested in working the way you have suggested. If I understand correctly, I don't need to modify the device tree everytime I want to check a different GPIO configuration .... is this right?

I would appreciate very much that you could show me how to do it with a concrete example ( I have few experience with embedded linux). I am also using imx6ulevk and would like to use arduino expansion port for gpio purposes.

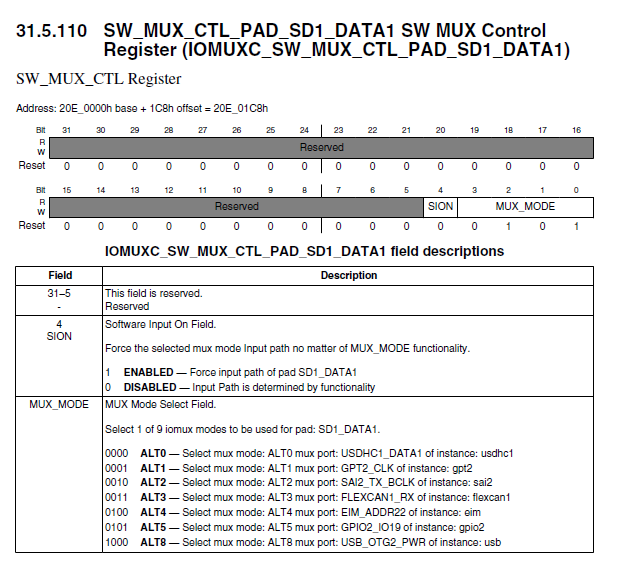

SD1_DATA1 is configured in the device tree as:

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

imx6ul-evk {

....

pinctrl_usdhc1: usdhc1grp {

fsl,pins = <

......

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x17059

......

>;

};

pinctrl_usdhc1_100mhz: usdhc1grp100mhz {

fsl,pins = <

.......

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170b9

......

>;

};

pinctrl_usdhc1_200mhz: usdhc1grp200mhz {

fsl,pins = <

......

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170f9

.......

>;

};

.....

}

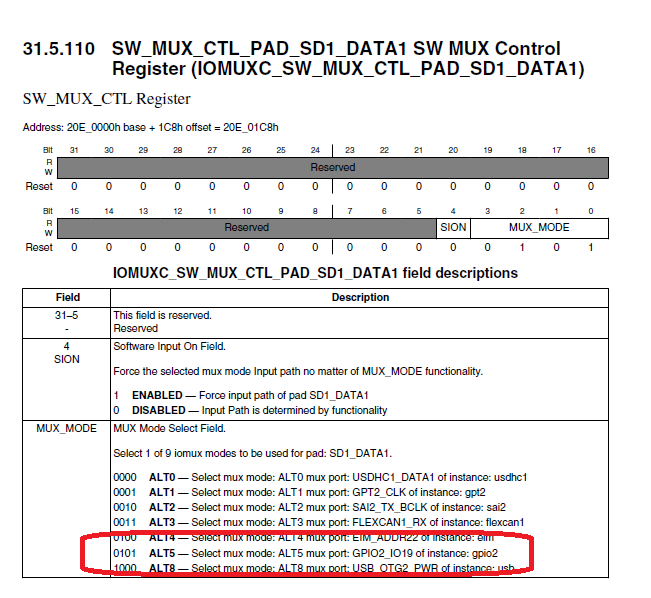

as I am only using sdh2, I can completely redefine the use of these pins and SD1_DATA1 could be a gpio: MX6UL_PAD_SD1_DATA1__GPIO2_IO19

How can I redefine the use of this pin without modifying the device tree by using memtool?

Could you please illustrate this example as a reference?

Thank you in advance!

BR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Using memtool to set IOMUX as GPIO is just for test.

In the real project, you should modify the device tree.

memtool is very useful debug tool. Not only can configure pad as GPIO but others as well.

Here is example:

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1 Addr:0x020E01C8 Value:0x00000000 - SW_MUX_CTL Register

IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE(0..3) :0x0

Select 1 of 9 iomux modes to be used for pad: SD1_DATA1.

IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.SION(4..4) :0x0

Force the selected mux mode Input path no matter of MUX_MODE functionality.

oot@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE=5

SOC: i.MX6UL

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1 Addr:0x020E01C8 Value:0x00000005 - SW_MUX_CTL Register

IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE(0..3) :0x5

Select 1 of 9 iomux modes to be used for pad: SD1_DATA1.

IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.SION(4..4) :0x0

Force the selected mux mode Input path no matter of MUX_MODE functionality.

Note sometime you need to set the pad ctrl.

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1 Addr:0x020E0454 Value:0x00017059 - SW_PAD_CTL Register

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.SRE(0..0) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.DSE(3..5) :0x3

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.SPEED(6..7) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.ODE(11..11) :0x0

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.PKE(12..12) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.PUE(13..13) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.PUS(14..15) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.HYS(16..16) :0x1

Select one out of next values for pad: SD1_DATA1

you can use "."(dot) to list all:

root@imx6ulevk:~# /unit_tests/memtool .

SOC: i.MX6UL

Module Base Address

ADC1 0x02198000

ADC2 0x0219C000

APBH 0x01804000

ASRC 0x02034000

BCH 0x01808000

CCM 0x020C4000

CCM_ANALOG 0x020C8000

CSI 0x021C4000

ECSPI1 0x02008000

ECSPI2 0x0200C000

I2S1 0x02028000

I2S2 0x0202C000

I2S3 0x02030000

IOMUXC 0x020E0000

IOMUXC_GPR 0x020E4000

KPP 0x020B8000

LCDIF 0x021C8000

MMDC 0x021B0000

Not only the IOMUX but other module registers you can check.

root@imx6ulevk:~# /unit_tests/memtool GPT1.

SOC: i.MX6UL

GPT1 Addr:0x2098000

GPT1.CR Addr:0x02098000 Value:0x00000749 - The GPT Control Register (GPT_CR) is used to program and configure GPT operations.

GPT1.CR.EN(0..0) :0x1

GPT Enable.

GPT1.CR.ENMOD(1..1) :0x0

GPT Enable mode.

GPT1.CR.DBGEN(2..2) :0x0

GPT debug mode enable.

GPT1.CR.WAITEN(3..3) :0x1

GPT Wait Mode enable.

GPT1.CR.DOZEEN(4..4) :0x0

GPT Doze Mode Enable.

GPT1.CR.STOPEN(5..5) :0x0

GPT Stop Mode enable.

GPT1.CR.CLKSRC(6..8) :0x5

Clock Source select.

GPT1.CR.FRR(9..9) :0x1

Free-Run or Restart mode.

GPT1.CR.EN_24M(10..10) :0x1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay Biyong,

I am running the memtool.

I tried following:

# echo 114 > /sys/class/gpio/export

# echo "out" > /sys/class/gpio/gpio114/direction

# echo 1 > /sys/class/gpio/gpio114/value

# ./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE=5

# ./memtool IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1=0x00017059

./memtool IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1 Addr:0x020E0454 Value:0x00000049 - SW_PAD_CTL Register

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.SRE(0..0) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.DSE(3..5) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.SPEED(6..7) :0x1

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.ODE(11..11) :0x0

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.PKE(12..12) :0x0

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.PUE(13..13) :0x0

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.PUS(14..15) :0x0

Select one out of next values for pad: SD1_DATA1

IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1.HYS(16..16) :0x0

Select one out of next values for pad: SD1_DATA1

root@imx6ulevk:~# ./memtool GPIO2.GDIR=0xffffffff

SOC: i.MX6UL

write 0xFFFFFFFF to 0x020A0004

root@imx6ulevk:~# ./memtool GPIO2.DR=0xffffffff

SOC: i.MX6UL

write 0xFFFFFFFF to 0x020A0000

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-114 (sysfs ) out lo

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

But still the UART2.RXD pin is low, as All pins Voltages on the Board interfaces: J1703, J1704, J1706 (except for the Power pins 3V/5V of course).

-> Notice that cat sys debug - pin114 is still LOW ??

note: I posted earlier, how I disabled interfaces: INET2, UART2, uSDhc1 .

-

echo 61 > /sys/class/gpio/export

echo "out" > /sys/class/gpio/gpio61/direction

echo 1 > /sys/class/gpio/gpio61/value

echo 62 > /sys/class/gpio/export

echo "out" > /sys/class/gpio/gpio62/direction

echo 1 > /sys/class/gpio/gpio62/value

echo 63 > /sys/class/gpio/export

echo "out" > /sys/class/gpio/gpio63/direction

echo 1 > /sys/class/gpio/gpio63/value

echo 64 > /sys/class/gpio/export

echo "out" > /sys/class/gpio/gpio64/direction

echo 1 > /sys/class/gpio/gpio64/value

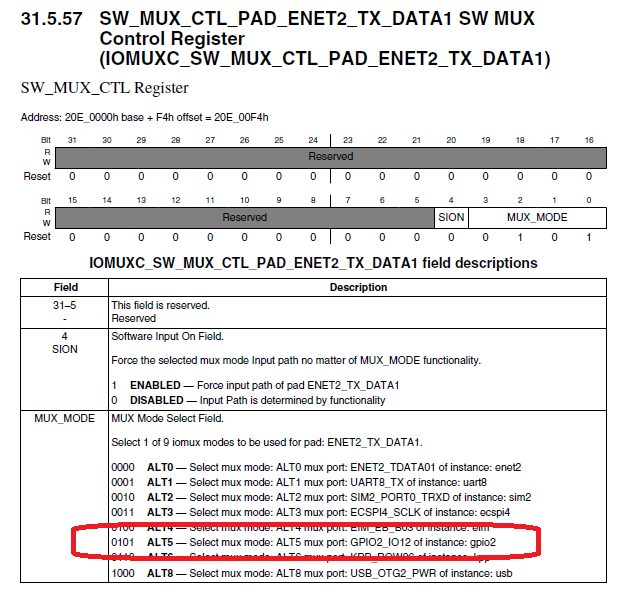

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_EN.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_CLK.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_DATA1.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_RX_ER.MUX_MODE=5

./memtool GPIO2.DR=0xffffffff

root@imx6ulevk:~# ./memtool GPIO2.GDIR

SOC: i.MX6UL

GPIO2 Addr:0x20a0000

GPIO2.GDIR Addr:0x020A0004 Value:0xE0000000 - GPIO_GDIR functions as direction control when the IOMUXC is in GPIO mode.

GPIO2.GDIR.GDIR(0..31) :0xe0000000

GPIO direction bits.

root@imx6ulevk:~# ./memtool GPIO2.GDIR=0xffffffff

SOC: i.MX6UL

write 0xFFFFFFFF to 0x020A0004

root@imx6ulevk:~# ./memtool GPIO2.GDIR

SOC: i.MX6UL

GPIO2 Addr:0x20a0000

GPIO2.GDIR Addr:0x020A0004 Value:0xFFFFFFFF - GPIO_GDIR functions as direction control when the IOMUXC is in GPIO mode.

GPIO2.GDIR.GDIR(0..31) :0xffffffff

GPIO direction bits.

root@imx6ulevk:~# ./memtool GPIO2.DR=0xffffffff

SOC: i.MX6UL

write 0xFFFFFFFF to 0x020A0000

root@imx6ulevk:~# ./memtool GPIO2.DR

SOC: i.MX6UL

GPIO2 Addr:0x20a0000

GPIO2.DR Addr:0x020A0000 Value:0xFFFFFFFF - The 32-bit GPIO_DR register stores data that is ready to be driven to the output lines.

GPIO2.DR.DR(0..31) :0xffffffff

Data bits.

Even here, the ENET2 pins on the Board are all just 0-volts.

I even disabled ENET PHY in the menuconfig.

Only GPIO19 works.

Maybe a Clock needs be Enabled for the GPIOs ?

I am using the UltraLite Board which supplies about a dozen GPIO pins in the center of the board.

But so far, I have not been able to Configure these Pins and use them, neither in a Program or from SysFs.

Can you finish your example,

and show how to swing IOMUXC.SW_PAD_CTL_PAD_SD1_DATA1 to a HI state on the output Pin ?

- Maybe there are some Processes (besides in the DataTree) running and accessing these Ports and Registers, that I need to Disable ??

- - like Uart2, Enet2, uSDhc1 ?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Still take GPIO19 as example for output, before the example for GPIO19 is input.

root@imx6ulevk:~# echo 19 > /sys/class/gpio/export

root@imx6ulevk:~# echo out > /sys/class/gpio/gpio19/direction

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

gpio-19 (sysfs ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

root@imx6ulevk:~# /unit_tests/memtool GPIO1.DR.DR

SOC: i.MX6UL

GPIO1 Addr:0x209c000

GPIO1.DR Addr:0x0209C000 Value:0xF0040318 - The 32-bit GPIO_DR register stores data that is ready to be driven to the output lines.

GPIO1.DR.DR(0..31) :0xf0040318

Data bits.

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio19/value

root@imx6ulevk:~# /unit_tests/memtool GPIO1.DR.DR

SOC: i.MX6UL

GPIO1 Addr:0x209c000

GPIO1.DR Addr:0x0209C000 Value:0xF00C0318 - The 32-bit GPIO_DR register stores data that is ready to be driven to the output lines.

GPIO1.DR.DR(0..31) :0xf00c0318

Data bits.

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

gpio-19 (sysfs ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

Using memtool can see the GPIO has been change, why it is not in the debug fs.

Cause it is out put, And it is a independent GPIO. need to loop back.

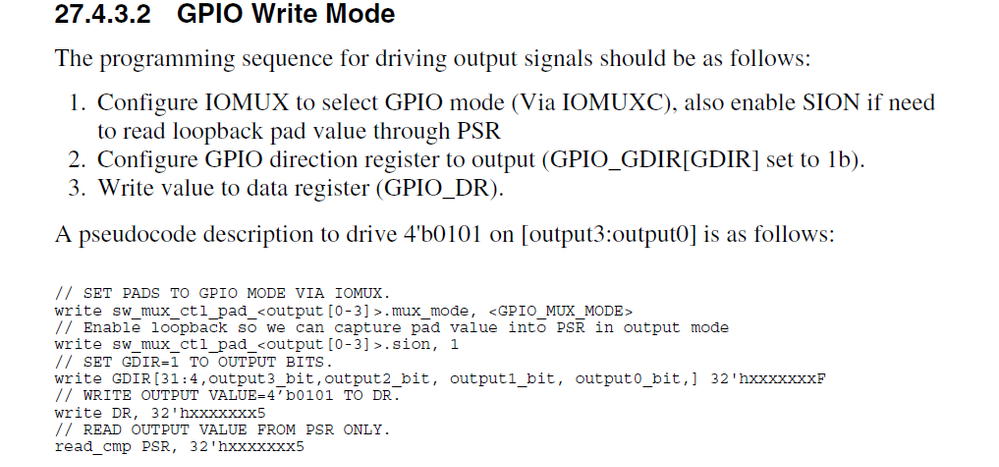

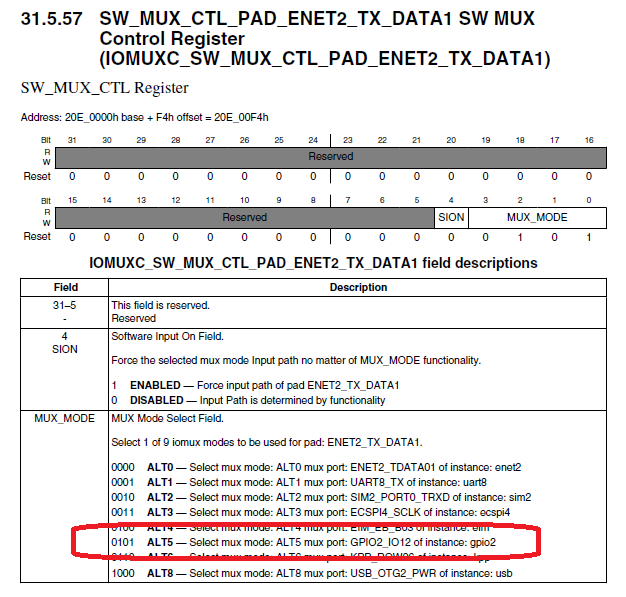

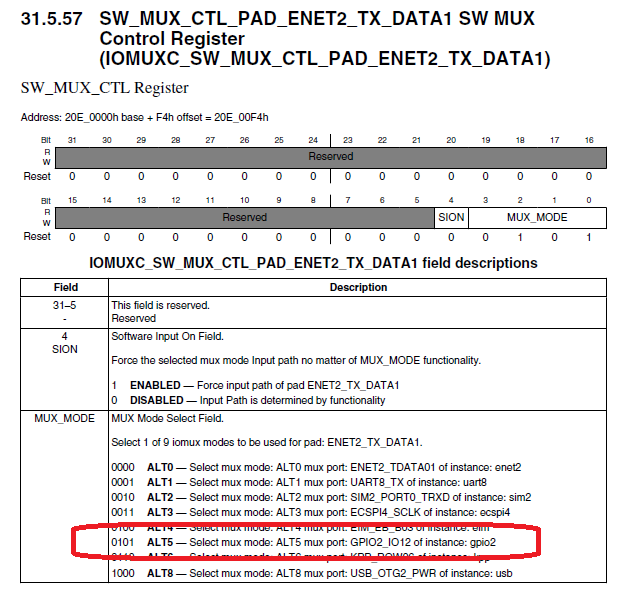

In the i.MX6 serials(i.MX6D/Q, i.MX6DL/Sole, i.MX6SX, i.MX6UL), it has bit call SION to set.

i.MX 6UltraLite Applications

Processor Reference Manual

Document Number: IMX6ULRM

Rev. 0, 08/2015

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B Addr:0x020E0090 Value:0x00000005 - SW_MUX_CTL Register

IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.MUX_MODE(0..3) :0x5

Select 1 of 9 iomux modes to be used for pad: UART1_RTS_B.

IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.SION(4..4) :0x0

Force the selected mux mode Input path no matter of MUX_MODE functionality.

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E0090

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B Addr:0x020E0090 Value:0x00000015 - SW_MUX_CTL Register

IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.MUX_MODE(0..3) :0x5

Select 1 of 9 iomux modes to be used for pad: UART1_RTS_B.

IOMUXC.SW_MUX_CTL_PAD_UART1_RTS_B.SION(4..4) :0x1

Force the selected mux mode Input path no matter of MUX_MODE functionality.

root@imx6ulevk:~# echo 0 > /sys/class/gpio/gpio19/value

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-19 (sysfs ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio19/value

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

gpio-19 (sysfs ) out hi

It is using the memtool to set the SION.

For add code, need to change the settings in the dts/imx6ul-pinfunc.h

But it just for loop back to linux system. here you can seen in the debugfs. It is not the madantory.

You can use the an oscilloscope or multimeter to confirm that signal.

The debugfs is just for debugging. For software to see the GPIO changes.

In the regular using, the value get/set is in the /sys/class/gpio.

Suggest don't set SION for output in programming.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

~#

echo 37 > /sys/class/gpio/export

echo 38 > /sys/class/gpio/export

echo 39 > /sys/class/gpio/export

echo 40 > /sys/class/gpio/export

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE=5

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_TX_DATA.MUX_MODE=5

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_CTS_B.MUX_MODE=5

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B.MUX_MODE=5

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RX_DATA.SION=1

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_TX_DATA.SION=1

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_CTS_B.SION=1

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B.SION=1

root@imx6ulevk:~# ./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00A0

root@imx6ulevk:~# ./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B

SOC: i.MX6UL

IOMUXC Addr:0x20e0000

IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B Addr:0x020E00A0 Value:0x00000015 - SW_MUX_CTL Register

IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B.MUX_MODE(0..3) :0x5

Select 1 of 9 iomux modes to be used for pad: UART2_RTS_B.

IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B.SION(4..4) :0x1

Force the selected mux mode Input path no matter of MUX_MODE functi

onality.

echo "out" > /sys/class/gpio/gpio37/direction

echo "out" > /sys/class/gpio/gpio38/direction

echo "out" > /sys/class/gpio/gpio39/direction

echo "out" > /sys/class/gpio/gpio40/direction

echo 1 > /sys/class/gpio/gpio37/value

echo 1 > /sys/class/gpio/gpio38/value

echo 1 > /sys/class/gpio/gpio39/value

echo 1 > /sys/class/gpio/gpio40/value

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-37 (sysfs ) out lo

gpio-38 (sysfs ) out lo

gpio-39 (sysfs ) out lo

gpio-40 (sysfs ) out lo

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

-

echo 61 > /sys/class/gpio/export

echo 62 > /sys/class/gpio/export

echo 63 > /sys/class/gpio/export

echo 64 > /sys/class/gpio/export

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_EN.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_CLK.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_DATA1.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_RX_ER.MUX_MODE=5

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_EN.SION=1

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_CLK.SION=1

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_TX_DATA1.SION=1

./memtool IOMUXC.SW_PAD_CTL_PAD_ENET2_RX_ER.SION=1

echo "out" > /sys/class/gpio/gpio61/direction

echo "out" > /sys/class/gpio/gpio62/direction

echo "out" > /sys/class/gpio/gpio63/direction

echo "out" > /sys/class/gpio/gpio64/direction

echo 1 > /sys/class/gpio/gpio61/value

echo 1 > /sys/class/gpio/gpio62/value

echo 1 > /sys/class/gpio/gpio63/value

echo 1 > /sys/class/gpio/gpio64/value

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-37 (sysfs ) out lo

gpio-38 (sysfs ) out hi

gpio-39 (sysfs ) out lo

gpio-40 (sysfs ) out lo

gpio-61 (sysfs ) out lo

gpio-62 (sysfs ) out lo

gpio-63 (sysfs ) out lo

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

gpio-64 (sysfs ) out lo

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

But still read 0-volts at all GPIO pins ENET_RER, TXEN, TXCLK, TXD1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE=5 root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E01C8

root@imx6ulevk:~#

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E01C8

root@imx6ulevk:~#

root@imx6ulevk:~#

root@imx6ulevk:~# echo 51 > /sys/class/gpio/export

root@imx6ulevk:~#

root@imx6ulevk:~# echo out > /sys/class/gpio/gpio51/direction

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

gpio-19 (2190000.usdhc cd ) in hi

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-51 (sysfs ) out lo

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

root@imx6ulevk:~#

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio51/value

root@imx6ulevk:~#

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

gpio-19 (2190000.usdhc cd ) in hi

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-51 (sysfs ) out hi

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

root@imx6ulevk:~#

/unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_DATA1.MUX_M ODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E00F4

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_DATA1.SION= 1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00F4

root@imx6ulevk:~#

root@imx6ulevk:~#

root@imx6ulevk:~# echo 44 > /sys/class/gpio/export

root@imx6ulevk:~#

root@imx6ulevk:~# echo out > /sys/class/gpio/gpio44/direction

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

gpio-19 (2190000.usdhc cd ) in hi

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44 (sysfs ) out lo

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

root@imx6ulevk:~#

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio44/value

root@imx6ulevk:~#

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

gpio-19 (2190000.usdhc cd ) in hi

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44 (sysfs ) out hi

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

root@imx6ulevk:~#

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay Biyong,

I can see the voltage changing on the SdCard CD pin (19).

But, I do NOT see the change for ENET2.TX_DATA1 pin - J1704.D13 pin (pin44).

Thanks for 1 pin usable, but what about the Development Pins ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have replied at 10:06 pm on 2015-12-20.

The test is for SD1_DATA1 and ENET2_TX_DATA1.

The changes for ENET2_TX_DATA1 are highlight in RED.

Copy and paste again, here

/unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_DATA1.MUX_M ODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E00F4

root@imx6ulevk:~# /unit_tests/memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_DATA1.SION= 1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00F4

root@imx6ulevk:~#

root@imx6ulevk:~#

root@imx6ulevk:~# echo 44 > /sys/class/gpio/export

root@imx6ulevk:~#

root@imx6ulevk:~# echo out > /sys/class/gpio/gpio44/direction

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

gpio-19 (2190000.usdhc cd ) in hi

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44 (sysfs ) out lo

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

root@imx6ulevk:~#

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio44/value

root@imx6ulevk:~#

root@imx6ulevk:~# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X- ) in hi

gpio-9 (VSD_3V3 ) out lo

gpio-19 (2190000.usdhc cd ) in hi

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44 (sysfs ) out hi

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-132 (headset detect ) in lo

gpio-135 (spi32766.0 ) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

root@imx6ulevk:~#

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes thanks Biyong,

I followed that and even tested it again now.

Serial Terminal outputs match yours.

* But the Multimeter shows No Voltage changes on the Board - all 0Volts.

I am using INet2.TxData1 = J1704.p6 on UltraLite EVB Board.

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_DATA1.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E00F4

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_DATA1.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00F4

echo 44 > /sys/class/gpio/export

echo out > /sys/class/gpio/gpio44/direction

cat /sys/kernel/debug/gpio

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44 (sysfs ) out lo

echo 1 > /sys/class/gpio/gpio44/value

cat /sys/kernel/debug/gpio

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44 (sysfs ) out hi

# but No Change on J1704.Enet2TxD1 Pin via VoltMeter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Below are my Tests, but none of this affected the pins on J1703 or J1704 Voltages.

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_EN.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E00F8

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_EN.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00F8

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_CLK.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E00FC

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_TX_CLK.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00FC

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_RX_ER.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E0100

./memtool IOMUXC.SW_MUX_CTL_PAD_ENET2_RX_ER.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E0100

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA0.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E01C4

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E01C8

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA2.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E01CC

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA3.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E01D0

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA0.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E01C4

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA1.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E01C8

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA2.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E01CC

./memtool IOMUXC.SW_MUX_CTL_PAD_SD1_DATA3.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E01D0

root@imx6ulevk:~# echo 61 > /sys/class/gpio/export

root@imx6ulevk:~# echo 62 > /sys/class/gpio/export

root@imx6ulevk:~# echo 63 > /sys/class/gpio/export

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio61/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio62/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio63/direction

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio61/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio62/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio63/value

root@imx6ulevk:~# echo 113 > /sys/class/gpio/export

root@imx6ulevk:~# echo 114 > /sys/class/gpio/export

root@imx6ulevk:~# echo 115 > /sys/class/gpio/export

root@imx6ulevk:~# echo 116 > /sys/class/gpio/export

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio113/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio114/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio115/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio116/direction

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio113/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio114/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio115/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio116/value

root@imx6ulevk:~# echo 50 > /sys/class/gpio/export

root@imx6ulevk:~# echo 52 > /sys/class/gpio/export

root@imx6ulevk:~# echo 53 > /sys/class/gpio/export

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio50/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio52/direction

root@imx6ulevk:~# echo out> /sys/class/gpio/gpio53/direction

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio50/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio52/value

root@imx6ulevk:~# echo 1 > /sys/class/gpio/gpio53/value

# cat /sys/kernel/debug/gpio

GPIOs 0-31, platform/209c000.gpio, 209c000.gpio:

gpio-3 (tsc_X-) inhi

gpio-9 (VSD_3V3 ) out lo

GPIOs 32-63, platform/20a0000.gpio, 20a0000.gpio:

gpio-44(sysfs ) out hi

gpio-50(sysfs ) out hi

gpio-51(sysfs ) out hi

gpio-52(sysfs ) out hi

gpio-53(sysfs ) out hi

gpio-54(sysfs ) inlo

gpio-61(sysfs ) out lo

gpio-62(sysfs ) out lo

gpio-63(sysfs ) out lo

GPIOs 64-95, platform/20a4000.gpio, 20a4000.gpio:

GPIOs 96-127, platform/20a8000.gpio, 20a8000.gpio:

gpio-113 (sysfs ) out lo

gpio-114 (sysfs ) out lo

gpio-115 (sysfs ) out lo

gpio-116 (sysfs ) out lo

gpio-119 (? ) out lo

GPIOs 128-159, platform/20ac000.gpio, 20ac000.gpio:

gpio-131 (? ) out lo

gpio-135 (spi32766.0) out lo

gpio-136 (? ) out lo

gpio-138 (spi4.14 ) out lo

gpio-139 (spi4.14 ) out lo

GPIOs 248-255, spi/spi32766.0, 74hc595, can sleep:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I measure from the R1731 for SD1_DATA1. It does take effect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

* * *

-> I had success with 3 pins, off of the J1703 bus, UART2 RX + TX + RTS.

UART2 / Pins need to be disabled in the imx6ul-14x14-evk.dts file also.

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RX_DATA.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E0098

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_TX_DATA.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E0094

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_CTS_B.MUX_MODE=5

SOC: i.MX6UL

write 0x00000005 to Bit 0..3 of 0x020E009C

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RX_DATA.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E0098

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_TX_DATA.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E0094

./memtool IOMUXC.SW_MUX_CTL_PAD_UART2_RTS_B.SION=1

SOC: i.MX6UL

write 0x00000001 to Bit 4..4 of 0x020E00A0

echo 20 > /sys/class/gpio/export

echo 21 > /sys/class/gpio/export

echo 25 > /sys/class/gpio/export

echo out> /sys/class/gpio/gpio20/direction

echo out> /sys/class/gpio/gpio21/direction

echo out> /sys/class/gpio/gpio25/direction

echo 1 > /sys/class/gpio/gpio20/value

echo 1 > /sys/class/gpio/gpio21/value

echo 1 > /sys/class/gpio/gpio25/value

echo 0 > /sys/class/gpio/gpio20/value

echo 0 > /sys/class/gpio/gpio21/value

echo 0 > /sys/class/gpio/gpio25/value

This will toggle Pins 1, 2, and 3 on J1703 bus.

Pin 3 RTS is OpenCollector so it needs a PullUp resistor.

Thanks for the help Biyong.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

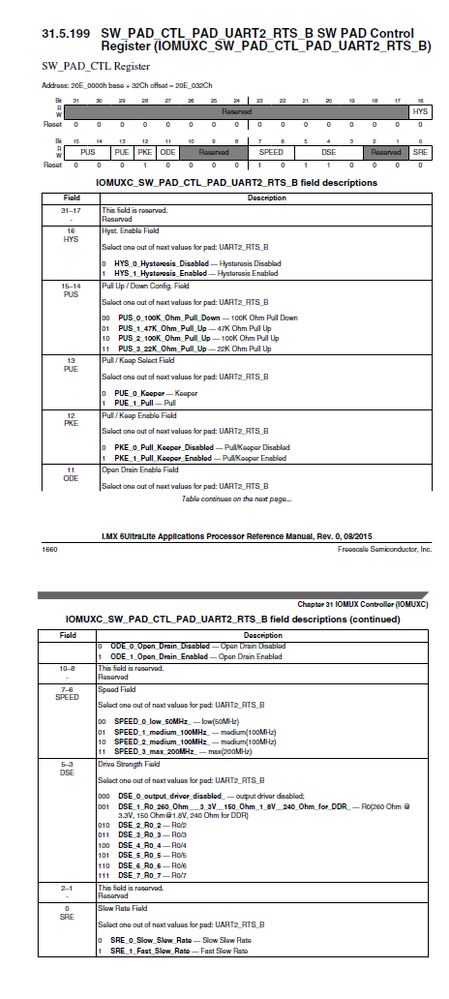

I don't know what is "OpenCollector" here for i.MX6UL RTS. Cause i.MX6 has no OC setting for a PAD. But it has OD setting.

In the IOMUX module, i.MX6 has software pad control, which can change the open drain to others including pull up.

Also you can change it in device tree or use the memtool to change it for test purpose.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much Biyong for such illustrative examples. They clarify many concepts for developers who still don't have a great knowledge in Linux which is exactly my situation. So thank you very much for your help!

I have gone through all your proposals for debugging and I have succeeded in all of them except for one important thing: I am unable to compile the device tree! and this is what I need for my board customization, since I cannot use debug tools for my board customization project.

This i what I try to do:

I modify imx6ul-evk-14x14.dts and save it with another name (imx6ul-evk-14x14-custom.dts) in the same directory, that is in:

/home/alvaro/yocto/fsl-release-bsp-ul/build-qt5/tmp/work-shared/imx6ulevk/kernel-source/arch/arm/boot/dts/imx6ul-evk-14x14-custom.dts

and execute from directory where dtc executable is:

./dtc /home/alvaro/yocto/fsl-release-bsp-ul/build-qt5/tmp/work-shared/imx6ulevk/kernel-source/arch/arm/boot/dts/imx6ul-evk-14x14-custom.dts

I get the following error:

Error: /home/alvaro/yocto/fsl-release-bsp-ul/build-qt5/tmp/work-shared/imx6ulevk/kernel-source/arch/arm/boot/dts/imx6ul-14x14-custom.dts:11.1-9 syntax error

FATAL ERROR: Unable to parse input tree

This also happens with the original file imx6ul-evk-14x14.dts, so that I guess it has nothing to do with the file modifications.

Do you have any idea of what might be happening?

Thank you in advance!

BR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The dtb compile depends on the linux kernel build.

Could not just use the dtc.

If you use the yocto, you could use bitbake linux-imx -c compile -f.

If you use standalone method,

ARCH=arm CROSS_COMPILE=/opt/poky/1.8/sysroots/x86_64-pokysdk-linux/usr/bin/arm-poky-linux-gnueabi/arm-poky-linux-gnueabi- make imx6ul-14x14-evk.dtb -C linux

Attached the dtb, which is for this test.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your indications Biyong! Sometimes it is complicated to get things working in embedded linux if you don't have some deep background as it is my case ... and this is why your detailed explanations are really welcome!

As I am using yocto, I have been able to modify the device tree and use it correctly as you suggested. This is what I have done, just in case anybody else might be interested:

modify the device tree file imx6ul-14x14-evk.dts at /tmp/work/imx6ulevk-poky-linux-gnueabi/linux-imx/3.14.38-r0/git/arch/arm/boot/dts/

from ~/yocto/fsl-release-bsp-ul/ execute source setup-environment build-qt5 as I have a fsl-image-qt5 image and decided to call the working directory "build-qt5"

from ~/yocto/fsl-release-bsp-ul/build-qt5/

compile the kernel and the device tree: bitbake linux-imx -c compile -f

deploy them: bitbake linux-imx -c deploy -f -> new files (kernel and dtb) are at /tmp/deploy/images/imx6ulevk/

copy these files and rename them into the boot partition of the sdcard.

I have just copied the dtb files, and it seems to be working ... is this enough? do I have to replace the zImage file also?

Regarding the dts file, in the given example to use sd1_cd as gpio, is it enough to comment the line cd-gpio=<&gpio1 19 0> or do I have to additionally define this pin as gpio in the device tree?

I guess that if it is not defined as part of the sd1, you can export it as gpio "by default" ... is this right? I have not defined it as gpio in the device tree and just by commenting it I have been able to export it.

As a next step, I would like to use ecspi4 port available at arduino expansion port ... any suggestion to begin with? I will let you know how it works.

Thank you in advance for your kind collaboration.

BR