- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

SD boot issue with i.MX6SL

Hi all

My customer have already built a custom board with i.MX6SL and they have a problem with SD boot.

Some of the board fail first boot but it can boot after second time.

They tried following things.

1.It can boot normally when they turn on the power with pressing the reset button

2.It can boot normally when they press the reset button after boot fail

Form the above, they guess it have some problem with reset and clock timing.

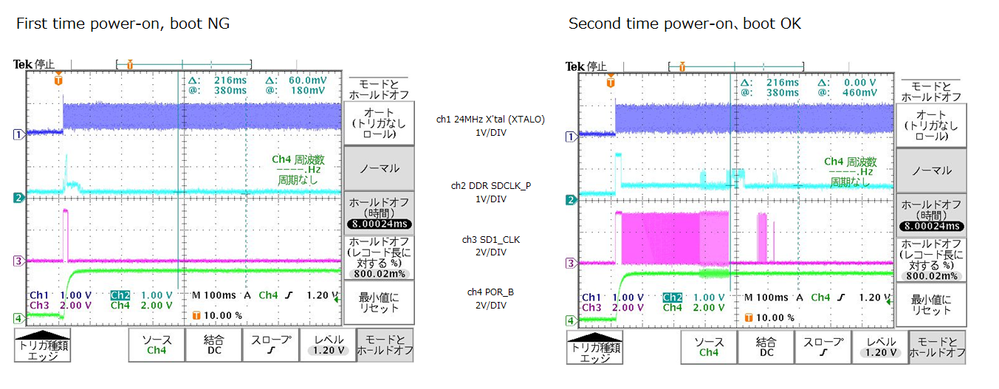

So they check the timing of POR_B and XTAL. (Please see a following picture.)

From the pictures, it seems that is has no problem with the timings.

Then, they checked the SD clock output to confirm the point of where the i.MX is stopped.

As a result, they confirm that the SD clock wasn't output.

From the results of the investigation, we guess that ERR007927 may cause this issue.

Is there a way to confirm that this errata is caused the issue ?

And do you have any idea to avoid this issue ?

Ko-hey

Hello,

For such issues, with non stable boot, it makes sense

check power up sequence.

Also, the erratum ERR007927 may take place, so, please

try workarounds for it.

Another point for consideration - DDR stress test can help

to find possible memory issues, assuming memory initialization

is the same for the test and customer’s applications.

i.MX6/7 DDR Stress Test Tool V2.52

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Yuri

Please see the attachment. It shows power up sequence.

Regarding workaround, they tried 1 to 3 workaround but there are no affect.

Let me confirm about workaround No.4 and No.5.

Those workaround can only do with adding a reset IC. Is my understanding correct ?

Is there any way to do it with SW change ?

Ko-hey