- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- RMII interface error on i.MX6Q

RMII interface error on i.MX6Q

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I have a custom hardware with i.MX6 Quad CPU. I would like to use its RMII interface to communicate with SMSC's LAN8720A PHY. Configuration, detection and communication seem to be right, but the problem is that all packets are received or transmitted by the PHY are totally wrong in fact. Below you can find an example ifconfig output, look at the statistics.

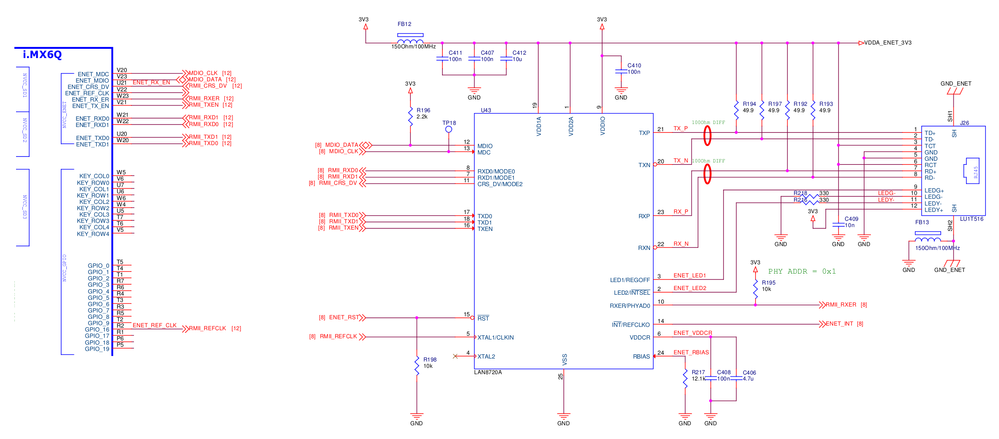

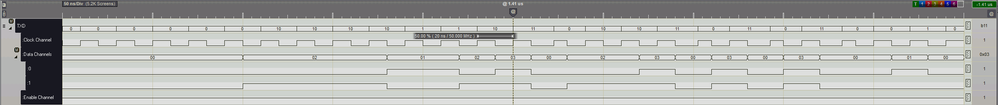

The connection is based on Freescale documentation: IMX6DQ6SDLHDG Rev 1 / Chapter 12.2. The part of schematic is attached. The system uses GPIO_16 pin to generate the reference clock. I measured the clock with frequency counter and is exact (<50ppm). The signal quality is a bit distorted, but is between LAN8720A's timing margins. I tried with different drive strengths, but none of them helped. An oscillogram is attached (in case of DSE=60Ohm). Anyway, I tried with external 50MHz clock on GPIO_16 with ENET_CLK_SEL:0, but same problem.

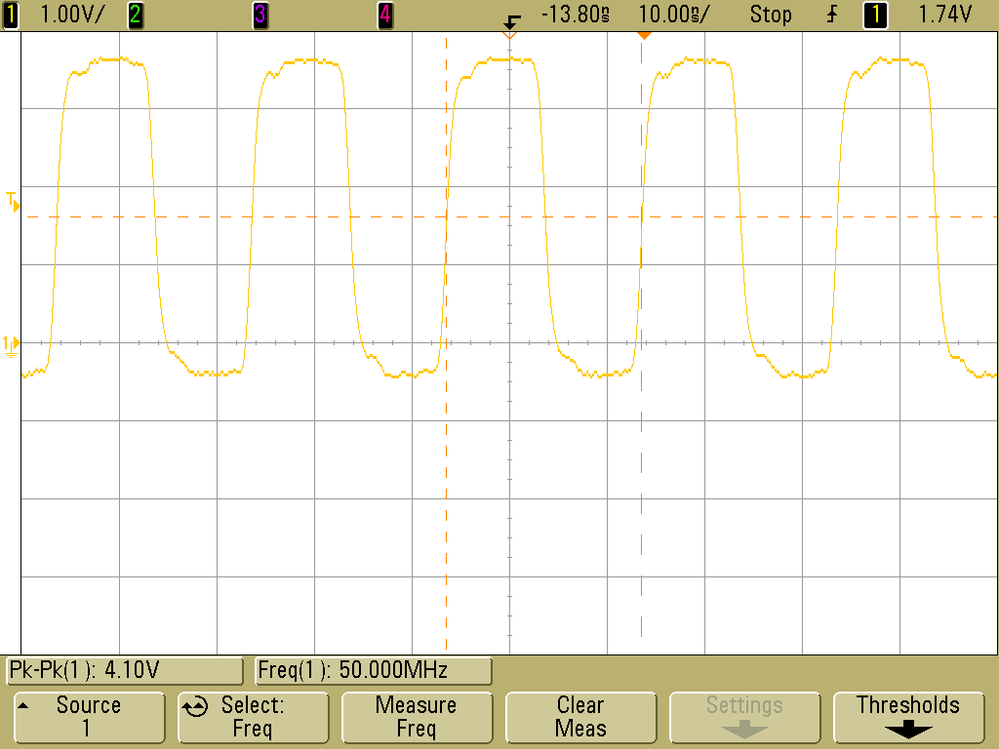

I observed the RMII lines with logic analyzer. It seems good to me, but I can't decode and interpret it.

RMII signals have 1410mils lengths, however REF_CLK has 1750mils.

I have already used LAN8720A with this connector successfully on another board, so physical part might not be the cause of error.

By the way, changing link's speed to 10Mbps does not help either.

Any help would be appreciated.

Best Regards,

Laszlo Timko

Tested software versions:

U-Boot: imx_v2015.04_3.14.52_1.1.0_ga

Linux: 3.14.28_1.0.0_ga and imx_3.14.52_1.1.0_ga and imx_4.1.15_1.0.0_ga

Device tree:

&fec {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet>;

phy-mode = "rmii";

phy-reset-gpios = <&gpio5 6 GPIO_ACTIVE_HIGH>;

phy-reset-duration = <2>;

status = "okay";

};

pinctrl_enet: enetgrp {

fsl,pins = <

MX6QDL_PAD_ENET_MDIO__ENET_MDIO 0x1b0a8

MX6QDL_PAD_ENET_MDC__ENET_MDC 0x1b0a8

MX6QDL_PAD_ENET_RXD0__ENET_RX_DATA0 0x1b0a8

MX6QDL_PAD_ENET_RXD1__ENET_RX_DATA1 0x1b0a8

MX6QDL_PAD_ENET_CRS_DV__ENET_RX_EN 0x1b0a8

MX6QDL_PAD_ENET_RX_ER__ENET_RX_ER 0x1b0a8

MX6QDL_PAD_ENET_TXD0__ENET_TX_DATA0 0x1b0a8

MX6QDL_PAD_ENET_TXD1__ENET_TX_DATA1 0x1b0a8

MX6QDL_PAD_ENET_TX_EN__ENET_TX_EN 0x1b0a8

MX6QDL_PAD_GPIO_16__ENET_REF_CLK 0x4001b0a1

MX6QDL_PAD_DISP0_DAT12__GPIO5_IO06 0x1b0b0 /* ENET_RST */

MX6QDL_PAD_DISP0_DAT11__GPIO5_IO05 0x1b0b0 /* ENET_INT */

>;

};

The changes made in kernel source to generate 50MHz clock:

linux-2.6-imx-rel_imx_3.14.28_1.0.0_ga/arch/arm/mach-imx/clk-imx6q.c:

@@ -568,8 +568,8 @@

imx_clk_prepare_enable(clk[IMX6QDL_CLK_USBPHY2_GATE]);

}

- /*Set enet_ref clock to 125M to supply for RGMII tx_clk */

- clk_set_rate(clk[IMX6QDL_CLK_ENET_REF], 125000000);

+ /*Set enet_ref clock to 50M to supply for RMII tx_clk */

+ clk_set_rate(clk[IMX6QDL_CLK_ENET_REF], 50000000);

#ifdef CONFIG_MX6_VPU_352M

/*

Register values verification:

IOMUXC_SW_PAD_CTL_PAD_GPIO16:

root@mx6obu:~# devmem2 0x20e0618 w

Value at address 0x20E0618 (0x76f90618): 0x1B0A1 (-> 60Ohm DSE, SRE)

IOMUXC_SW_MUX_CTL_PAD_GPIO16:

root@mx6obu:~# devmem2 0x20e0248 w

Value at address 0x20E0248 (0x76fc0248): 0x12 (-> SION, ALT2:ENET_REF_CLK)

IOMUX_ENET_REF_CLK_SELECT_INPUT:

root@mx6obu:~# devmem2 0x20e083C w

Value at address 0x20E083C (0x76f1983c): 0x1 (-> DAISY - GPIO16_ALT2)

IOMUXC_GPR1:

root@mx6obu:~# devmem2 0x20e0004

Value at address 0x20E0004 (0x76fdb004): 0x48693005 (-> ENET_CLK_SEL:1)

PHY related kernel boot log:

[ 1.260400] libphy: fec_enet_mii_bus: probed

[ 1.263863] fec 2188000.ethernet eth0: registered PHC device 0

[ 15.536851] fec 2188000.ethernet eth0: Freescale FEC PHY driver [SMSC LAN8710/LAN8720] (mii_bus:phy_addr=2188000.ethernet:01, irq=-1)

[ 15.548649] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

[ 19.696915] libphy: 2188000.ethernet:01 - Link is Up - 100/Full

[ 19.701573] IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

Ethernet info:

root@mx6obu:~# ethtool eth0

Settings for eth0:

Supported ports: [ TP MII ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: Yes

Advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Advertised pause frame use: Symmetric

Advertised auto-negotiation: Yes

Link partner advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Link partner advertised pause frame use: No

Link partner advertised auto-negotiation: Yes

Speed: 100Mb/s

Duplex: Full

Port: MII

PHYAD: 1

Transceiver: external

Auto-negotiation: on

Supports Wake-on: d

Wake-on: d

Link detected: yes

root@mx6obu:~# ifconfig eth0

eth0 Link encap:Ethernet HWaddr 00:40:95:36:35:33

inet addr:10.0.3.174 Bcast:10.0.3.255 Mask:255.255.252.0

inet6 addr: fe80::240:95ff:fe36:3533/64 Scope:Link

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:98 errors:98 dropped:26 overruns:0 frame:98

TX packets:76 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:28847 (28.1 KiB) TX bytes:6949 (6.7 KiB)

U-Boot log:

Net: eth_init: fec_probe(bd, -1, 1) @ 02188000

fec_mii_setspeed: mii_speed 0000001a

fec_mdio_read: phy: 01 reg:02 val:0x7

fec_mdio_read: phy: 01 reg:03 val:0xc0f1

fec_mii_setspeed: mii_speed 0000001a

fec_mdio_read: phy: 01 reg:00 val:0x3000

fec_mdio_write: phy: 01 reg:00 val:0xb000

fec_mdio_read: phy: 01 reg:00 val:0x3000

FEC connected to SMSC LAN8710/LAN8720

fec_mdio_read: phy: 01 reg:04 val:0x1e1

fec_mdio_read: phy: 01 reg:00 val:0x3000

FEC [PRIME]

=> ping 10.0.0.102

eth_halt: wait for stop regs

eth_halt: done

fec_mii_setspeed: mii_speed 0000001a

fec_open: fec_open(dev)

fec_mdio_read: phy: 01 reg:01 val:0x782d

fec_mdio_read: phy: 01 reg:01 val:0x782d

fec_mdio_read: phy: 01 reg:04 val:0x1e1

fec_mdio_read: phy: 01 reg:05 val:0x41e1

fec_open:Speed=100

Using FEC device

fec_send: status 0xc00 index 0 ret 0

fec_recv: ievent 0xc000000

fec_recv: status 0x8000

fec_recv: stop

fec_recv: ievent 0x0

fec_recv: status 0x8000

fec_recv: stop

fec_recv: ievent 0x0

fec_recv: status 0x8000

fec_recv: stop

fec_recv: ievent 0x0

fec_recv: status 0x8000

ARP Retry count exceeded; starting again

ARP Retry count exceeded; starting again

...

Part of schematic:

REF_CLK scope measurement:

Analyzer output sample (RMII_TXD):

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Finally, I have found the solution.

As can be seen in schematic, ENET_RXD0 is connected to RMII_RXD1, ENET_RXD1 to RMII_RXD0, ENET_TXD0 to RMII_TXD1 and ENET_TXD1 to RMII_TXD0. Ethernet instantly started to work when I fixed these lines.

Thank everyone for the help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Finally, I have found the solution.

As can be seen in schematic, ENET_RXD0 is connected to RMII_RXD1, ENET_RXD1 to RMII_RXD0, ENET_TXD0 to RMII_TXD1 and ENET_TXD1 to RMII_TXD0. Ethernet instantly started to work when I fixed these lines.

Thank everyone for the help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am still struggling with this problem and I am starting to run out of ideas. Is anyone using combination of i.MX6 Dual or Quad CPU with LAN8720 PHY and 3.14 or newer kernel successfully?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Laszlo Timko,

I have the same problem.

After I mark below line in file:arch/arm/mach-imx/clk-imx6q.c function:imx6q_clocks_init, it fix this problem.

clk_set_rate(clk[enet_ref], 125000000);

Hope it is useful for you.

Best Regards,

Frank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Laszlo Timko,

MX6QDL_PAD_GPIO_16__ENET_REF_CLK 0x1b0a1

...

IOMUXC_SW_MUX_CTL_PAD_GPIO16:

root@mx6obu:~# devmem2 0x20e0248 w

Value at address 0x20E0248 (0x76fc0248): 0x12 (-> SION, ALT2 - ENET_REF_CLK)

as far as I can see SION is not enabled in the gpio16 configuration, we use LAN8720A on SOLO and DUAL and in our case pin configured as here

| MX6QDL_PAD_GPIO_16__ENET_REF_CLK | 0x4001b0a8 |

Documentation/devicetree/bindings/pinctrl/fsl,imx-pinctrl.txt

SION(1 << 30): Software Input On Field.

Force the selected mux mode input path no matter of MUX_MODE functionality.

Alexander

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alexander,

Thank you so much for your advice.

However, as I see it, SION bit is indeed enabled:

0x12 -> 10010 -> 5th bit is 1

It has been activated in arch/arm/boot/dts/imx6q-pinfunc.h:

-#define MX6QDL_PAD_GPIO_16__ENET_REF_CLK 0x248 0x618 0x83c 0x2 0x1

+#define MX6QDL_PAD_GPIO_16__ENET_REF_CLK 0x248 0x618 0x83c 0x12 0x1

Anyway, I have tested with 0x4001b0a8 value too and did not help.

Regards,

Laszlo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please check Your configuration regarding recommendations in Chapter 9

(Porting the Ethernet Controller Driver) of "i.MX_6_BSP_Porting_Guide.pdf"

in Linux documentation.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Yuri,

Thanks for your reply, I didn't know documentation like this existed. That would certainly aid in the future, but it did not help to solve my ethernet problem.

It would be helpful to rule out software error, if someone confirmed that RMII interface actually works with 3.14 kernel.

Sincerely