- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Modifying the i.MX28 BSP for a different DDR2 Device and size

Modifying the i.MX28 BSP for a different DDR2 Device and size

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Modifying the i.MX28 BSP for a different DDR2 Device and size

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all,

I am hoping someone can help me with some changes to the i.MX28 WCE BSP to support a different memory size. I have read the two application notes that are available for the i.MX51 and i.MX25 but the code structure is slightly different so I want to make sure I get it right.

I have used the Freescale spreadsheet to make sure my DDR2 device has the correct register settings and timings. I have also modified xldr.c to reflect the necessary changes.

I am trying to modify the BSP to support a 256MB (2Gbit) single chip select DDR2 device (Micron MT47H128M16RT-25E) - the default BSP setting is for 128MB.

I am aware that I have to make changes to image_cfg.h, image_cfg.inc, config.bib, eboot.bib and oemaddrtab_cfg.inc to support the changes. I started with oemaddrtab_cfg.inc but I am unsure of how to modify this file.

g_oalAddressTable

DCD 0x90000000, 0x80000000, 1

DCD 0x90100000, 0x60000000, 1 ; SPI NOR flash

DCD 0x80000000, 0x40000000, 128 ; RAM image mapping

DCD 0x88000000, 0x00000000, 1 ; On-chip RAM

DCD 0x00000000, 0x00000000, 0 ; Terminate table

If I change the RAM Image mapping line to 256MB then this will occupy 0x80000000 to 0x8FFFFFFF. I will therefore nee do move the on-chip RAM location. If I move this to 0x900000000 then I will need to move the top two sections. The very top value appears to map to the internal registers of the i.MX28 (starting at the interrupt controller) on APBH.

How would I adjust the above table to support 256MB? Also what changes need to be made to the other files...?

Thank you, Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Its done.

Problem was different and stuck at different module but this is due to new RAM changes. Right now i disabled that particular module and device boot properly and also application working smoothly.

All above attached files are for 256 MB RAM support (MT47H128M16RT-25E_C)

I'll check all peripheral interfaces and update the result.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have cut and paste the relevant sections below. To send full files I would have to go over them all to ensure no proprietary content / comments in there.

Image_cfg.h:

#define IMAGE_BOOT_RAMDEV_RAM_SIZE (256*1024*1024) // 256 MB

Image_cfg.inc

IMAGE_BOOT_RAMDEV_RAM_SIZE EQU (256*1024*1024);; 256 MB

Config.bib

Set up based on your partitioning of OS region to RAM. We have 70MB reserved for our OS, it is copied from flash into this RAM area every boot:

IF IMGFLASH !

#define NK_START 80200000 ; 2MB (after reserved region)

IF IMGUUT

#define NK_SIZE 00700000 ; 7MB

ENDIF

IF IMGUUT !

#define NK_SIZE 04600000 ; 70MB

ENDIF

#define RAM_START 84800000 ; 72MB Offset

#define RAM_SIZE 0B800000 ; 184MB

ENDIF

We also need to adjust the mapping for OCRAM and NOR because we moved them in our modifications to the oem addr table:

OCRAM 90000000 00008000 RESERVED

...

; ------------------- FLASH image with/without EBOOT -------------------

; ROMSIZE = 0x04000000 (64 MB)

; ROMSTART = 0x90200000 (NOR virtual address base)

; ROMWIDTH = 32 (32-bit wide memory, entire image in one file)

; ----------------------------------------------------------------------

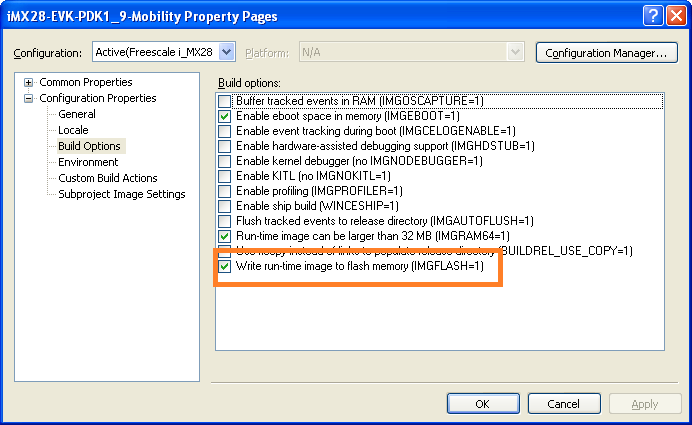

IF IMGFLASH

IF IMGEBOOT

ROMSIZE=03FC0000

ROMSTART=90240000

ENDIF

IF IMGEBOOT !

ROMSIZE=04000000

ROMSTART=90200000

ENDIF

ROMWIDTH=32

ENDIF

Eboot.bib - nothing to change here other than the comment at the to showing OS RAM size if you want it to reflect your 256MB.

Hope this helps. But check your DDR setup in xldr.c too. My notes just show the following changes. The ADDR_PINS one I originally missed so will still be 128MB without the additional address line.

HW_DRAM_CTL29 CS_MAP – 0xF in the original code, 0x1 from the spreadsheet. Determines which chip selects active based on bit for each available CS. If just using CS1 then 0x1 ok. 0xF enables all CS.

HW_DRAM_CTL29 ADDR_PINS – 0x1 Defines the difference between the maximum number of address pins configured (15) and the actual number of pins being used.

HW_DRAM_CTL42 TRAS_MAX – 0x36A6 (13990) in original code, 0x36B0 from spreadsheet (14000)

HW_DRAM_CTL43 TRFC – 0x1A (26) in original code, 0x27 (39) from spreadsheet. DRAM precharge time in cycles.

HW_DRAM_CTL45 TXSNR – 0x1C in original code, 0x29 in spreadsheet. As described above for tXSNR (because 2Gb not 1Gb).

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark,

IMO if below parameter set then only IF IMGFLASH case will be applicable so in your suggested code in config .bib both conditions IF IMGFLASH and IF IMGFLASH ! are considered. Can you please review it what you mentioned?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Mark for all details

But still something is missing and i could not able to load the image.

Here is log

BSP Clock Configuration:

PLL0 = 480000000 Hz

PLL1 = 480000000 Hz

PLL2 = 0 Hz

REF_CPU = 480000000 Hz

REF_EMI = 392727272 Hz

REF_IO0 = 480000000 Hz

REF_IO1 = 480000000 Hz

REF_PIX = 480000000 Hz

REF_HSADC = 480000000 Hz

REF_GPMI = 480000000 Hz

REF_PLL = 480000000 Hz

REF_XTAL = 24000000 Hz

REF_ENET_PLL= 0 Hz

P_CLK = 240000000 Hz

H_CLK = 120000000 Hz

X_CLk = 24000000 Hz

ETM = 24000000 Hz

EMI = 196363636 Hz

SSP0 = 24000000 Hz

SSP1 = 24000000 Hz

SSP2 = 24000000 Hz

SSP3 = 24000000 Hz

GPMI = 24000000 Hz

HSADC = 26666666 Hz

LCDIF = 24000000 Hz

SPDIF = 120000000 Hz

UTMI0 = 480000000 Hz

UTMI1 = 480000000 Hz

UART24MHZ = 24000000 Hz

PWM24MHZ = 24000000 Hz

TIMROT32K = 32000 Hz

Microsoft Windows CE Bootloader Common Library Version 1.4 Built Oct 1 2019 15:09:27

Microsoft Windows CE Ethernet Bootloader 1.0 for MX28 (Oct 1 2019 15:13:28)

reset GPMI module

enable bch module

NumberOfChip=1

NAND_ECCConfLayout, pagesize=4096,sisize=224

INFO: OEMPlatformInit: Initialized NAND flash device.

SD/MMC card is not found.

WARNING: OEMPlatformInit: Failed to initialize SDHC device.

INFO: Loading boot configuration from NAND

System ready!

Preparing for download...

INFO: Initial Eboot Screen Display...

EBOOT: DisplayInit++ :BSP_DISPLAY_43WVF1G-0

In Init backlight functionEBOOT: BLMenu...WaitSignal

Press [ENTER] to launch image stored in NAND flash or [SPACE] to cancel.

Initiating image launch in 0 seconds.

Launching flash image ...

-BLMenu .

INFO: Using device name: 'MX2843204'

INFO: Reading NK image from NAND (please wait)...

INFO: Valid image length is [0x1c13000]

INFO: Loading image is 100% completed.

INFO: Loading of NK completed successfully.

OEMLaunch called PhysAddress 0x40200000.

Download successful! Jumping to image at 0x0 (physical 0x40200000)...

BSP Clock Configuration:

PLL0 = 480000000 Hz

PLL1 = 480000000 Hz

PLL2 = 0 Hz

REF_CPU = 480000000 Hz

REF_EMI = 392727272 Hz

REF_IO0 = 480000000 Hz

REF_IO1 = 480000000 Hz

REF_PIX = 480000000 Hz

REF_HSADC = 480000000 Hz

REF_GPMI = 480000000 Hz

REF_PLL = 480000000 Hz

REF_XTAL = 24000000 Hz

REF_ENET_PLL= 0 Hz

P_CLK = 240000000 Hz

H_CLK = 120000000 Hz

X_CLk = 24000000 Hz

ETM = 24000000 Hz

EMI = 196363636 Hz

SSP0 = 24000000 Hz

SSP1 = 24000000 Hz

SSP2 = 24000000 Hz

SSP3 = 24000000 Hz

GPMI = 120000000 Hz

HSADC = 26666666 Hz

LCDIF = 24000000 Hz

SPDIF = 120000000 Hz

UTMI0 = 480000000 Hz

UTMI1 = 480000000 Hz

UART24MHZ = 24000000 Hz

PWM24MHZ = 24000000 Hz

TIMROT32K = 32000 Hz

Windows CE Kernel for ARM (Thumb Enabled) Built on Mar 8 2013 at 17:05:33

INFO:OALLogSetZones: dpCurSettings.ulZoneMask: 0xb

OALInitCpuHclkClock:Update CPU clock to 454MHz!

reset GPMI module

NumberOfChip=1

NAND_ECCConfLayout, pagesize=4096,sisize=224

INFO: Set NAND flash blocks [0x0 ~ 0x97] as reserved.

Stuck at above line and could not load the image

Few quires

We are using IF IMGFLASH ! so below patch is not applicable right?

IF IMGFLASH

IF IMGEBOOT

ROMSIZE=03FC0000

ROMSTART=90240000

ENDIF

IF IMGEBOOT !

ROMSIZE=04000000

ROMSTART=90200000

ENDIF

ROMWIDTH=32

ENDIF

My changes is exactly same as you mentioned but still could not load the image. Any other changes is required to make it for 256MB?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark

I had already go through this link https://community.nxp.com/thread/308734

So all DDR registers are modified as per excel provided in above link

Now i have same concern as mentioned by you i.e. g_oalAddressTable

So How did you manage first two entry in oemaddrtab_cfg.inc?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is our version. We have been using this since the original post.

g_oalAddressTable

DCD 0x80000000, 0x40000000, 256 ; RAM image mapping

DCD 0x90000000, 0x00000000, 1 ; On-chip RAM

DCD 0x90100000, 0x80000000, 1 ; Processor register space

DCD 0x90200000, 0x60000000, 1 ; SPI NOR flash

DCD 0x00000000, 0x00000000, 0 ; Terminate table

Is this the start of your project with the iMX28 or just an upgrade? If you are using the Windows CE BSP there are a number of bugs, a lot covered in my posts. If you are using NAND flash make sure you fix the really nasty one that can cause random pages to become corrupt!

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Mark

Now i can able to run boot loader properly but OS could not load. I suspect its due to config.bib. Could you please share changes of Image_cfg.h, Image_cfg.inc and Config.bib?

This is my changes

Image_cfg.h

// RAM image defines

#define IMAGE_BOOT_RAMDEV_RAM_PA_START (IMAGE_BOOT_RAM_PA_START)

#define IMAGE_BOOT_RAMDEV_RAM_SIZE (256*1024*1024) // 128 MB

#define IMAGE_BOOT_RAMDEV_RAM_PA_END (IMAGE_BOOT_RAMDEV_RAM_PA_START+IMAGE_BOOT_RAMDEV_RAM_SIZE-1)

Image_cfg.inc

; RAM image defines

IMAGE_BOOT_RAMDEV_RAM_PA_START EQU (0x40000000)

IMAGE_BOOT_RAMDEV_RAM_UA_START EQU (0xA0000000)

IMAGE_BOOT_RAMDEV_RAM_CA_START EQU (0x80000000)

IMAGE_BOOT_RAMDEV_RAM_SIZE EQU (256*1024*1024);; 128 MB

IMAGE_BOOT_RAMDEV_RAM_PA_END EQU (IMAGE_BOOT_RAMDEV_RAM_PA_START+IMAGE_BOOT_RAMDEV_RAM_SIZE-1)

Config.bib

IF IMGFLASH !

#define NK_START 80200000

IF IMGUUT

#define NK_SIZE 00300000 ;3MB

ENDIF

IF IMGUUT !

#define NK_SIZE 01E00000 ;30MB

ENDIF

#define RAM_START 82000000

#define RAM_SIZE 0E000000 //224MB (previous was 96MB for 128MB RAM)

ENDIF

NK $(NK_START) $(NK_SIZE) RAMIMAGE

RAM $(RAM_START) $(RAM_SIZE) RAM

OCRAM 90000000 00008000 RESERVED

This is just an upgrade to 256MB RAM. I have already ported WIndows CE 6.0 with 128MB RAM back in 2015. i bookmarked your thread back in 2016 regarding NANDFlash corruption issue and modified DMA_Wait() as per your suggestions

iMX28 NAND Flash ECC Layout BBI Swap

Just for confirmation please share entire updated function of DMA_Wait() from dma_utils.c

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I am away from the office at the moment so will try and dig out the source when I get back.

Note you should also consider xldr.c and the DDR2 setup. I believe I used a spreadsheet from one of the forum posts and there were a few changes when going to 256MB. Including refresh timings and the number of address lines.

These are all in register writes so easier to use the DDR setup spreadsheet and enter the values.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark,

Did you get any chance to check the source for 256MB changes?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

void DDR2EmiController_EDE1116_200MHz(void) { volatile UINT32* DRAM_REG = (volatile UINT32*) HW_DRAM_CTL00_ADDR; DRAM_REG[0] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_0(RW) DRAM_REG[1] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_1(RW) DRAM_REG[2] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_2(RW) DRAM_REG[3] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_3(RW) DRAM_REG[4] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_4(RW) DRAM_REG[5] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_5(RW) DRAM_REG[6] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_6(RW) DRAM_REG[7] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_7(RW) DRAM_REG[8] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_0(RD) DRAM_REG[9] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_1(RD) DRAM_REG[10] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_2(RD) DRAM_REG[11] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_3(RD) DRAM_REG[12] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_4(RD) DRAM_REG[13] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_5(RD) DRAM_REG[14] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_6(RD) DRAM_REG[15] = 0x00000000 ; //00000000000000000000000000000000 user_def_reg_ro_7(RD) DRAM_REG[16] = 0x00000000 ; //0000000_0 write_modereg(WR) 0000000_0 power_down(RW) 000000000000000_0 start(RW) DRAM_REG[17] = 0x00000100 ; //0000000_0 auto_refresh_mode(RW) 0000000_0 arefresh(WR) 0000000_1 enable_quick_srefresh(RW) 0000000_0 srefresh(RW+) DRAM_REG[18] = 0x00000000 ; //00000000000000000000000000000000 DRAM_REG[19] = 0x00000000 ; //00000000000000000000000000000000 DRAM_REG[20] = 0x00000000 ; //00000000000000000000000000000000 DRAM_REG[21] = 0x00000000 ; //00000_000 cke_delay(RW) 00000000 dll_lock(RD) 0000000_0 dlllockreg(RD) 0000000_0 dll_bypass_mode(RW) DRAM_REG[22] = 0x00000000 ; //000000000000_0000 lowpower_refresh_enable(RW) 000_00000 lowpower_control(RW) 000_00000 lowpower_auto_enable(RW) DRAM_REG[23] = 0x00000000 ; //0000000000000000 lowpower_internal_cnt(RW) 0000000000000000 lowpower_external_cnt(RW) DRAM_REG[24] = 0x00000000 ; //0000000000000000 lowpower_self_refresh_cnt(RW) 0000000000000000 lowpower_refresh_hold(RW) DRAM_REG[25] = 0x00000000 ; //00000000000000000000000000000000 lowpower_power_down_cnt(RW) DRAM_REG[26] = 0x00010101 ; //000000000000000_1 priority_en(RW) 0000000_1 addr_cmp_en(RW) 0000000_1 placement_en(RW) DRAM_REG[27] = 0x01010101 ; //0000000_1 swap_port_rw_same_en(RW) 0000000_1 swap_en(RW) 0000000_1 bank_split_en(RW) 0000000_1 rw_same_en(RW) DRAM_REG[28] = 0x000f0f01 ; //00000_000 q_fullness(RW) 0000_1111 age_count(RW) 0000_1111 command_age_count(RW) 0000000_1 active_aging(RW) DRAM_REG[29] = 0x0f02010a ; //0000_1111 cs_map(RW) 00000_010 column_size(RW) 00000_010 addr_pins(RW) 0000_1010 aprebit(RW) DRAM_REG[30] = 0x00000000 ; //0000000000000_000 max_cs_reg(RD) 0000_0000 max_row_reg(RD) 0000_0000 max_col_reg(RD) DRAM_REG[31] = 0x00010101 ; //000000000000000_1 eight_bank_mode(RW) 0000000_1 drive_dq_dqs(RW) 0000000_1 dqs_n_en(RW) DRAM_REG[32] = 0x00000100 ; //00000000000000000000000_1 reduc(RW) 0000000_0 reg_dimm_enable(RW) DRAM_REG[33] = 0x00000100 ; //00000000000000000000000_1 concurrentap(RW) 0000000_0 ap(RW) DRAM_REG[34] = 0x00000000 ; //0000000_0 writeinterp(RW) 0000000_0 intrptwritea(RW) 0000000_0 intrptreada(RW) 0000000_0 intrptapburst(RW) DRAM_REG[35] = 0x00000002 ; //000000000000000_0 pwrup_srefresh_exit(RW) 0000000_0 no_cmd_init(RW) 0000_0010 initaref(RW) DRAM_REG[36] = 0x01010000 ; //0000000_1 tref_enable(RW) 0000000_1 tras_lockout(RW) 000000000000000_0 fast_write(RW) DRAM_REG[37] = 0x07080403 ; //0000_0111 caslat_lin_gate(RW) 0000_1000 caslat_lin(RW) 00000_100 caslat(RW) 0000_0011 wrlat(RW) DRAM_REG[38] = 0x06005003 ; //000_00110 tdal(RW) 0000000001010000 tcpd(RW) 00000_011 tcke(RW) DRAM_REG[39] = 0x0a0000c8 ; //00_001010 tfaw(RW) 000000000000000011001000 tdll(RW) DRAM_REG[40] = 0x02009c40 ; //000_00010 tmrd(RW) 000000000111010100100010 tinit(RW) DRAM_REG[41] = 0x0002030c ; //0000000000000010 tpdex(RW) 00000011 trcd_int(RW) 00_001100 trc(RW) DRAM_REG[42] = 0x0036b009 ; //TRAKA 000000000011011010100110 tras_max(RW) 00001001 tras_min(RW) DRAM_REG[43] = 0x03270612 ; //TRAKA 0000_0011 trp(RW) 00011010 trfc(RW) 00_00011000010010 tref(RW) DRAM_REG[44] = 0x02030202 ; //0000_0010 twtr(RW) 000_00011 twr_int(RW) 00000_010 trtp(RW) 00000_010 trrd(RW) DRAM_REG[45] = 0x00c80029 ; //TRAKA 0000000011001000 txsr(RW) 0000000000011100 txsnr(RW) DRAM_REG[46] = 0x00000000 ; //00000000000000000000000000000000 DRAM_REG[47] = 0x00000000 ; //00000000000000000000000000000000 DRAM_REG[48] = 0x00012100 ; //0_0000000 axi0_current_bdw(RD) 0000000_1 axi0_bdw_ovflow(RW) 0_0100001 axi0_bdw(RW) 000000_00 axi0_fifo_type_reg(RW) //DRAM_REG[49] = 0x55550303 ; //0101010101010101 axi0_en_size_lt_width_instr(RW) 00000_011 axi0_w_priority(RW) 00000_011 axi0_r_priority(RW) DRAM_REG[49] = 0xffff0303 ; //0101010101010101 axi0_en_size_lt_width_instr(RW) 00000_011 axi0_w_priority(RW) 00000_011 axi0_r_priority(RW) DRAM_REG[50] = 0x00012100 ; //0_0000000 axi1_current_bdw(RD) 0000000_1 axi1_bdw_ovflow(RW) 0_0100001 axi1_bdw(RW) 000000_00 axi1_fifo_type_reg(RW) DRAM_REG[51] = 0xffff0303 ; //1111111100000000 axi1_en_size_lt_width_instr(RW) 00000_011 axi1_w_priority(RW) 00000_011 axi1_r_priority(RW) DRAM_REG[52] = 0x00012100 ; //0_0000000 axi2_current_bdw(RD) 0000000_1 axi2_bdw_ovflow(RW) 0_0100001 axi2_bdw(RW) 000000_00 axi2_fifo_type_reg(RW) DRAM_REG[53] = 0xffff0303 ; //0000000000000001 axi2_en_size_lt_width_instr(RW) 00000_011 axi2_w_priority(RW) 00000_011 axi2_r_priority(RW) DRAM_REG[54] = 0x00012100 ; //0_0000000 axi3_current_bdw(RD) 0000000_1 axi3_bdw_ovflow(RW) 0_0100001 axi3_bdw(RW) 000000_00 axi3_fifo_type_reg(RW) DRAM_REG[55] = 0xffff0303 ; //0000000000000001 axi3_en_size_lt_width_instr(RW) 00000_011 axi3_w_priority(RW) 00000_011 axi3_r_priority(RW) DRAM_REG[56] = 0x00000003 ; //00000000000000000000000000000_011 arb_cmd_q_threshold(RW) DRAM_REG[57] = 0x00000000 ; //00000000000000000000000000000000 DRAM_REG[58] = 0x00000000 ; //00000_00000000000 int_status(RD) 00000_00000000000 int_mask(RW) DRAM_REG[59] = 0x00000000 ; //00000000000000000000000000000000 out_of_range_addr(RD) DRAM_REG[60] = 0x00000000 ; //000000000000000000000000000000_00 DRAM_REG[61] = 0x00000000 ; //00_000000 out_of_range_type(RD) 0_0000000 out_of_range_length(RD) 000_0000000000000 out_of_range_source_id(RD) DRAM_REG[62] = 0x00000000 ; //00000000000000000000000000000000 port_cmd_error_addr(RD) DRAM_REG[63] = 0x00000000 ; //000000000000000000000000000000_00 DRAM_REG[64] = 0x00000000 ; //00000000000_0000000000000 port_cmd_error_id(RD) 0000_0000 port_cmd_error_type(RD) DRAM_REG[65] = 0x00000000 ; //00000000000_0000000000000 port_data_error_id(RD) 00000_000 port_data_error_type(RD) DRAM_REG[66] = 0x00000612 ; //000000000000_0000 tdfi_ctrlupd_min(RD) 00_00011000010010 tdfi_ctrlupd_max(RW) //DRAM_REG[67] = 0x01000002 ; //0000_0001 tdfi_dram_clk_enable(RW) 00000_000 tdfi_dram_clk_disable(RW) 0000_0000 dram_clk_disable(RW) 0000_0010 tdfi_ctrl_delay(RW) DRAM_REG[67] = 0x01000f02 ; //0000_0001 tdfi_dram_clk_enable(RW) 00000_000 tdfi_dram_clk_disable(RW) 0000_0000 dram_clk_disable(RW) 0000_0010 tdfi_ctrl_delay(RW) DRAM_REG[68] = 0x06120612 ; //00_00011000010010 tdfi_phyupd_type0(RW) 00_00011000010010 tdfi_phyupd_resp(RW) DRAM_REG[69] = 0x00000200 ; //00000000000000000000_0010 tdfi_phy_wrlat_base(RW) 0000_0000 tdfi_phy_wrlat(RD) DRAM_REG[70] = 0x00020007 ; //000000000000_0010 tdfi_rddata_en_base(RW) 0000_0000 tdfi_rddata_en(RD) 0000_0111 tdfi_phy_rdlat(RW) DRAM_REG[71] = 0xf4004a27; DRAM_REG[72] = 0xf4004a27; DRAM_REG[73] = 0xf4004a27; DRAM_REG[74] = 0xf4004a27; DRAM_REG[75] = 0x07000300 ; //00000111000000000000001100000000 phy_ctrl_reg_1_0(RW) DRAM_REG[76] = 0x07000300 ; //00000111000000000000001100000000 phy_ctrl_reg_1_1(RW) DRAM_REG[77] = 0x07400300 ; //00000111010000000000001100000000 phy_ctrl_reg_1_2(RW) DRAM_REG[78] = 0x07400300 ; //00000111010000000000001100000000 phy_ctrl_reg_1_3(RW) DRAM_REG[79] = 0x00000005 ; //00000000000000000000000000000101 phy_ctrl_reg_2(RW) DRAM_REG[80] = 0x00000000 ; //00000000000000000000000000000000 dft_ctrl_reg(RW) DRAM_REG[81] = 0x00000000 ; //0000000000000000000_00000 ocd_adjust_pup_cs_0(RW) 000_00000 ocd_adjust_pdn_cs_0(RW) DRAM_REG[82] = 0x01000000 ; //0000000_1 odt_alt_en(RW) 000000000000000000000000 DRAM_REG[83] = 0x01020408 ; //0000_0001 odt_rd_map_cs3(RW) 0000_0010 odt_rd_map_cs2(RW) 0000_0100 odt_rd_map_cs1(RW) 0000_1000 odt_rd_map_cs0(RW) DRAM_REG[84] = 0x08040201 ; //0000_1000 odt_wr_map_cs3(RW) 0000_0100 odt_wr_map_cs2(RW) 0000_0010 odt_wr_map_cs1(RW) 0000_0001 odt_wr_map_cs0(RW) DRAM_REG[85] = 0x000f1133 ; //00000000000011110001000100110011 pad_ctrl_reg_0(RW) DRAM_REG[86] = 0x00000000 ; //00000000000000000000000000000000 version(RD) DRAM_REG[87] = 0x00001f04; DRAM_REG[88] = 0x00001f04; DRAM_REG[89] = 0x00001f04; DRAM_REG[90] = 0x00001f04; DRAM_REG[91] = 0x00001f04; DRAM_REG[92] = 0x00001f04; DRAM_REG[93] = 0x00001f04; DRAM_REG[94] = 0x00001f04; DRAM_REG[95] = 0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_0_0(RD) DRAM_REG[96] = 0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_0_1(RD) DRAM_REG[97] = 0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_0_2(RD) DRAM_REG[98] = 0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_0_3(RD) DRAM_REG[99] = 0x00000000 ; //00000000000000000000000000000000 phy_obs_reg_0_0(RD) DRAM_REG[100] =0x00000000 ; //00000000000000000000000000000000 phy_obs_reg_0_1(RD) DRAM_REG[101] =0x00000000 ; //00000000000000000000000000000000 phy_obs_reg_0_2(RD) DRAM_REG[102] =0x00000000 ; //00000000000000000000000000000000 phy_obs_reg_0_3(RD) DRAM_REG[103] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_1_0(RD) DRAM_REG[104] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[105] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[106] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[107] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[108] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_1_1(RD) DRAM_REG[109] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[110] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[111] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[112] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[113] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_1_2(RD) DRAM_REG[114] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[115] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[116] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[117] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[118] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_1_3(RD) DRAM_REG[119] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[120] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[121] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[122] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[123] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_2_0(RD) DRAM_REG[124] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[125] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[126] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[127] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[128] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_2_1(RD) DRAM_REG[129] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[130] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[131] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[132] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[133] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_2_2(RD) DRAM_REG[134] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[135] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[136] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[137] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[138] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_2_3(RD) DRAM_REG[139] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[140] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[141] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[142] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[143] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_3_0(RD) DRAM_REG[144] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[145] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[146] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[147] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[148] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_3_1(RD) DRAM_REG[149] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[150] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[151] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[152] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[153] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_3_2(RD) DRAM_REG[154] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[155] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[156] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[157] =0x00000000 ; //00000000000000000000000_000000000 DRAM_REG[158] =0x00000000 ; //00000000000000000000000000000000 dll_obs_reg_3_3(RD) DRAM_REG[159] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[160] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[161] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[162] =0x00010000 ; //00000_000 w2r_samecs_dly(RW) 00000_001 w2r_diffcs_dly(RW) 0000000_000000000 DRAM_REG[163] =0x00030404 ; //00000000 dll_rst_adj_dly(RW) 0000_0011 wrlat_adj(RW) 0000_0100 rdlat_adj(RW) 0000_0100 dram_class(RW) DRAM_REG[164] =0x00000003 ; //00000000000000_0000000000 int_ack(WR) 00000011 tmod(RW) DRAM_REG[165] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[166] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[167] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[168] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[169] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[170] =0x00000000 ; //00000000000000000000000000000000 DRAM_REG[171] =0x01010000 ; //0000000_1 axi5_bdw_ovflow(RW) 0000000_1 axi4_bdw_ovflow(RW) 0000000000000000 dll_rst_delay(RW) DRAM_REG[172] =0x01000000 ; //0000000_1 resync_dll_per_aref_en(RW) 0000000_0 resync_dll(WR) 0000000_0 concurrentap_wr_only(RW) 0000000_0 cke_status(RD) DRAM_REG[173] =0x03030000 ; //00000_011 axi4_w_priority(RW) 00000_011 axi4_r_priority(RW) 000000_00 axi5_fifo_type_reg(RW) 000000_00 axi4_fifo_type_reg(RW) DRAM_REG[174] =0x00010303 ; //00000_000 r2r_samecs_dly(RW) 00000_001 r2r_diffcs_dly(RW) 00000_011 axi5_w_priority(RW) 00000_011 axi5_r_priority(RW) DRAM_REG[175] =0x01020202 ; //00000_001 w2w_diffcs_dly(RW) 00000_010 tbst_int_interval(RW) 00000_010 r2w_samecs_dly(RW) 00000_010 r2w_diffcs_dly(RW) DRAM_REG[176] =0x00000000 ; //0000_0000 add_odt_clk_sametype_diffcs(RW) 0000_0000 add_odt_clk_difftype_samecs(RW) 0000_0000 add_odt_clk_difftype_diffcs(RW) 00000_000 w2w_samecs_dly(RW) DRAM_REG[177] =0x02040303 ; //000_00010 tccd(RW) 0000_0100 trp_ab(RW) 0000_0011 cksrx(RW) 0000_0011 cksre(RW) DRAM_REG[178] =0x21002103 ; //0_0100001 axi5_bdw(RW) 0_0000000 axi4_current_bdw(RD) 0_0100001 axi4_bdw(RW) 000_00011 tckesr(RW) DRAM_REG[179] =0x00061200 ; //0000000000_00011000010010 tdfi_phyupd_type1(RW) 0_0000000 axi5_current_bdw(RD) DRAM_REG[180] =0x06120612 ; //00_00011000010010 tdfi_phyupd_type3(RW) 00_00011000010010 tdfi_phyupd_type2(RW) DRAM_REG[181] =0x04420442 ; //0_000010001000010 mr0_data_1(RW) 0_000010001000010 mr0_data_0(RW) DRAM_REG[182] =0x04420442 ; //0_000010001000010 mr0_data_3(RW) 0_000010001000010 mr0_data_2(RW) DRAM_REG[183] =0x00040004 ; //0_000000000000100 mr1_data_1(RW) 0_000000000000100 mr1_data_0(RW) DRAM_REG[184] =0x00040004 ; //0_000000000000100 mr1_data_3(RW) 0_000000000000100 mr1_data_2(RW) DRAM_REG[185] =0x00000000 ; //0_000000000000000 mr2_data_1(RW) 0_000000000000000 mr2_data_0(RW) DRAM_REG[186] =0x00000000 ; //0_000000000000000 mr2_data_3(RW) 0_000000000000000 mr2_data_2(RW) DRAM_REG[187] =0x00000000 ; //0_000000000000000 mr3_data_1(RW) 0_000000000000000 mr3_data_0(RW) DRAM_REG[188] =0x00000000 ; //0_000000000000000 mr3_data_3(RW) 0_000000000000000 mr3_data_2(RW) DRAM_REG[189] =0xffffffff ; //0000000000000001 axi5_en_size_lt_width_instr(RW) 0000000000000001 axi4_en_size_lt_width_instr(RW) }

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The above is the memory controller setup from our xldr.c file - I hope this helps. The formatting doesn't seem great above but hopefully you can copy/paste/compare to what you have. We left the function name the same as the original xldr.c

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark,

Did you get any chance to share Image_cfg.h, Image_cfg.inc, Config.bib, eboot.bib? It'll be really helpful who is working on 256 MB RAM support.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for sharing xldr.c.

Also share Image_cfg.h, Image_cfg.inc and Config.bib so i can compare my changes. Any changes in eboot.bib?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks

Yes i have already checked below thread and modified DDR registers as per excel sheet

https://community.nxp.com/thread/308734

I am using same part number of RAM as your mentioned MT47H1128M16RT-25E so if possible also share your xldr.c so i can compare my changes.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Deactivated user are you available to help on this case?