- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hello,

I am debugging our custom board that used i.MX 6Solo.

I want to keep GPIO port level from before reset until after reset.

For example, EIM_A17 has been set to high level before reset and I want to keep until after reset.

I tried by the warm reset(watchdog reset) that, but level is not keep.

Is i.MX6 can this behavior?

Best regards,

tomo

已解决! 转到解答。

Hi Tomo,

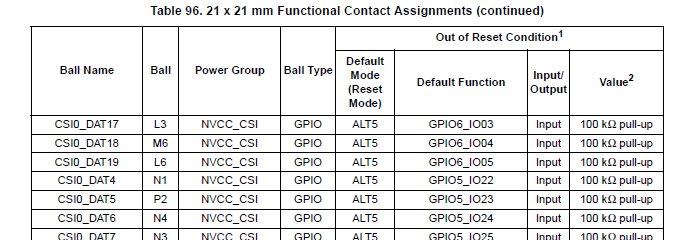

Unfortunately once a reset is applied the GPIO (IOMUX cells) reset to the state defined in the datasheet, in most cases this will be an input, taken from the datasheet table -

If you need a fixed high or low, you could use a pull resistor to set the level you need, but if you need to program a variable state and have that held during a reset sequence you will need to use an external latch to achieve this.

Regards

Ross

Hi Tomo,

Unfortunately once a reset is applied the GPIO (IOMUX cells) reset to the state defined in the datasheet, in most cases this will be an input, taken from the datasheet table -

If you need a fixed high or low, you could use a pull resistor to set the level you need, but if you need to program a variable state and have that held during a reset sequence you will need to use an external latch to achieve this.

Regards

Ross